Кінцевий автомат Мура

Модуль MOORE_1 ілюструє використання таблиці істинності для опису автомата Мура, граф переходів якого наведений на рис. 1.

SUBDESIGN MOORE_1

(

START, ABAR, CLK : INPUT;

WORK, END_WORK : OUTPUT;

)

VARIABLE

FSM : MACHINE WITH STATES

(UNIT, WORK, WAIT, FINISH, RESUME);

BEGIN

FSM.CLK = CLK;

FSM.RESET = ABAR;

TABLE

--поточний вхідний вихідний наступний

--стан сигнал сигнал стан

FSM, START => WORK, END_WORK, FSM;

UNIT, 0 => 0, 0, UNIT;

UNIT, 1 => 0, 0, WORK;

WORK, 0 => 1, 0, WAIT;

WORK, 1 => 1, 0, WORK;

WAIT, 0 => 1, 1, FINISH;

WAIT, 1 => 1, 1, RESUME;

RESUME, 0 => 0, 0, WAIT;

RESUME, 1 => 0, 0, WORK;

FINISH, B"x" => 0, 1, UNIT;

END TABLE;

END;

У наведеному описі задана внутрішня змінна FSM, що є символічним ім'ям кінцевого автомата, що має п'ять станів: INIT, WORK, WAIT, RESUM, FINISH. Відзначимо, що при її завданні зазначені тільки стани автомата.

Рівняння FSM.clk=CLK визначає з'єднання тактового сигналу з тактовим входом кінцевого автомата.

Вхід АВАР з'єднується із входом асинхронного скидання автомата. FSM.reset=ABAP.

Оскільки вхід дозволу роботи автомата FSM.ENA не використаний, то на нього автоматично подається логічний рівень, що не перешкоджає нормальній роботі автомата (тобто сигнал логічної одиниці).

У лівій частині таблиці істинності (ліворуч від знака =>) вказуються поточний стан автомата й набір вхідних сигналів. У правій частині - стан, у який автомат перейде з появою на вході CLK перепаду з 0 в 1, тобто стан переходу. І, крім того, перераховуються вихідні сигнали автомата. Оскільки даний автомат - це автомат Мура, то його вихідні сигнали залежать тільки від поточного стану й не залежать від вхідних сигналів.

Той же самий автомат може бути описаний за допомогою операторів CASE

SUBDESIGN MOORE_2

(

START, ABAR, CLK : INPUT;

WORK, END_WORK : OUTPUT;

)

VARIABLE

FSM : MACHINE WITH STATES

(INIT, WORK, WAIT, FINISH, RESUME);

BEGIN

FSM.(CLK,RESET) = (CLK,ABAR);

CASE FSM IS

WHEN INIT =>

IF START == 1

THEN

FSM = WORK;

ELSE

FSM = INIT;

END IF;

WHEN WORK =>

WORKING = VCC;

IF START == 1

THEN

FSM = WORK;

ELSE

FSM = WAIT;

END IF;

WHEN WAIT =>

WORKING = VCC;

END_WORKING = VCC;

IF START ==1

THEN

FSM = RESUME;

ELSE

FSM = FINISH;

END IF;

WHEN FINISH =>

END_WORKING =VCC;

FSM = INIT;

WHEN RESUME =>

IF START ==1

THEN

FSM = WORK;

ELSE

FSM = WAIT;

END IF;

END CASE;

END;

Відзначимо, що в даному описі значення вихідних сигналів WORK і END_WORK визначені не на всіх наборах аргументів. Оскільки немає явного задання їхніх базових значень, то, за замовчуванням, на тих наборах аргументів, на яких вони не були визначені, їм буде присвоєне значення логічного нуля.

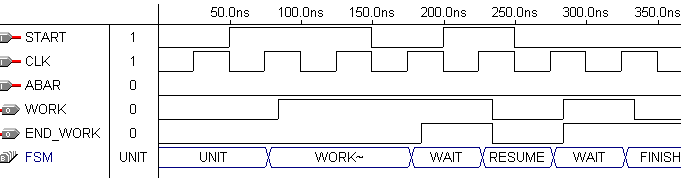

Результати моделювання автомата Мура наведені на рис. 4

Рис.4.

При реалізації модулів MOORE1 і M00RE2 на НВІС сімейства FLEX компілятор, кодує стани в такий спосіб (відомості взяті з файлу звіту - Report File):

FSM: MACHINE

OF BITS (

FSM~5,

FSM~4,

FSM~3,

FSM~2,

FSM~1

)

WITH STATES (

UNIT = B"00000",

WORK~ = B"11000",

WAIT = B"10100",

FINISH = B"10010",

RESUME = B"10001"

);

Таким чином, у цьому випадку використане кодування за принципом: один стан - один біт.

При реалізації зазначених модулів на НВІС сімейства МАХ і відключеної опції One Hot State Machine Encoding (команда Global Project Logic Synthesis меню Assign), тобто при реалізації двійкового кодування, для станів установлюються наступні коди (відомості взяті з файлу звіту — Report File):

FSM: MACHINE

OF BITS (

FSM~3,

FSM~2,

FSM~1

)

WITH STATES (

UNIT = B"000",

WORK~ = B"011",

WAIT = B"010",

FINISH = B"001",

RESUME = B"100"

);

Відмітимо, що стан, зазначений першим у списку станів автомата (WITH STATES (...)), при будь-якому способі кодування має код, що містить одні нулі. Тому з появою логічної одиниці на вході асинхронного скидання, автомат асинхронно перейде в стан, зазначений першим у списку станів (у даному прикладі - у стан INIT). Більше того, при включенні живлення всі тригери НВІС сімейств FLEX і МАХ установлюються, якщо явно не задане інше, у нульовий стан. Тому після включення живлення НВІС, автомат виявляється в тім стані, що у списку станів був зазначений першим.

Мова AHDL дозволяє задати значення вихідних сигналів уже при оголошенні автомата Мура. Дана можливість ілюструється на прикладі опису модуля MООRE3.

SUBDESIGN MOORE_3

(

START, ABAR, CLK :INPUT;

WORKING, END_WORKING : OUTPUT;

)

VARIABLE

FSM : MACHINE OF BITS (WORKING, END_WORKING)

WITH STATES

(INIT = B"00",

WORK = B"10",

WAIT = B"11",

FINISH=B"01",

RESUME=B"00");

BEGIN

FSM.(CLK,RESET) = (CLK,ABAR);

CASE FSM IS

WHEN INIT =>

IF START == 1

THEN

FSM = WORK;

ELSE

FSM = INIT;

END IF;

WHEN WORK =>

IF START == 1

THEN

FSM = WORK;

ELSE

FSM = WAIT;

END IF;

WHEN WAIT =>

IF START ==1

THEN

FSM = RESUME;

ELSE

FSM = FINISH;

END IF;

WHEN FINISH =>

FSM = INIT;

WHEN RESUME =>

IF START ==1

THEN

FSM = WORK;

ELSE

FSM = WAIT;

END IF;

END CASE;

END;

У цьому випадку при оголошенні автомата явно задані імена двох розрядів коду станів (Work, End_work), що є одночасно іменами вихідних сигналів. Крім того, явно зазначені їхні значення для кожного зі станів. Оскільки навіть при двійковому кодуванні двох розрядів недостатньо для кодування п'яти станів, то компілятор автоматично додасть відсутній розряд і здійснить перекодування станів, залишаючи без зміни значення заданих розрядів.

Оскільки явно задані значення розрядів у кодах станів компілятор не має права змінити, то він не може здійснити кодування за принципом: один стан - один біт.

Нижче представлені коди станів, установлені компілятором при реалізації модуля MООRE3 на НВІС сімейства FLEX (відомості взяті з файлу звіту - Report File):

FSM: MACHINE

OF BITS (

FSM~1,

WORKING~,

END_WORKING~

)

WITH STATES (

UNIT = B"000",

WORK = B"010",

WAIT = B"011",

FINISH = B"001",

RESUME = B"100"

);

Відзначимо, що вихідні сигнали в модулі MООRE3 є виходами тригерів блоку пам'яті автомата, і, отже, вони синхронізовані тактовим сигналом CLK.