Среднее Заочное отделение / 5 семестр / Курсовой ЦМПУ / 4 Раздел 1

.docx1 Описание принципа работы заданной структурной электрической схемы устройства сравнения двоичных чисел

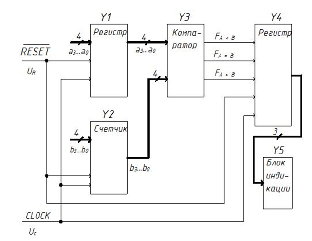

Структурная электрическая схема устройства сравнения двоичных чисел представлена на рисунке 1.

Рисунок 1 – Устройство сравнения двоичных чисел. Схема электрическая структурная

Рассмотрим назначение узлов, входящих в структурную схему устройства сравнения.

Компаратор Y3 предназначен для сравнения четырехразрядных двоичных чисел А и B, представленных разрядами a3…a0 и b3…b0. На выходах компаратора формируются сигналы, фиксирующие результат сравнения.

Регистр Y1 предназначен для параллельного ввода четырехразрядного операнда A в двоичной СС, значение которого может меняться в пределах от 0 до F в шестнадцатеричной СС.

Счетчик Y2 предназначен для параллельного ввода операнда B в двоичной СС, значение которого также может меняться от 0 до F.

Регистр Y4 предназначен для фиксации результата сравнения, который представляет собой трехразрядное слово.

Блок индикации Y5 предназначен для индикации результата сравнения с помощью светодиодных индикаторов.

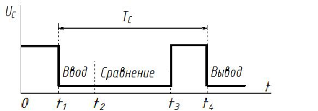

Работа устройства синхронизируется тактовыми импульсами Uс. Процесс функционирования устройства поясняется временной диаграммой, которая представлена на рисунке 2.

Рисунок 2 – Временная диаграмма, поясняющая процесс функционирования устройства сравнения

В момент времени t1 по отрицательному фронту тактового импульса (рисунок 2) начинается ввод операндов А и В в регистр Y1 и счетчик Y2 (рисунок 1). К моменту времени t2 ввод заканчивается, и начинается процесс сравнения в компараторе. Этот процесс в худшем случае завершается к моменту времени t3. Затем по положительному фронту тактового импульса результат сравнения фиксируется в регистре Y4 и одновременно поступает в блок индикации Y5. Например, при сравнении равных операндов A = B = 1011(2) на выходе FA = B компаратора Y3 вырабатывается единичный сигнал, а на выходах FA < B и FA > B вырабатываются нулевые сигналы.