Среднее Заочное отделение / 4 семестр / Цифровые и микропроцессорные устройства / Электронный конспект лекций (ЦиМПУ)

.pdf

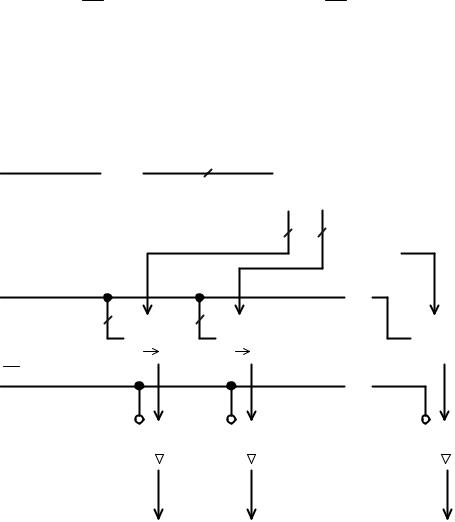

плексирования, но и функции изменения направления передачи данных под воздействием сигнала R/W .

A |

n-k |

|

|

|

|

|

|

|

|

|

|

1 |

DC |

|

n-k |

|

|

|

|

|

|

|

|

|

|

2 |

Матрица |

|

|

|

|||||

|

|

X |

|

|

|

|

|||||

|

|

|

|

|

2 |

n-k |

× m2 |

k |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

m2 |

k |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CS |

|

|

|

|

|

|

|

|

|

|

|

R/W |

|

|

|

|

|

|

|

|

|

|

|

DI |

|

m |

|

|

Буферы данных |

m |

DO |

||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

BD |

|

|

|

|

|

|

DC |

2 |

k |

A |

Y |

|

|

k |

|

|

|

2 |

|

|

Рисунок 3.36 – Структура ЗУ типа 2DM для RAM

3.6.4 Кэш-память

Кэш-память запоминает копии информации, передаваемой между устройствами (прежде всего между процессором и основной памятью). Она имеет небольшую емкость в сравнении с основной памятью и более высокое быстродействие (реализуется на триггерных элементах памяти).

При чтении данных сначала выполняется обращение к Кэш-памяти (рисунок 3.37). Если в КЭШе имеется копия данных, адресованной ячейки основной памяти, то КЭШ вырабатывает сигнал Hit (попадание) и выдает данные на общую шину данных. В противном случае сигнал Hit не вырабатывается, и выполняется чтение из основной памяти и одновременное помещение считанных данных в КЭШ.

Адрес n |

n |

|

Данные |

m |

CPU |

|

RAM |

|

|

|

|

|

m |

Hit |

|

|

|

|

|

|

|

|

CACHE |

|

|

|

n |

Tag |

m |

|

|

|

|

|

Данные |

|

m |

|

Данные |

|

|

|

||

Рисунок 3.37 – Структура Кэш-памяти

292

Эффективность кэширования обуславливается тем, что большинство прикладных программ имеют циклический характер и многократно используют одни и те же данные. Поэтому после первого использования данных из относительно медленной основной памяти повторные обращения требуют меньше времени. К тому же при использовании процессором Кэш-памяти основная память освобождается, и могут выполняться регенерация данных в динамическом ЗУ или использование памяти другими устройствами.

Объем Кэш-памяти много меньше емкости основной памяти, и любая единица информации, помещаемая в КЭШ, должна сопровождаться дополнительными данными (тегом), определяющими копией содержания, какой ячейки основной памяти является эта единица информации.

В полностью ассоциативной Кэш-памяти FACM (от англ. Fully Associated Cache Memory), структура которой показана на рисунке 3.38, каждая ячейка хранит данные, а в поле «тег» – полный физический адрес информации, копия которой записана. При любых обменах физический адрес запрашиваемой информации сравнивается с полями «тег» всех ячеек, и при совпадении их в любой ячейке устанавливается сигнал Hit. При чтении и значении сигнала Hit = 1 данные выдаются на шину данных, если же совпадений нет (Hit = 0), то при чтении из основной памяти данные вместе с адресом помещаются в свободную или наиболее давно не используемую ячейку Кэш-памяти.

При записи данные вместе с адресом сначала, как правило, размещаются в Кэш-памяти (в обнаруженную ячейку памяти при Hit = 1 и свободную при Hit = 0). Копирование данных в основную память выполняется под управлением специального контроллера, когда нет обращений к памяти.

Теговый адрес |

|

|

|

Тег |

|

|

Данные |

n |

|

|

m |

|

|

Шина данных |

|

|

|

|

|

n |

= |

= |

Буфер |

|

|

||

|

|

|

|

|

|

|

m |

|

|

|

m |

|

|

|

1 Hit |

... |

|

|

... |

|

|

|

... |

|

|

|

... |

Тег |

|

|

Данные |

n |

|

|

m |

|

|

|

|

n |

= |

= |

Буфер |

|

|

||

|

|

|

|

|

|

|

m |

Рисунок 3.38 – Структура полностью ассоциативной Кэш-памяти

293

Память типа FACM является весьма сложным устройством и используется только при малых емкостях. В то же время этот вид Кэш-памяти обеспечивает наибольшую функциональную гибкость и бесконфликтность адресов, так как любую единицу информации можно загрузить в любую ячейку Кэш-памяти.

Сложность FACM заставляет искать иные структуры Кэш-памяти, более экономичные по затратам аппаратных средств на их реализацию. К числу таких структур относятся Кэш-память с прямым размещением и Кэш-память с набор- но-ассоциативной архитектурой (с ассоциацией по нескольким направлениям).

3.6.5 Запоминающие элементы оперативных ЗУ

Статические ОЗУ (SRAM), как правило, имеют структуру 2DM, часть их при небольшой информационной емкости строится по структуре 2D.

Запоминающими элементами (ЗЭ) статических ОЗУ служат триггеры с цепями установки и сброса. В последнее время наиболее интенсивно развиваются статические ОЗУ, выполненные по схемотехнике КМОП, которые имеют сверхмалую потребляемую мощность в режиме хранения, высокую помехоустойчивость, повышенную емкость и высокое быстродействие (быстродействие повышается по мере уменьшения топологических норм технологического процесса).

Рассмотрим принципиальную схему ЗЭ на КМОП-транзисторах, который можно использовать в оперативных ЗУ со словарной организацией (рисунок

3.39).

ЗЭ на КМОП-транзисторах (рисунок 3.39) представляет собой RS-триггер на транзисторах VT1…VT4 с ключами выборки на транзисторах VT5 и VT6. При обращении к заданному ЗЭ появляется высокий уровень напряжения на адресной линии, который открывает ключи выборки (адресные ключи) по всей строке накопителя, и выходы триггеров соединяются со столбцовыми разрядными линиями считывания-записи. Через эти линии можно считывать состояние триггера (штриховыми линиями показан дифференциальный усилитель считывания), через них же можно записывать данные в триггер, подавая уровень логического нуля на ту или иную линию.

294

|

К другим цепям |

U |

VD1 |

|

|

п |

|

+ |

|

Uрез |

VD2 |

+ |

|

Накопитель ЗУ

Рисунок 3.40 – Схема подключения резервного источника питания к накопителю ЗУ

Вэтой схеме напряжение резервного источника несколько ниже напряжения основного источника UИП. В рабочем режиме накопитель питается от напряжения UИП, при этом диод VD1 проводит, а диод VD2 заперт. При снижении рабочего напряжения к накопителю автоматически подключается источник резервного питания. При этом проводит диод VD2, а диод VD1 запирается, так как при малых значения UИП он попадает под обратное смещение.

Для повышения надежности работы МПС нарушение нормальной работы источника питания обнаруживается контролем напряжения переменного тока.

Вдинамических ОЗУ (DRAM) данные хранятся в виде зарядов емкостей МОП-структур, и основой ЗЭ является просто конденсатор небольшой емкости. Такой ЗЭ значительно проще триггерного, содержащего 6 транзисторов, что обеспечивает динамическим ОЗУ в 4…5 раз большую емкость.

Известны конденсаторные ЗЭ разной сложности. В последнее время применяют однотранзисторные ЗЭ – лидеры компактности (рисунок 3.41).

ЛЗС (Линия записи-считывания) |

||

VT |

C |

3 |

|

||

Адресная линия (АЛ)

Рисунок 3.41 – Принципиальная схема ЗЭ динамического ОЗУ

Ключевой транзистор VT отключает запоминающий конденсатор CЗ от линии записи-считывания или подключает его к ней. Сток транзистора VT не

296

вается единица или ноль. Неравенство напряжений в точках A и B вносит несимметрию проводимостей транзисторов VT1 и VT2. Для считывания и регенерации данных сигнал «Подготовка» переводится на высокий уровень. Транзисторы VTН1 и VTН2 открываются, и возникает схема триггера, находящегося в неустойчивом состоянии, близком к симметричному. Такой триггер в силу своих свойств быстро перейдет в устойчивое состояние, предопределенное начальной несимметрией его режима. На выходах триггера сформируются полные напряжения высокого и низкого уровней. Так как одни и те же точки A и B являются одновременно и входами и выходами усилителя-регенератора, после своего срабатывания он восстанавливает на емкости CЗ полное значение считанного сигнала. Тем самым автоматически осуществляется регенерация данных в ЗЭ. Состояние триггера определяет также сигналы, выводимые во внешние цепи в качестве считанной информации.

ЛЗСА |

VT |

|

|

|

Подготовка |

|

|

|

|

|

|

||

|

C3 |

|

|

|

|

Uп |

|

|

|

|

n |

n |

|

|

|

|

|

VTН1 |

|

VTН2 |

CЛ/2 |

АЛ |

|

|

A |

|

B |

|

|

|

|

|

||

А |

Усилитель- |

В |

|

VT1 |

|

VT2 |

|

регенератор |

|

CЛ/2 |

|

||

|

|

|

|

|

а) |

ЛЗСВ |

б) |

|

||

|

|

Рисунок 3.42 – Схема включения усилителя-регенератора в разрыв линии записисчитывания динамического ЗУ (а) и вариант схемной реализации усилителя-регенератора (б)

Особенностью динамических ЗУ является мультиплексирование шины адреса. Адрес делится на два полуадреса, один из которых представляет собою адрес строки, а другой – адрес столбца матрицы ЗЭ. Полуадреса подаются на одни и те же выводы корпуса ИС поочередно. Подача адреса строки сопровождается соответствующим стробом RAS (от англ. Row Address Strobe), а адреса столбца – стробом CAS (от англ. Column Address Strobe). Причиной мультиплексирования адресов служит стремление уменьшить число выводов корпуса ИС и тем самым удешевить ее, а также то обстоятельство, что полуадреса и сигналы RAS и CAS в некоторых режимах и схемах используются различно

298

(например, в режимах регенерации адрес столбца вообще не нужен). Сокращение числа внешних выводов корпуса для динамических ЗУ особенно актуально, так как они имеют максимальную емкость и, следовательно, большую разрядность адресов. Например, ЗУ с организацией 16 M 1 имеет 24-разрядный адрес, а мультиплексирование сократит число адресных линий на 12.

3.6.6 Запоминающие элементы постоянных ЗУ

Программирование постоянной памяти заключается в том или ином размещении элементов связи между горизонтальными и вертикальными линиями матрицы запоминающих элементов. Запоминающие устройства типа ROM имеют многоразрядную организацию (чаще всего 8-разрядную или 4- разрядную, для некоторых ИС 16-разрядную) и обычно выполняются по структуре 2DM. Простейшие ПЗУ могут иметь структуру 2D. Технологии изготовления постоянных ЗУ разнообразны: ТТЛ(Ш), КМОП, n-МОП и др.

Вмасочных ПЗУ элементом связи могут быть диоды, биполярные транзисторы, МОП-транзисторы и т. д. Например, в матрице диодного ROM(M) (рисунок 3.43) горизонтальные линии являются линиями выборки слов (адресными линями – АЛ), а вертикальные – линиями считывания (разрядными линиями – РЛ). Считываемое слово определяется расположением диодов в узлах координатной сетки. При наличии диода высокий потенциал выбранной горизонтальной линии передается на соответствующую вертикальную линию, и в данном разряде слова появляется сигнал логической единицы. При отсутствии диода потенциал близок к нулевому, так как вертикальная линия через резистор связана с землей. В изображенной матрице при возбуждении линии выборки АЛ1 считывается слово 11010001 (это слово хранится в ячейке № 1). При возбуждении АЛ2 считывается слово 10101011 (оно хранится в ячейке № 2). Шины выборки являются выходами дешифратора адреса, каждая адресная комбинация возбуждает свой выход дешифратора, что приводит к считыванию слова из адресуемой ячейки.

Вматрице с диодными элементами в одних узлах матрицы диоды изготавливаются, в других – нет. При этом, чтобы удешевить производство, при изготовлении ПЗУ стремятся варьировать только один шаблон, так чтобы одни элементы связи были законченными и работоспособными, а другие – незавершенными и как бы отсутствующими. Для матриц с МОП-транзисторами часто в МОП-транзисторах, соответствующих хранению нуля, увеличивают толщину подзатворного окисла, что ведет к увеличению порогового напряжения транзистора. В этом случае рабочие напряжения ПЗУ не в состоянии открыть транзистор. Постоянно закрытое состояние транзистора аналогично его отсутствию.

299

АЛ1

АЛ2

|

... ... ... ... ... ... ... ... |

|||||||

АЛn |

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

Рисунок 3.43 – Матрица диодных запоминающих элементов масочного ПЗУ

ПЗУ с масочным программированием отличаются компактностью запоминающих элементов и, следовательно, высоким уровнем интеграции. При больших объемах производства масочное программирование предпочтительно, однако при недостаточной тиражности ПЗУ затраты на проектирование и изготовление шаблона для их технологического программирования окажутся чрезмерно высокими. Отсюда видна и область применения масочных ПЗУ – хранение стандартной информации, имеющей широкий круг потребителей. В частности, масочные ПЗУ имеют в качестве «прошивки»1) коды букв алфавитов (русского и латинского), таблицы типовых функций (синуса, квадратичной функции и др.), стандартное программное обеспечение и т. п.

ВПЗУ типа PROM микросхемы программируются устранением или созданием специальных перемычек. В исходной заготовке имеются (или отсутствуют) все перемычки. После программирования остаются или возникают только необходимые.

Устранение части перемычек свойственно ПЗУ с плавкими перемычками (типа fuse – предохранитель). При этом в исходном состоянии ПЗУ имеет все перемычки, а при программировании часть их ликвидируется путем расплавления импульсами тока достаточно большой амплитуды и длительности.

ВПЗУ с плавкими перемычками эти перемычки включаются в электроды диодов или транзисторов. Перемычки могут быть металлическими (вначале изготавливались из нихрома, позднее из титановольфрамовых и других сплавов)

1)Термином «прошивка» иногда называют содержимое постоянной памяти. Это название появилось во времена памяти на ферритовых сердечниках, когда информация заносилась в ЗУ путем пропускания провода через определенные сердечники.

300

MUX 2

MUX 2 1

1