- •Лекции 13 -17

- •Особенности и основные характеристики плис семейств Spartan–3a и Spartan–3an

- •Программируемые логические генераторы

- •Блочная память

- •Аппаратные умножители — блоки dsp48e

- •Трассировочные ресурсы

- •1.1.7Трассировочные ресурсы

- •Состав семейства

- •Производительность

- •Fpga платформы плис Virtex-5 txt фирмы Xilin Общая характеристика

- •Назначение и применение

- •Переход к одночиповой реализации системы с суммарной пропускной способностью 100 Гбит/с

- •Программная поддержка

- •Семейство плис Virtex-5 fxt с встроенным процессорным ядром PowerPc 440 Характеристики плис платформы Virtex-5 ftx

- •Лекция 16 Stratix III – новое семейство fpga фирмы Altera

- •Архитектура fpga Stratix III

- •Адаптивные логические модули (alm)

- •Структура памяти TriMatrix

- •Блоки цифровой обработки сигналов

- •Банки ввода-вывода

- •Средства защиты проекта

- •Средства поддержки разработок

- •Архитектура плис со структурой cpld

- •Леция 17 40-нм fpga компании Altera Stratix IV

- •Процессоры dsp

- •Базовая логическая ячейка.

- •Пример пректирования цифровых устройств на основе плис

Архитектура плис со структурой cpld

ПЛИС XC9500 относится к классу МС со структурой, фирменное название которой CPLD (Complex Programmable Logic Device - комплексные программируемые логические устройства (КПЛУ)).

Структуру CPLD составляют макроячейки, позволяющие получать логические функции многих переменных с ограниченным числом термов. Микросхемы этого типа могут быть использованы для создания устройств, где требуется логические функции многих переменных и небольшое количество триггеров.

Для программирования МС семейства ХС9500 не требуется программатор - перепрограммирование осуществляется сигналами от элементов с напряжением питания +5 В через специальные выводы МС, т.е. производится в той же системе, где и применяется данная ПЛИС.

В состав семейства ХС9500 входят девять МС, емкостью от 36 до 576 макроячеек (от 800 до 12 800 вентилей, соответственно) в различных корпусах (табл. 3 в Приложении).

Общая структура МС семейства ХС9500

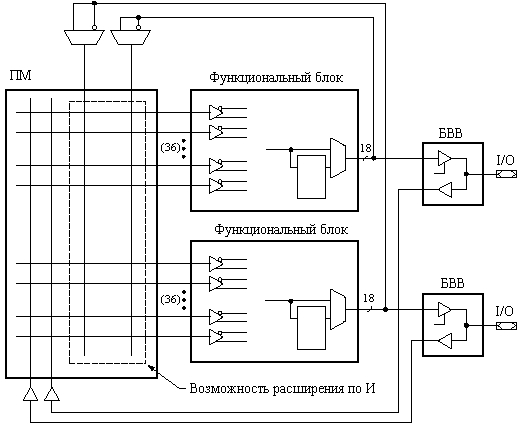

МС семейства ХС9500 состоит из функциональных блоков (ФБ) и блоков ввода/вывода (БВВ), соединённых переключающей матрицей (ПМ) (рис. 1.14).

Рис. 1.14. Структура МС семейства ХС9500

Все выводы ПЛИС семейства ХС9500 можно подразделить на три группы:

выводы стандартного JTAG-интерфейса, через которые производится программирование;

логические выводы, которые могут выполнять функцию входа, выхода или совмещенного входа/выхода (I/O);

управляющие выводы, на которые подаются глобальные управляющие сигналы тактирования (GCK), установки/сброса (GSR) и управления третьим состоянием (GTS). Управляющие выводы могут также выполнять функции логических выводов I/O.

Также имеются выводы "земли" и питания (на схеме не показаны).

Блоки ввода/вывода обеспечивают буферизацию всех входов и выходов МС.

Каждый ФБ содержит 18 макроячеек и позволяет получить 18 логических функций от 36 переменных.

Переключающая матрица (ПМ) обеспечивает подачу выходных сигналов ФБ и входных сигналов на входы ФБ.

Структура функционального блока

Функциональный блок (рис. 1.15) состоит из 18 независимых макроячеек (МЯ), распределителя термов (РТ) и матрицы логических произведений.

Макроячейка обеспечивает выполнение комбинаторной и/или регистровой функции. На каждую МЯ приходят сигналы разрешения выхода, установки/сброса и глобальной синхронизации. Каждый ФБ формирует 18 выходных сигналов, которые поступают на ПМ, а также передаются в БВВ.

Рис. 1.15. Схема функционального блока МС семейства ХС9500

Матрица логических произведений реализует конъюнкцию (терм) от 36 независимых переменных. Тридцать шесть входов обеспечивают использование 72 прямых и инверсных сигналов в матрице логических произведений для формирования до 90 термов. Любое подмножество этих термов может быть доступно каждой МЯ через схему распределения термов.

Каждый ФБ имеет внутренние цепи обратной связи, что позволяет любому количеству выходных сигналов ФБ поступать в свою собственную программируемую матрицу И, не выходя за пределы ФБ.

Любая макроячейка в МС семейства ХС9500 может выполнять как логическую комбинаторную, так и регистровую функции. Структура макроячейки совместно с программируемой матрицей логических произведений (элементов И, или "термов"), принадлежащим всему ФБ, представлена на рис. 1.16.

Рис. 1.16. Макроячейка МС семейства ХС9500

Каждая макроячейка имеет пять основных и четыре дополнительных входов, коммутируемых распределителем термов.

Из матрицы логических произведений пять термов поступают на основные входы макроячейки и могут использоваться либо для выполнения комбинаторных функций (ИЛИ и "Исключающее ИЛИ"), либо как управляющие сигналы.

Запоминающий элемент в макроячейке может быть сконфигурирован или как D-триггер, или как тактируемый триггер-защелка, или же он может отсутствовать. В последнем случае сигнал логической функции пропускается напрямую для использования в других макроячейках.

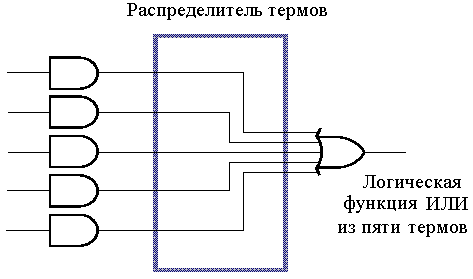

Распределитель термов управляет назначением пяти прямых термов к каждой макроячейке. К примеру, все пять прямых термов могут передаваться на элемент ИЛИ, как показано на рис. 1.17.

Распределитель термов может переназначить любой терм внутри ФБ для расширения логической емкости макроячейки сверх пяти прямых термов.

Каждой макроячейке, запрашивающей дополнительный терм, доступен любой незадействованный терм в другой макроячейке внутри данного ФБ. Одной макроячейке могут быть доступны до 15 термов, как показано на рис. 1.18.

Рис.

1.17.

Получение функции ИЛИ

Рис.

1.17.

Получение функции ИЛИ

Рис. 1.18. Схема расширения логической ёмкости МЯ

Переключающая матрица

Переключающая матрица коммутирует сигналы, поступающие с выходов ФБ и из БВВ на входы ФБ внутри МС, как показано на рис. 1.19. Выходные сигналы ФБ могут объединяться внутри ПМ по схеме "Монтажное И", что увеличивает логические возможности.

Блок ввода/вывода

Блок ввода/вывода (рис. 1.20) выполняет функцию интерфейса между внутренними логическими сигналами и контактами МС. Каждый БВВ содержит буферы ввода, буферы вывода и мультиплексор сигналов разрешения выхода.

Рис. 1.19. Быстродействующая ПМ микросхем семейства ХС9500

Входной буфер может работать с сигналами, имеющими стандартные КМОП- или ТТЛ-уровни от элементов с напряжением питания +5В, либо +3,3В.

Рис. 1.20. Блок ввода/вывода микросхем семейства ХС9500