- •Содержание

- •Введение

- •1. Общие положения

- •1.1. Методические указания по выполнению лабораторных работ

- •1.2. Порядок защиты и оформление отчета

- •2. Учебная система моделирования

- •2.1. Структура окна и система меню программы ewb

- •2.2. Проектирование цифровых устройств

- •2.3. Библиотека компонентов

- •2.4. Контрольно-измерительные приборы

- •3. Основы моделирования цифровых устройств

- •3.1. Логические элементы

- •3.2. Арифметические сумматоры

- •3.3. Триггеры

- •3.4. Регистры и счетчики

- •3.5. Мультивибраторы на логических элементах Автоколебательный мультивибратор

- •Ждущий мультивибратор

- •4. Лабораторный практикум Лабораторная работа №1 Исследование триггеров

- •I. Цель работы

- •II. Задание и указания обучающимся по подготовке и выполнению лабораторного занятия

- •III. Порядок выполнения работы

- •IV. Содержание отчета:

- •Лабораторная работа №2 Исследование мультивибраторов

- •I. Цель работы

- •II. Задание и указания обучающимся по подготовке и выполнению лабораторного занятия

- •III. Порядок выполнения работы

- •1. Исследование мультивибраторов на логических элементах

- •2. Исследование мультивибраторов на логических элементах в автоколебательном режиме

- •IV. Содержание отчета:

- •Лабораторная работа №3 Исследование комбинационных цифровых узлов

- •I. Цель работы

- •II. Задание и указания обучающимся по подготовке и выполнению лабораторного занятия

- •III. Порядок выполнения работы

- •IV. Содержание отчета:

- •Лабораторная работа № 4 Исследование последовательностных цифровых узлов

- •I. Цель работы

- •II. Задание и указания обучающимся по подготовке и выполнению лабораторного занятия

- •III. Порядок выполнения работы

- •IV. Содержание отчета:

- •Цифровые микросхемы

- •Комбинационные цифровые устройства в базисе и-не

- •1. Сумматор по модулю два

- •2. Полусумматор

- •3. Полный сумматор

- •4. Шифратор 4 х 2

- •5. Шифратор 8 х 3

- •6. Дешифратор 2 х 4

- •9. Компаратор для сравнения двух одноразрядных чисел

- •10. Компаратор для сравнения двух двухразрядных чисел

- •Последовательностные цифровые устройства

- •Реализация логических функций на основе замещения логическими элементами и-не

- •Литература

Лабораторная работа № 4 Исследование последовательностных цифровых узлов

I. Цель работы

Исследование процессов функционирования цифровых узлов последова- тельностного типа.

II. Задание и указания обучающимся по подготовке и выполнению лабораторного занятия

1. Курсантам в ходе самостоятельной подготовки накануне лабораторной работы необходимо:

уяснить цель, содержание и порядок выполнения работы;

повторить материал занятий 1, 2, 3, 4, 6, 7 темы 5 с целью подготовки ответов на ряд контрольных вопросов по принципам построения и функционирования цифровых узлов последовательностного типа:

регистры хранения;

регистры сдвига;

кольцевой регистр;

рекуррентный регистр;

классификация счётчиков;

счётчики с последовательным переносом;

счётчики с параллельным переносом;

реверсивные счётчики;

счётчики с обратными связями;

счётчики Джонсона.

2. Провести анализ схем, приведенных в приложении 4.

3. Оформить отчет по лабораторной работе и доказать полученные результаты. Отчет по лабораторной работе для проверки представляется ведущему преподавателю.

III. Порядок выполнения работы

Порядок проведения исследований предполагает выполнение следующих этапов:

собрать схему 4-х разрядного регистра (счетчика) на базе D-триггера с динамическим входом синхронизации;

подключить генератор слов ко входу исследуемого цифрового узла;

подключить логический анализатор к выходам цифрового узла;

выполнить согласование генератора слов и логического анализатора по частоте;

- используя логический анализатор, получить временные диаграммы функционирования регистра(счетчика);

зарисовать полученные диаграммы и оценить быстродействие исследуемого узла;

определить, как в зависимости от продвигающего импульса (по фронту или спаду) изменяются временные диаграммы на выходах регистра(счётчика);

по результатам исследований сделать выводы.

IV. Содержание отчета:

наименование работы;

цель работы;

схемы исследуемых цифровых узлов;

временные диаграммы;

экспериментальные и расчетные данные быстродействия цифровых узлов относительно времени задержки логических элементов;

выводы по каждому пункту работы.

Приложение № 1

Цифровые микросхемы

В зависимости от технологии изготовления интегральные микросхемы (ИМС) подразделяются на серии (семейства), различающиеся физическими параметрами базовых элементов и их функциональным назначением. Наибольшее распространение получили ИМС, изготовляемые по ТТЛ- и КМОП-технологиям. (ТТЛ - транзисторно-транзисторная логика с использованием биполярных транзисторов, КМОП - с использованием комплементарных МОП-транзисторов).

Первой была выпущена ТТЛ-серия SN74 / SN54 (74 - коммерческая, 54 - для военных применений). Отечественным аналогом серии SN74 стала популярная в свое время серия 155. В 1967 г. дополнительно разработаны семейства SN74H \ 54Н (High speed - быстродействующая, отечественные аналоги - серии 131 и 130) и SN74L / 54L - (Low power - маломощная, аналоги - серии 158 и 136).

В 1969 г. разработана серия SN74S / 54S (серии 531 и 530), в 1971 г. – серия SN74LS / 54LS (серии 555 и 533), в 1979 г. - серия SN74F / 54F фирмы Fairchild (FAST - Fairchild's Advanced Schottky TTL, серия 1531), в 1980 г. - серия SN74ALS / 54ALS (серия 1533), в 1982 г. - серия SN74AS / 54AS (в обозначениях серий S - Schottky, LS -Low power Schottky, ALS - Advanced Low power Schottky, AS - Advanced Schottky, Advanced - усовершенствованная). Использование диодов с барьером Шотки позволило значительно повысить быстродействие ИМС за счет предотвращения глубокого насыщения транзисторов в ключевом режиме. Особенностью всех перечисленных серий является полное совпадение номеров выводов и обозначения типа для ИМС одинакового функционального назначения. Например, если SN7472 - JK-триггер, то обозначение 72 будет присутствовать во всех сериях. Этот же принцип используется и в отечественных ИМС, где тип обозначается буквами. В EWB 5.0 для всех цифровых ИМС введена нумерация выводов, позволяющая определять их функциональное назначение при сопоставлении с отечественными аналогами.

В библиотеке программы EWB используется только серия SN74. В число редактируемых параметров цифровых ИМС входят:

VON, VOL - верхний и нижний уровни выходного сигнала;

VIH, VIL - верхний и нижний уровни входного сигнала;

TPLH - задержка распространения сигнала при включении (обычно дается на уровне 1,0);

TPHL - задержка при включении (на уровне 0,1);

VTG - среднее напряжение срабатывания.

Для облегчения работы с библиотекой ниже приводится список отечественных аналогов серии SN74 (для краткости некоторые повторяющиеся символы опущены).

7400 |

155ЛА3 |

4 элемента 2И-НЕ (цифра 2 означает двухвходовой); |

7402 |

155ЛЕ1 |

4 элемента 2ИЛИ-НЕ; |

7403 |

155ЛА9 |

4 элемента 2И-НЕ с открытым коллектором (позволяют подключать нагрузку с питанием от более высоковольтного источника питания); |

7404 |

155ЛН1 |

6 элементов НЕ; |

7405 |

555ЛН2 |

6 элементов НЕ с открытым коллектором; |

7406 |

155ЛН3 |

6 элементов НЕ с открытым коллектором; |

7407 |

155ЛП9 |

6 буферных элементов с открытым коллектором; |

7408 |

155ЛИ1 |

4 элемента 2И; |

7409 |

155ЛИ2 |

4 элемента 2И с открытым коллектором; |

7410 |

155ЛА4 |

3 элемента 3И-НЕ; |

7411 |

555ЛИ3 |

3 элемента 3И; |

7412 |

155ЛА10 |

3 элемента 3И-НЕ с открытым коллектором; |

7414 |

155ТЛ2 |

6 триггеров Шмитта с инверсией (обладают повышенной помехозащищенностью); |

7416 |

155ЛН5 |

6 буферных элементов НЕ; |

7417 |

155ЛП4 |

6 буферных элементов с открытым коллектором; |

7420 |

155ЛА1 |

2 элемента 4И-НЕ; |

7421 |

155ЛИ6 |

2 элемента 4И; |

7422 |

155ЛА7 |

2 элемента 4И-НЕ с открытым коллектором; |

7425 |

155ЛЕ3 |

2 элемента 4И-НЕ с входом стробирования; |

7426 |

155ЛА11 |

4 элемента 2И-НЕ с открытым коллектором; |

7428 |

155ЛЕ5 |

4 элемента 2ИЛИ-НЕ; |

7430 |

155ЛА2 |

элемент 8И-НЕ; |

7432 |

155ЛЛ1 |

4 элемента 2ИЛИ; |

7437 |

155ЛА12 |

4 элемента 2И-НЕ с открытым коллектором; |

7438 |

155ЛА13 |

4 элемента 2И-НЕ с открытым коллектором; |

7440 |

155ЛА6 |

2 элемента 4И-НЕ с повышенной нагрузочной способностью; |

7442 |

555ИД6 |

дешифратор 4 х 10 (декодирование 4-разрядного двоичного числа в десятичное); |

7451 |

155ЛР11 |

элементы 2-2И-2ИЛИ-НЕ (2 элемента 2И, выходы которых подключены на кристалле ИМС к элементу 2ИЛИ-НЕ) и 2-3И-2ИЛИ-НЕ (аналогично для 2-3И); |

7454 |

155ЛР13 |

элемент 2-3-3-2И-4ИЛИ-НЕ (2 элемента 2И и 2 элемента 3И объединены через 4ИЛИ-НЕ); |

7455 |

155ЛР4 |

элемент 4-4И-2ИЛИ-НЕ (2 элемента 4И объединены через 2ИЛИ-НЕ) с возможностью объединения по ИЛИ (выходной каскад элемента 2ИЛИ-НЕ имеет дополнительные входы транзистора С - Collector и E - Emitter, что и позволяет осуществить объединение по ИЛИ); |

7472 |

155ТВ1 |

JK-триггер с элементом 3И на входах; |

7474 |

155ТМ2 |

2 D-триггера; |

7475 |

155ТМ7 |

4 D-триггера с прямыми и инверсными выходами; |

7476 |

155ТВ7 |

2 JK-триггера; |

7477 |

155ТМ5 |

4 D-триггера с прямыми выходами; |

7478 |

134ТВ14 |

два JK-триггера; |

7486 |

155ЛП5 |

4 элемента Исключающее ИЛИ; |

7490 |

155ИЕ2 |

4-разрядный асинхронный двоично-десятичный счетчик; |

7491 |

134ИР2 |

8-разрядный сдвиговый регистр; |

7492 |

155ИЕ4 |

4-разрядный асинхронный счетчик-делитель на 12; |

7493 |

155ИЕ5 |

4-разрядный асинхронный двоичный счетчик; |

74107 |

155ТВ6 |

2 JK-триггера с раздельной установкой нуля; |

74109 |

155ТВ15 |

2 JK-триггера; |

74112 |

155ТВ9 |

2 JK-триггера; |

74113 |

155ТВ10 |

2 JK-триггера с предустановкой нуля или единицы; |

74114 |

155ТВ11 |

2 JK-триггера с предустановкой нуля или единицы и общим обнулением; |

74125 |

155ЛП8 |

4 буфера с тремя состояниями; |

74126 |

155ЛП14 |

4 формирователя с тремя состояниями; |

74132 |

155ТЛ3 |

4 триггера Шмитта; |

74134 |

155ЛА19 |

элемент 12И-НЕ с тремя состояниями; |

74138 |

155ИД7 |

дешифратор-демультиплексор 3 х 8; |

74139 |

155ИД14 |

2 дешифратора-демультиплексора 2 х 4; |

74145 |

155ИД10 |

двоично-десятичный дешифратор с открытым коллектором; |

74147 |

555ИВ3 |

приоритетный шифратор 10- 4; |

74148 |

155ИВ1 |

шифратор приоритетов 8 х 3; |

74150 |

155КП1 |

селектор-мультиплексор 16 х 1; |

74151 |

155КП7 |

селектор-мультиплексор 8 х 1; |

74152 |

155КП5 |

селектор-мультиплексор 8 х 1; |

74153 |

155КП2 |

2 селектора-мультиплексора 4 х 2; |

74154 |

155ИД3 |

дешифратор-демультиплексор 4 х 16; |

74155 |

155ИД4 |

2 дешифратора-мультиплексора 2 х 4; |

74156 |

555ИД5 |

2 дешифратора-демультиплексора 2 х 4 с открытым коллектором; |

74157 |

533КП16 |

4-разрядный селектор-мультиплексор 2 х 1; |

74158 |

1533КП18 |

4-разрядный селектор-мультиплексор 2 х 1 с инверсией; |

74160 |

155ИЕ9 |

4-разрядный синхронный двоично-десятичный счетчик; |

74162 |

155ИЕ11 |

4-разрядный синхронный десятичный счетчик; |

74163 |

155ИЕ18 |

4-разрядный синхронный реверсивный двоично-десятичный счетчик; |

74164 |

155ИР8 |

8-разрядный регистр сдвига с параллельными выходами; |

74165 |

155ИР9 |

8-разрядный регистр сдвига с параллельным вводом информации; |

74166 |

155ИР10 |

8-разрядный регистр сдвига с синхронным параллельным вводом; |

74169 |

155ИЕ17 |

4-разрядный двоичный синхронный реверсивный счетчик; |

74173 |

155ИР15 |

4-разрядный регистр с тремя состояниями; |

74174 |

155ТМ9 |

6 D-триггеров; |

74175 |

155ТМ8 |

4 D-триггера; |

74181 |

155ИП3 |

4-разрядное АЛУ; |

74191 |

155ИЕ13 |

синхронный реверсивный двоичный счетчик; |

74192 |

155ИЕ6 |

двоично-десятичный реверсивный счетчик; |

74194 |

155ИР11 |

4-разрядный универсальный регистр сдвига; |

74195 |

155ИР12 |

4-разрядный регистр сдвига с параллельным вводом; |

74198 |

155ИР13 |

8-разрядный универсальный регистр сдвига; |

74240 |

155АП3 |

8 буферов с инверсией и тремя состояниями; |

74241 |

155АП4 |

8 буферов с тремя состояниями; |

74244 |

155АП5 |

2 х 4 буферов с тремя состояниями; |

74251 |

155КП15 |

селектор-мультиплексор 8 х 1 с тремя состояниями; |

74253 |

155КП12 |

2 селектора-мультиплексора 4 х 1 с тремя состояниями; |

74257 |

155КП11 |

4 селектора-мультиплексора 2 х 1 с тремя состояниями; |

74258 |

155КП14 |

4 селектора-мультиплексора 2 х 1 с тремя состояниями и инверсией; |

74273 |

155ИР35 |

8-разрядный регистр с установкой нуля; |

74279 |

155ТР2 |

4 RS-триггера-защелки; |

74280 |

155ИП5 |

9-разрядная схема контроля четности; |

74283 |

155ИМ6 |

4-разрядный полный сумматор с ускоренным переносом; |

74298 |

155КП13 |

4 2-входовых мультиплексора с запоминанием; |

74353 |

155КП17 |

сдвоенный мультиплексор 4 х 1 с инверсией и тремя состояниями выхода; |

74365 |

155ЛП10 |

6 повторителей с управлением по входам и тремя состояниями; |

74367 |

155ЛП11 |

6 повторителей с раздельным управлением по входам и тремя состояниями; |

74373 |

155ИР22 |

8-разрядный буферный регистр с тремя состояниями и потенциальным управлением; |

74374 |

155ИР23 |

8-разрядный буферный регистр с тремя состояниями и импульсным управлением; |

74377 |

155ИР27 |

8-разрядный регистр с разрешением записи; |

74395 |

155ИР25 |

4-разрядный параллельный регистр сдвига. |

Ссылки в этом перечне на ИМС других серий вызваны их отсутствием в серии 155, однако здесь это не имеет существенного значения, поскольку речь идет только о выяснении функционального назначения выводов.

Цифровые ИМС КМОП-серии получили название от своего базового элемента, в котором используется так называемая комплементарная пара из двух МОП-транзисторов различной проводимости. Такие ИМС характеризуются малым потреблением мощности в статическом режиме (0,02 ... 1 мкВт на вентиль), большим диапазоном питающих напряжений (3... 18 В), высоким входным сопротивлением, большой нагрузочной способностью, незначительной зависимостью характеристик от температуры, малыми размерами транзисторов в интегральном исполнении и, как следствие, более высокой степенью интеграции по сравнению с ТТЛ-микросхемами.

Первые ИМС по КМОП-технологии разработаны фирмой RCA в 1968 г. Эта серия имела название CD4000 (отечественные аналоги - 564, 561 и 1561). а также МС14000А и МС14000В фирмы Motorola и 54НС фирмы National Semiconductor в 1981 г. (отечественный аналог - серия 1564). В библиотеке программы EWB используются ИМС фирмы RCA, большинство которых приведено в следующем перечне:

4000 |

176ЛП4 |

2 элемента 3ИЛИ-НЕ и 1 НЕ; |

4001 |

561ЛЕ5 |

4 элемента 2ИЛИ-НЕ; |

4002 |

561ЛЕ6 |

2 элемента 4ИЛИ-НЕ; |

4008 |

561ИМ1 |

4-разрядный полный сумматор; |

4009 |

176ПУ2 |

6 преобразователей уровня с инверсией; |

4010 |

176ПУ3 |

6 преобразователей уровня без инверсии; |

4011 |

561ЛА7 |

4 элемента 2И-НЕ; |

4012 |

561ЛА8 |

2 элемента 4И-НЕ; |

4013 |

561ТМ2 |

2 D-триггера; |

4015 |

561ИР2 |

2 4-разрядных сдвиговых регистра; |

4017 |

561ИЕ8 |

десятичный счетчик с дешифратором; |

4019 |

561ЛС2 |

4 элемента И-ИЛИ; |

4023 |

561ЛА9 |

3 элемента 3И-НЕ; |

4024 |

176ИЕ1 |

6-разрядный двоичный счетчик; |

4025 |

1561ЛЕ10 |

3 элемента 3ИЛИ-НЕ; |

4027 |

561ТВ1 |

два JK-триггера; |

4028 |

561ИД1 |

двоично-десятичный дешифратор; |

4030 |

561ЛП2 |

4 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ; |

4040 |

1561ИЕ20 |

12-разрядный двоичный счетчик; |

4042 |

561ТМ3 |

четыре D-триггера; |

4043 |

561ТР2 |

четыре RS-триггера; |

4049 |

561ЛН2 |

6 элементов НЕ; |

4050 |

561ПУ4 |

6 преобразователей уровня; |

4066 |

561КТ3 |

4 переключателя (цифрового или аналогового сигнала); |

4070 |

1561ЛП14 |

4 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ; |

4081 |

1561ЛИ2 |

4 элемента 2И; |

4502 |

561ЛН1 |

6 стробируемых инверторов; |

4516 |

561ИЕ11 |

4-разрядный реверсивный счетчик; |

4520 |

561ИЕ10 |

2 4-разрядных счетчика; |

4556 |

1561ИД7 |

двоичный декодер-демультиплексор. |

Приведем систему обозначений входов и выходов простейших логических элементов, используемых в программе EWB. Обозначения для ТТЛ-серии приводятся в первых круглых скобках, для КМОП – во вторых, при одинаковых обозначениях – без скобок:

Вывод для питания – (Ucc), (Udd);

Общий вывод – (GND), (Uss);

Вывод не подключен – NC;

Входы – (А, В, С ...), (I);

Выходы – (Y), (О);

Вход стробирования – G.

Приведем пример обозначения последовательности выводов для 2-входовых логических элементов:

(1A 1B 1Y, 2A 2B 2Y, 3A 3B 3Y, 4A 4B 4Y), (I1 I2 O1, I3 I4 O2, I5 I6 O3, I7 I8 O4).

Для более сложных ИМС определение функционального назначения их выводов целесообразно проводить путем сопоставления с отечественными аналогами.

Кроме того может использоваться перечень наиболее распространенных мнемонических обозначений на их функциональных схемах или в таблицах состояний.

A = B (Parity) |

- выход равенства операндов А и В; |

A / S (Asynchro / Synchro) |

- вход асинхронного и синхронного режимов; |

B / D (Binary / Decimal) |

- вход переключения счета с двоичного на десятичный; |

C (Clock input) |

- вход тактовых импульсов; |

CD (Count down) |

- вход тактовых импульсов на уменьшение счета (в реверсивных счетчиках); |

CU (Count up) |

- вход тактовых импульсов на увеличение счета; |

CE (Clock enable) |

- вход разрешения для тактовых импульсов; |

CEP (Count enable parallel) |

- вход параллельного наращивания разрядов счетчика; |

CET (Count enable trickle) |

- вход разрешения счета при наращивании разрядов счетчика; |

CLR (Clear) |

- вход сброса; |

Cin, Cn (Carry in) |

- вход для разряда переноса; |

CS (Chip select) |

- выбор кристалла; определяет доступ к одной из ИМС устройства; |

D (Data input) |

- вход данных триггера, счетчика, регистра; |

DSI (Data serial input) |

- вход последовательных данных; |

DS (Data select) |

- вход выбора данных; |

DL, DR (Data left, Data right) |

- входы для последовательной загрузки (регистра) слева, справа; |

DSL, DSR (Data shift left, Data shift right) |

- входы для сдвига данных влево, вправо; |

E (Enable) |

- вход сигнала разрешения; |

EC (Enable count) |

- вход сигнала разрешения счета; |

EE (Enable even) |

- вход сигнала разрешения, счетный; |

EI (Enable input) |

- вывод ИМС, по которому дается разрешение на прием данных; |

EIO (Enable input / output) |

- вывод для одновременного разрешения по входу и выходу; |

EO (Enable output) |

- вывод для разрешения по выходу; |

LSB (Least significant bit) |

- младший значащий разряд (МЗР); |

M (Mode control) |

- выбор режима «Арифметика-логика» в АЛУ; |

PE (Parallel enable load) |

- вход разрешения параллельной загрузки; |

P / S (Parallel / serial) |

- вход переключения режимов параллельной или последовательной загрузки; |

R (Reset) |

- асинхронный сброс данных; |

RE (Read enable) |

- вход разрешения чтения; |

S (Set) |

- установка триггера, счетчика, регистра; |

SE (Set enable) |

- разрешение предварительной параллельной записи; |

SI (Serial input) |

- вход последовательный; |

SIR, SIL (Serial input right, serial input left) |

- вход последовательный справа, слева; |

SR (Synchro reset) |

- вход сброса синхронно с тактовым импульсом; |

TC (Terminal count) |

- выход окончания счета; |

TCD (Terminal count down) |

- то же, на уменьшение счета; |

TCU (Terminal count up) |

- то же, не увеличение счета. |

Приложение № 2

а)

б)

Рис. 32. Формирователь импульсов

а) схема формирователя коротких импульсов; б) временные диаграммы

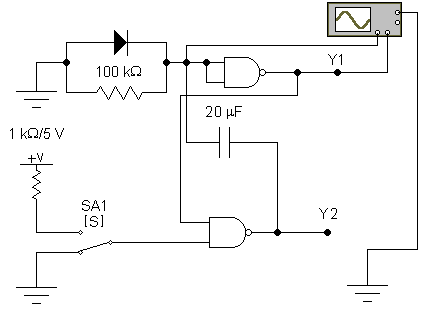

Рис. 33. Схема для исследования ждущего мультивибратора

Рис. 34. Схема для исследования ждущего мультивибратора

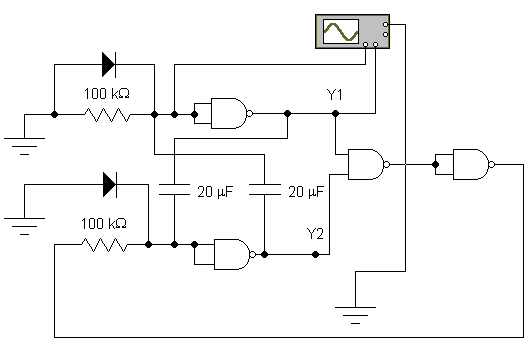

Рис. 35. Схема для исследования автоколебательного мультивибратора

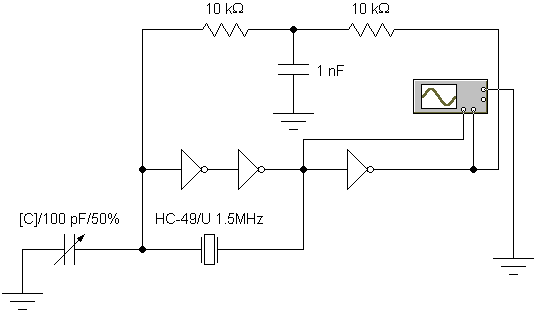

Рис. 36. Схема для исследования мультивибратора с кварцевым резонатором

в цепи обратной связи

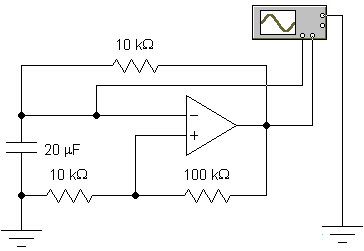

Рис. 37. Схема для исследования мультивибратора на операционном усилителе

Приложение 3