- •Вимоги до виконання лабораторних робіт

- •Вступ Бібліотеки цифрових пристроїв та інструментарій програмного середовища ms10

- •10.1.1. Генератор бінарного слова

- •10.1.2. Логічний аналізатор

- •Лабораторна робота № 1

- •Теоретичні відомості

- •3. Базові логічні елементи

- •5. Перехід від логічної функції до логічної схеми

- •Навчальні завдання і методичні вказівки до їх виконання

- •Лабораторна робота № 2

- •Теоретичні відомості

- •Дешифратор

- •Шифратор

- •Мультиплексор

- •Демультиплексор

- •Хід роботи і вказівки до її виконання

- •Лабораторна робота № 3

- •Лабораторна робота № 4

- •Теоретичні відомості

- •Асинхронний і синхронний rs-тригери

- •Навчальні завдання і методичні вказівки до їх виконання

- •Лабораторна робота № 5

- •Теоретичні відомості

- •Паралельний регістр на rs-тригерах

- •Навчальні завдання:

- •Лабораторна робота № 6

- •Теоретичні відомості

- •2. Лічильник з безпосередніми звʼЯзками

- •3. Сумуючий синхронний лічильник

- •4. Реверсивний синхронний лічильник

- •5. Десятковий лічильник

- •Навчальні завдання і методичні вказівки до їх виконання

- •Лабораторна робота № 7

- •Теоретичні відомості і розрахункові формули

- •Структура резистивних матриць цап

- •Основні параметри цап

- •Навчальні завдання і методиичні вказівки до їх виконання

- •Лабораторна робота № 8

- •Теоретичні відомості

- •Структурна схема ацп послідовної дії

- •Основні параметри ацп

- •Навчальні завдання

Лабораторна робота № 4

Тема роботи: Тригери

Мета роботи: Ознайомлення з основними характеристиками і випробовування інтегральних RS, D, T і JK.

Теоретичні відомості

Тригер – це пристрій послідовного типу з двома стійкими станами рівноваги, призначений для запису і зберігання інформації. Під дією вхідних сигналів тригер може переключатися із одного стійкого стану в інший. При цьому напруга на його вході стрибкоподібно змінюється з низького рівня на високий або навпаки.

По способу запису інформації тригери ділять на асинхронні, котрі переключаються в момент подачі вхідного сигналу, і синхронні(трактуємі), котрі переключаються тільки при подачі синхронізуючих імпульсів, а момент переключення пов’язаний з визначеним рівнем синхросигналу (статичні тригери) або з моментом перепаду напруги на трактуємому вході (динамічні тригери).

Як правило, тригер має два виходи: прямий Q і інверсний Q. Число входів залежить від структури і функцій, виконуючихся тригером. Наприклад, асинхронні RS-тригери мають два входи: вхід S установки в одиничний стан прямого виходу Q і вхід R установки в нульовий стан вихода Q. Синхронні тригери для занесення в них інформації, крім інформаційних входів S(J) і R(K), мають синхронізуючий C або лічильний T вхід, а тригери затримки – інформаційний вхід D.

Найбільше розповсюдження в цифрових пристроях отримали тригери RS, D, T і JK.

Асинхронний і синхронний rs-тригери

Н айпростішим

тригером являється асинхроннийRS-тригер,

умовне графічне зображення якого

представлено на рис. 12.1, а.

Тригер має два роздільних інформаційних

входа: R і S і два вихода: Q і . Незалежним

являється один (прямий) вихід Q, так як

інверсний сигнал можна отримати за

допомогою зовнішнього інвертора.

айпростішим

тригером являється асинхроннийRS-тригер,

умовне графічне зображення якого

представлено на рис. 12.1, а.

Тригер має два роздільних інформаційних

входа: R і S і два вихода: Q і . Незалежним

являється один (прямий) вихід Q, так як

інверсний сигнал можна отримати за

допомогою зовнішнього інвертора.

На рис. 12.1, в зображена часова діаграма, ілюструюча його роботу. В момент, коли подається сигнал S = 1, тригер переходить в стан Q = 1. При відсутності вхідних сигналів стан тригера не змінюється, а в момент подачі сигнала R = 1 тригер переключається в стан Q = 0, в якому перебуває до постачання нового одиничного сигнала на S-вхід.

Асинхронний RS-тригер можна перетворювати в синхронний, якщо додати третій синхронізуючий вхід C (рис. 12.1, б).

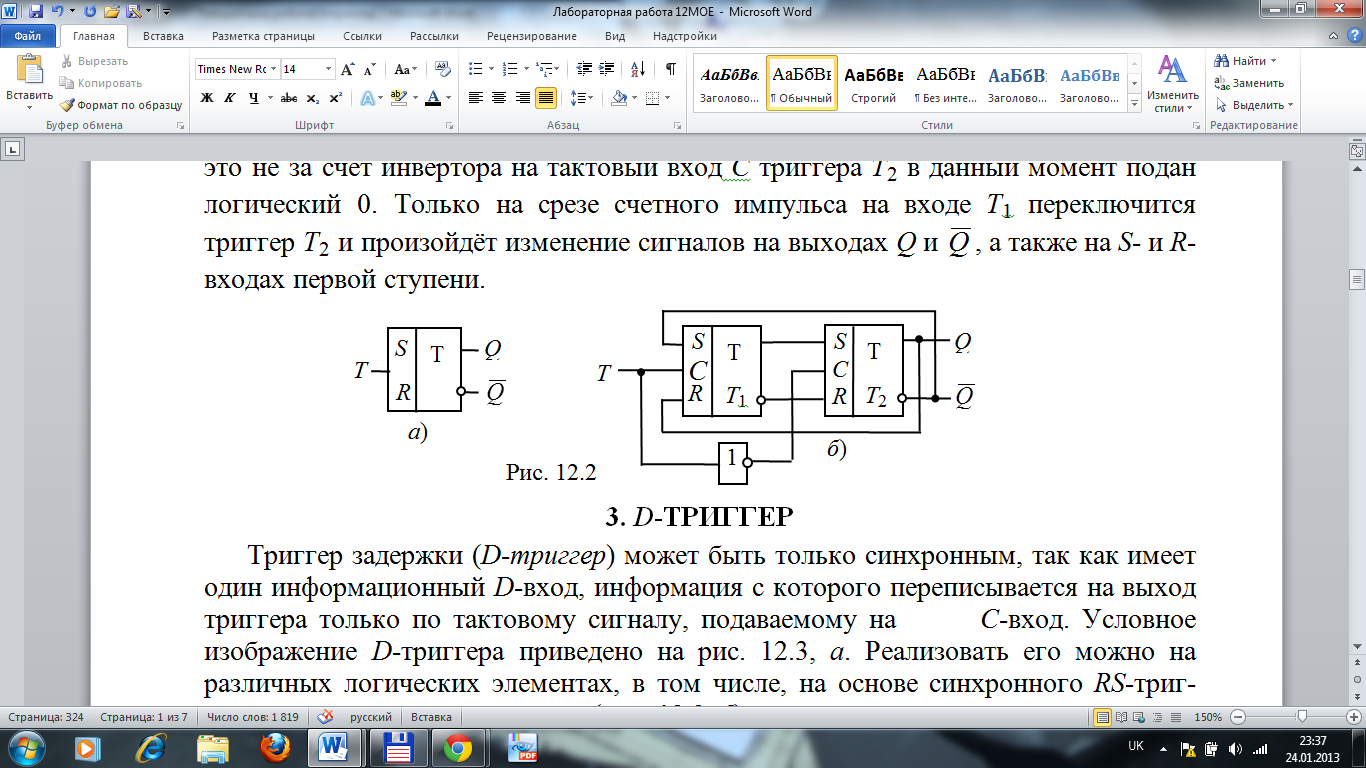

Т-ТРИГЕР

Тригер з рахунковим запуском (Т-тригер)повинен перемикатися кожним імпульсом, подаваним на єдиний рахунковий вхід Т (рис. 12.2, а). Функціонування Т-тригера визначається рівнянням

Він

може бути реалізований, наприклад, на

базі двох синхронних RS-тригерів

(рис. 12.2, б).

З появою фронта тактового імпульса

тригер Т1 першого ступеня перемикається

в стан, протилежний стану тригера Т2.

Але це не за рахунок інвертора на тактовий

вхід C тригера Т2 в даний момент поданий

логічний 0. Тільки на зрізі рахункового

імпульсу

на вході Т1 перемкнеться тригер Т2 і

відбудеться зміна сигналів на виходах

Q

і

,

а також на S- і R- входах першого ступеня.

,

а також на S- і R- входах першого ступеня.

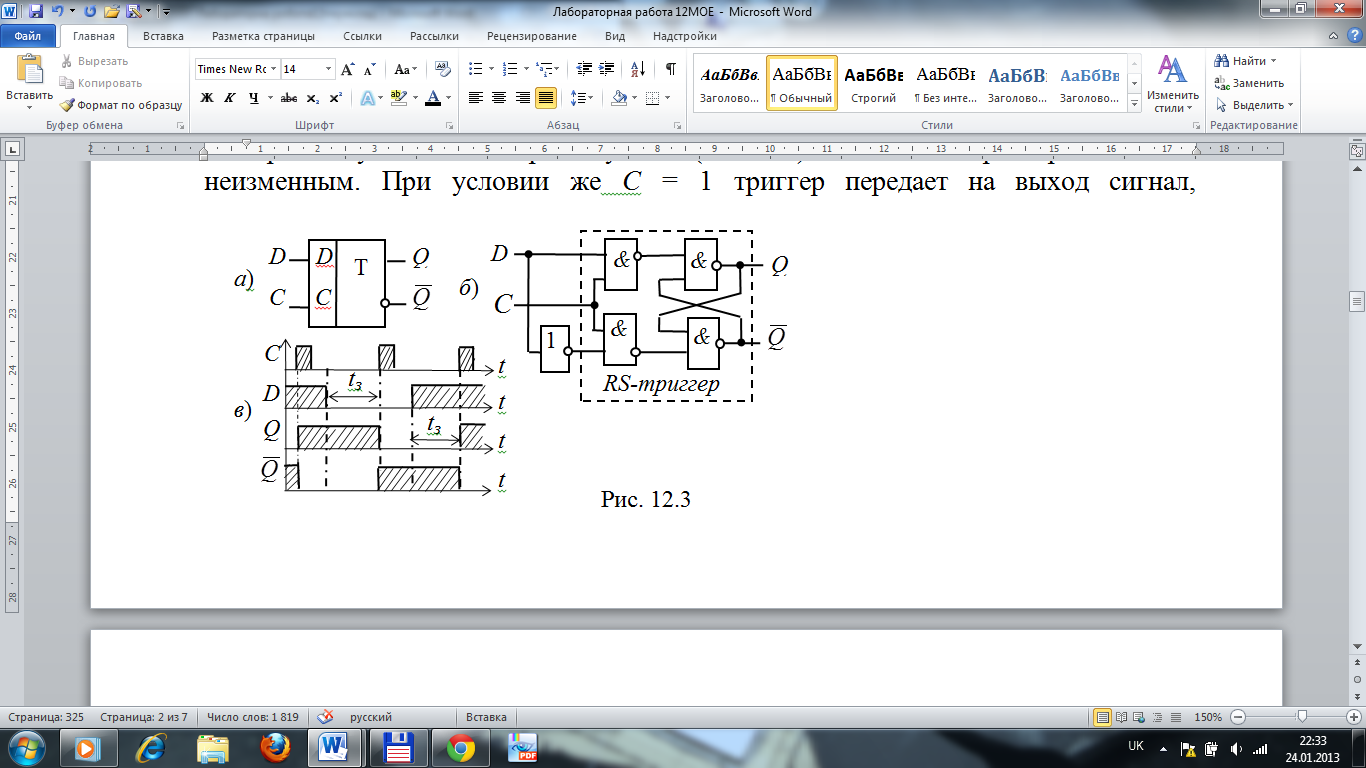

D-ТРИГЕР

Тригер затримки (D-тригер) може бути тільки синхронним, так як має тільки один інформаційний D-вхід, інформація з якого переписується на вихід тригера тільки по тактовому сигналу, подаваному на C-вхід. Умовне зображення D-тригера приведено на рис. 12.3, а. Реалізувати його можна на різних логічних елементах, в тому числі, на основі синхронного RS-тригера, доповненого інвертором (рис. 12.3, б).

При відсутності синхроімпульса (C = 0) стан тригера залишається незмінним. При умові ж C = 1 тригер передає на вихід сигнал, надійшовший на його вхід D в попередньому такті, тобто вихідний сигнал Qt+1 змінюється з затримкою на один період імпульсів синхронізації.

Із аналіза часової діаграми D-тригера (рис. 12.3, в) також слідує, що вихідний сигнал Q тригера повторює стан D-входа з надходженням чергового тактового імпульса на вхід C з затримкою t3 відносно змінившогося логічного стану на D-вході.

JK-ТРИГЕР

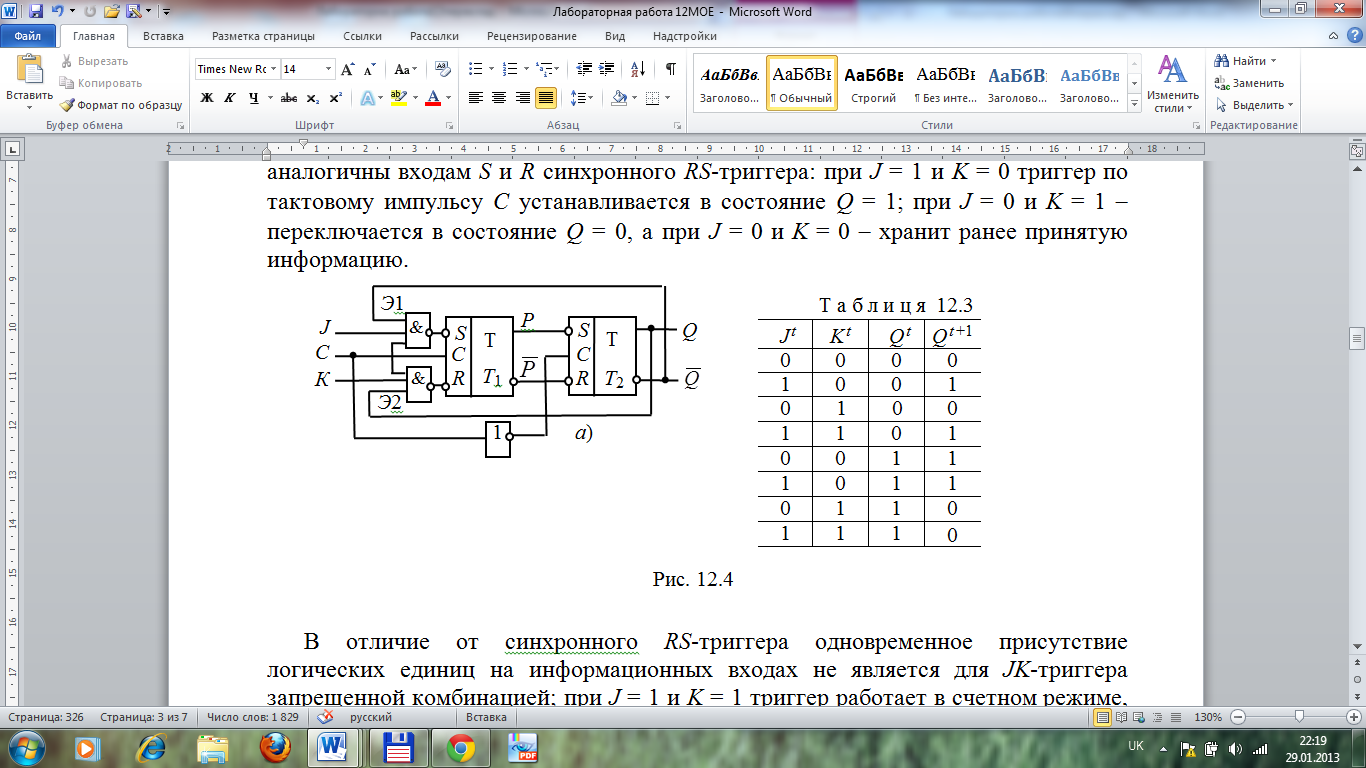

JK-тригери звичайно виконують тактованими. JK-тригер має інформаційні входи J і K, котрі по своїй дії на пристрій аналогічні входам S і R синхронного RS-тригера: при J = 1 і K = 0 тригер по тактовому імпульсу C встановлюється в стан Q= 1; при J = 0 і K = 1 – перемикається в стан Q = 0, а при J = 0 і K = 0 – зберігає раніше прийняту інформацію.

На відміну від синхронного RS-тригера одночасна присутність логічних одиниць на інформаційних входах не являється для JK-тригера забороненою комбінацію; при J = 1 і K = 1 тригер працює в рахунковому режимі, тобто перемикається кожним тактовим імпульсом на вході C.

На рис. 12.4, а зображена одна з функціональних схем JK-тригера. Вона відрізняється від схеми Т-тригера (див. рис. 12.2, б) двома тривходовими елементами І-НІ Е1 і Е2 вхідної логіки першого ступеня JK-тригера. Перемикаючий вхід С – динамічний (рис. 12.4, б): перемикання JK-тригера відбувається в момент перепаду синхроімпуьлса з рівня С = 1 на рівень С = 0, тобто при зрізі.

При J = 0 і K = 0 на виході елементів Е1 і Е2 встановлюються логічні одиниці, які для тригерів з інверсними входами являються пасивними сигналами: тригер Т1 і, отже, JK-тригер вцілому зберігає попередній стан (див. рис. 12.4, а). Логічна одиниця на одному із входів елемента І-ІН не визначає 1 на його виході і комбінація J = 1, K = 1 ніяк не впливає на вхідну логіку першого ступеня, тому схеми Т- і JK-тригерів (див. рис. 12.2, б і рис. 12.4, а) принципово не відрізняються: обидва працюють в рахунковому режимі.

Тільки при комбінації сигналівJ= 1, С = 1 и = 1 на входіелементуЕ1 тригер Т1 перемикається в стан Р = 1. Аналогічно логічний 0 буде на виході елементу Е2, коли К = 1, С = 1 і Q = 1.

Таким чином, комбінація J = 1, К = 0 обумовлюють по тактовому імпульсу С = 1 перемикання JK-тригери в цілому в стані Q = 1, а комбінація J = 0, K = 1 –в стані Q = 0.

Із аналіза таблиці 12.3 перемикальної функції JK-тригера

слідує,

що стан тригера визначається не тільки

рівнями сигналів на інформаційних

входах Jі

К, але і станом Qt,

в якому раніше знаходився JK-тригер.

Так, при комбінації J

= 0, K

= 0 тригер зберігає попередні стани (Qt+1

= Qt);

комбінація J

= 1, K

= 1 приводить до того, що тактовим імпульсом

тригер перемикається в стан, протилежний

попередньому: .

Комбінації J

= 1, K

= 0 і J

= 0, К = 1 дають дозвіл тригеру перемкнутися

відповідно в стан Q

= 1 і Q

= 0.

.

Комбінації J

= 1, K

= 0 і J

= 0, К = 1 дають дозвіл тригеру перемкнутися

відповідно в стан Q

= 1 і Q

= 0.

В інтегральній схемотехніці найбільше розповсюдження отримали D- і JK-тригери.