- •Лабораторная работа №3 Изучение интерфейса клавиатуры персональной эвм

- •Порядок выполнения работы.

- •Приложение 1 – Команды контроллера клавиатуры

- •Установить индикаторы состояния (еDh)

- •Выбрать альтернативный режим (f0h)

- •Холостые операции (еFh-f1h)

- •Идентификатор расширенной клавиатуры (f2h)

- •Установить частоту повторения клавиши (f3h)

- •Разрешить клавиатуру (f4h)

- •Запрет по умолчанию (f5h)

- •Установить условия по умолчанию (f6h)

- •Установить все клавиши (f7h, f8h, f9h, fАh)

- •Установить отдельные клавиши (fВh, fСh, fDh)

- •Коды ответов клавиатуры

Лабораторная работа №3 Изучение интерфейса клавиатуры персональной эвм

Цель работы: Изучить протокол работы интерфейса клавиатуры, структуру контроллера клавиатуры, приемы управления контроллером клавиатуры и клавиатурой.

Краткие теоретические сведения.

В архитектуре IBM РС АТ новое качество в сравнении с РС ХТ приобрел контроллер клавиатуры – однокристальная микро–ЭВМ i8042 (или совместимая), которая представляет собой контроллер универсального периферийного интерфейса (UPI) и обеспечивает выполнение следующих функций:

управление определенными системными функциями и интерфейсом клавиатуры;

чтение информации о конфигурации системы для процедур BIOS.

В контроллере i8042 имеется внутреннее ПЗУ, которое, программируется с учетом кодов сканирования клавиатуры и рабочих команд.

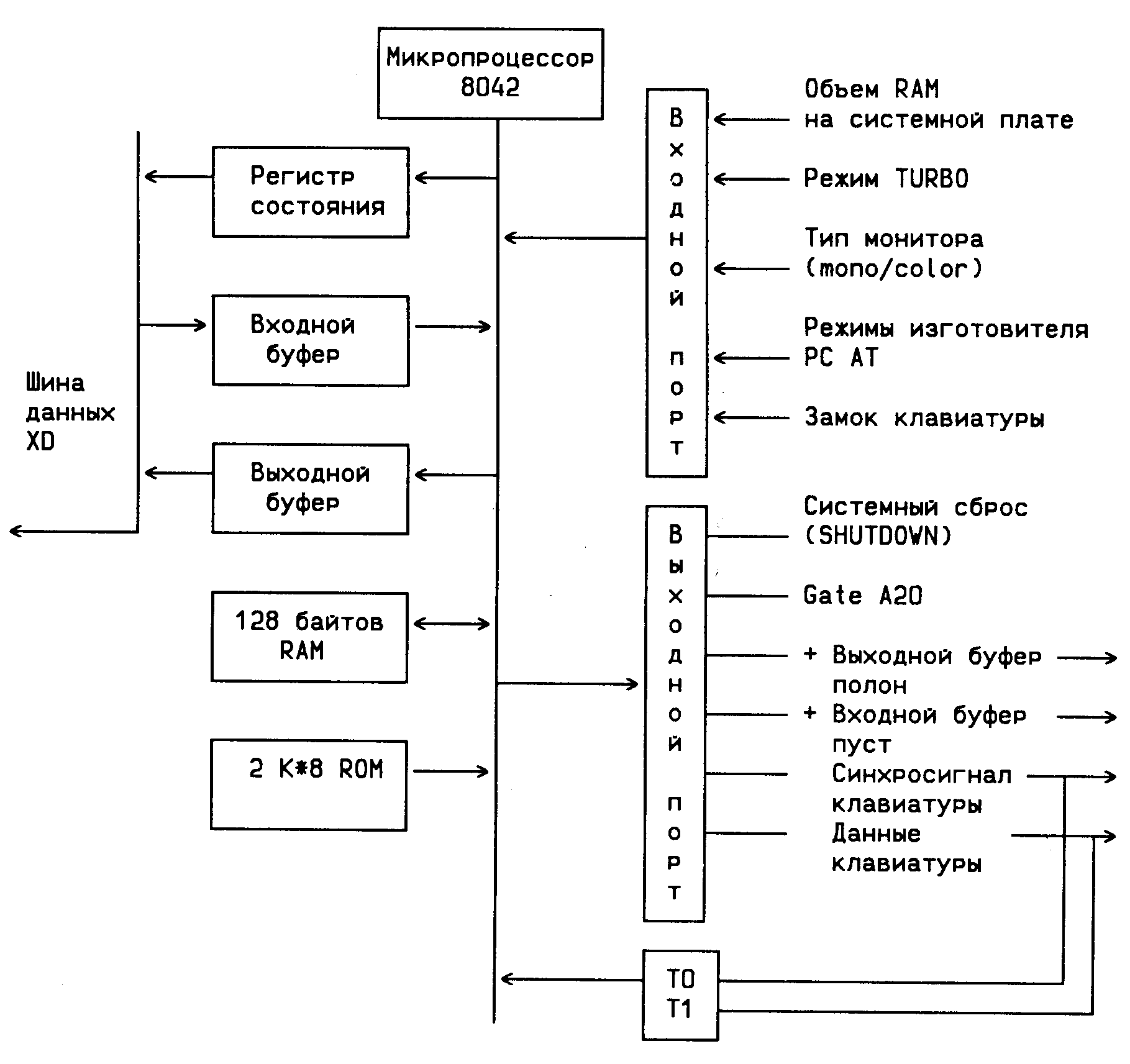

На рис. 1 приведена структурная схема контроллера клавиатуры.

Архитектура контроллера i8042 включает в себя три порта для непосредственного подключения аппаратуры:

8–ми разрядный выходной порт для управления системными функциями и обмена с клавиатурой (порт 2);

8–ми разрядный входной порт чтения информации о конфигурации системы для процедур BIOS (порт 1);

2–х разрядный контрольный порт чтения состояния линий синхронизации и данных клавиатуры (ТЕSТ0, ТЕSТ1).

Приведем назначение основных разрядов вышеуказанных портов:

Режимы изготовителя (разряды 0–3 вх. порта) – определяют состояние перемычек на системной плате ПК;

Объем ОЗУ на системной плате (разряд 4 вх. порта) определяет наличие в системе более чем 640К ОЗУ;

Р ис.

1 – Структура и подключение контроллера

клавиатуры

ис.

1 – Структура и подключение контроллера

клавиатуры

Режим TURBO (разряд 5 вх. порта) – состояние соответствующей кнопки на передней панели ПК;

Тип монитора (разряд 6 вх. порта) определяет наличие в системе цветного (нулевое значение бита) или монохромного монитора (единичное значение бита);

Замок клавиатуры (разряд 7 вх. порта): 0 - клавиатура заблокирована, 1 - клавиатура разблокирована. Заблокировать или разблокировать клавиатуру можно, записав соответствующее значение в старший (7–й) разряд порта 61h или изменив положение замка на передней панели корпуса ПК;

Системный сброс (разряд 0 вых. порта) – управляет программным сбросом ПК;

Gate А20 (разряд 1 вых. порта) – разрешение 20–ти разрядной адресации ОЗУ;

Выходной буфер полон (разряд 4 вых. порта) – признак наличия новых данных в выходном буфере;

Входной буфер пуст (разряд 5 вых. порта) – признак отсутствия необработанных данных во входном буфере;

Синхросигнал клавиатуры (разряд 6 вых. порта) – выход разрешения синхросигналов клавиатуры;

Данные клавиатуры (разряд 7 вых. порта) – выход данных (от контроллера к клавиатуре);

Т0 – вход синхросигнала клавиатуры (разряд 0 тестового порта);

Т1 – вход данных от клавиатуры (разряд 1 тестового порта).

И нтерфейс

контроллер i8042 – клавиатура. Контроллер

i8042 и клавиатура связаны четырехпроводным

экранированным кабелем, включающим

линию питания (+5В), линию заземления,

линии сигнала данных и сигнала

синхронизации (здесь под клавиатурой

будем понимать микроконтроллер,

находящийся в клавиатуре и аналогичный

по структуре с i8042).

нтерфейс

контроллер i8042 – клавиатура. Контроллер

i8042 и клавиатура связаны четырехпроводным

экранированным кабелем, включающим

линию питания (+5В), линию заземления,

линии сигнала данных и сигнала

синхронизации (здесь под клавиатурой

будем понимать микроконтроллер,

находящийся в клавиатуре и аналогичный

по структуре с i8042).

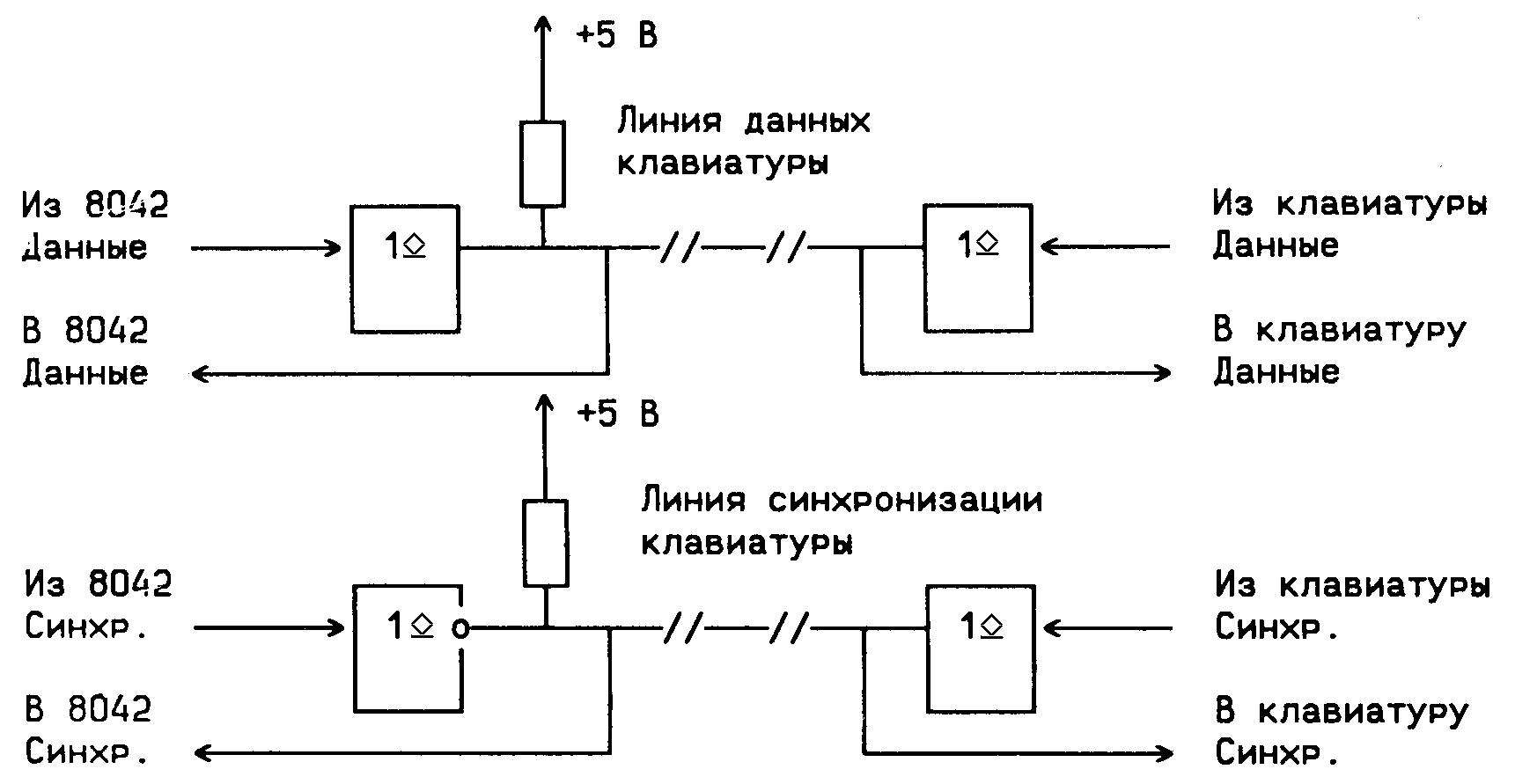

Рис. 2 – Упрощенные схемы цепей данных и синхронизации

Контроллер i8042 и клавиатура взаимодействуют с помощью механизма квитирования, используя для этого линии данных и синхронизации. Интерфейс взаимодействия классифицируется как синхронный последовательный двунаправленный (полудуплексный). На рис. 2 приведены упрощенные схемы цепей данных и синхронизации.

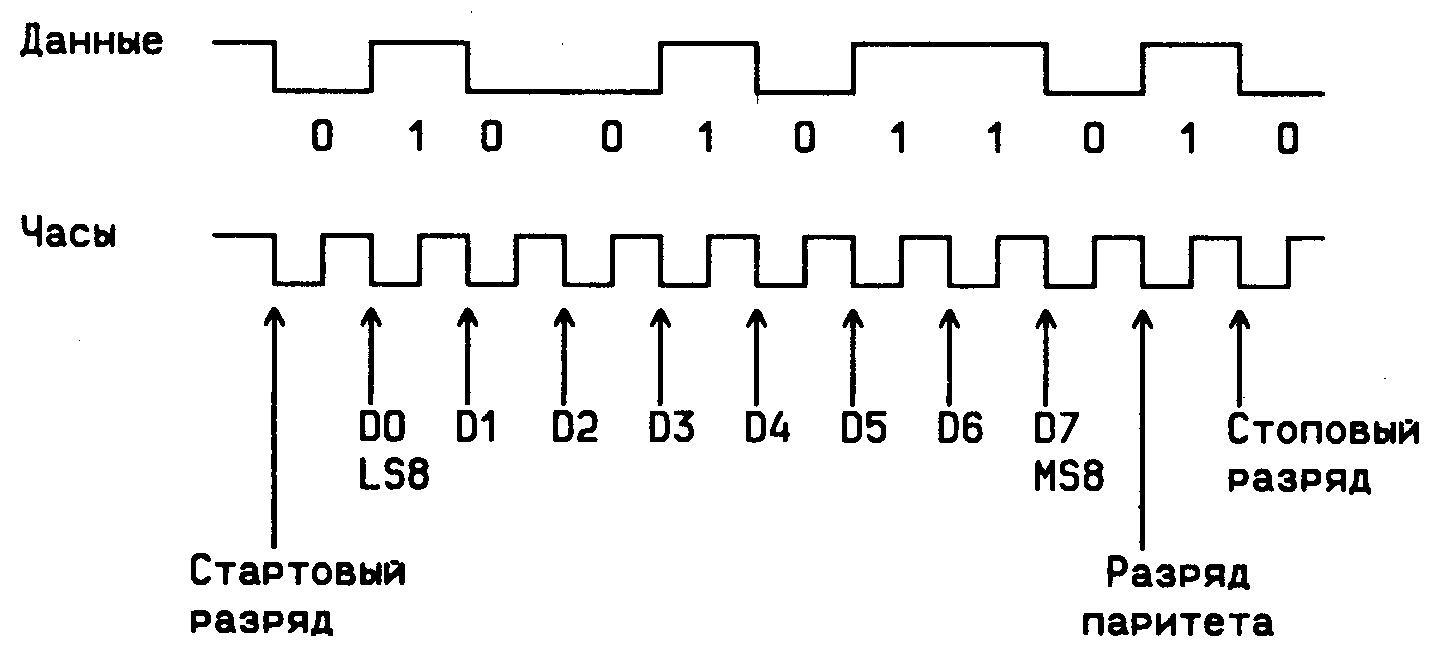

К лавиатура

и контроллер i8042 передают и принимают

данные в 11–разрядном формате (см. рис.

3). Первый разряд – стартовый, за ним

следуют восемь информационных разрядов,

разряд паритета и стоповый разряд. В

конце передачи контроллер клавиатуры

блокирует интерфейс до тех пор, пока

система не примет полученный байт.

лавиатура

и контроллер i8042 передают и принимают

данные в 11–разрядном формате (см. рис.

3). Первый разряд – стартовый, за ним

следуют восемь информационных разрядов,

разряд паритета и стоповый разряд. В

конце передачи контроллер клавиатуры

блокирует интерфейс до тех пор, пока

система не примет полученный байт.

Рис. 3 – Временная диаграмма работы интерфейса

Синхронизирующий сигнал для передачи данных в обоих направлениях обеспечивает клавиатура.

Логически «свободным» линиям синхронизации и данных соответствует высокий уровень сигнала (выходы с ОК). Приоритет на использование линии данных принадлежит .

Перед передачей данных в клавиатуру, контроллер i8042 проверяет состояние линий данных и синхронизации. Если линии заняты передачей от клавиатуры, но клавиатура еще не передала 10–й разряд данных (и, соответственно, 10–й синхроимпульс), то контроллер i8042 может прервать передачу клавиатуры, установив на линии синхронизации низкий уровень. Такое состояние называется «запрет клавиатуры». При этом, байт который пыталась передать клавиатура сохраняется в ее внутреннем буфере и будет передан позднее. Далее, контроллер i8042 разрешает клавиатуру и, одновременно, выставляет требование на передачу – низкий уровень на линии данных. Приняв требование, клавиатура начинает выдавать на линию синхронизации синхроимпульсы, используя которые контроллер осуществляет передачу данных.

Таким образом, клавиатура может начинать передачу только в том случае, если нет запрета на линии синхронизации (т.е. высокий уровень) и нет передачи от контроллера. Выполнив проверку указанных условий, клавиатура может передавать данные (соответственно, синхронизируя их).

Регистр состояния представляет собой 8-разрядный регистр, который доступен по чтению. Он содержит информацию о состоянии контроллера и интерфейсе. Может быть прочитан в любое время. Назначение разрядов регистра состояния приведено в табл. 1.

Таблица 1 – Назначение разрядов регистра состояния

Разряд |

Назначение |

0 |

Выходной буфер полон: 0 – в выходном буфере контроллера нет новых данных; 1 – контроллер поместил данные в выходной буфер (когда содержимое выходного буфера будет прочитано, этот разряд сбросится). |

1 |

Входной буфер полон: 0 – входной буфер контроллера пуст; 1 – во входной буфер помещены новые данные (когда контроллер прочитает содержимое входного буфера, разряд сбросится). |

2 |

Системный флажок: 0 – сброс по включению питания (холодный пуск), 1 – программный сброс (горячий пуск). |

3 |

Команда/данные: 0 – во входном буфере данные, 1 – во входном буфере команда. |

4 |

Ключ блокировки: 0 – защитный замок клавиатуры закрыт, 1 – защитный замок клавиатуры открыт. |

5 |

Тайм-аут передачи: 1 – передача данных, начатая контроллером, не завершена (если передаваемый байт не был синхронизирован в определенный аппаратурой временной промежуток, это ошибка; если передаваемый байт был синхронизирован, но ответ не был получен в запрограммированный промежуток времени, разряды тайм-аута передачи и приема будут установлены в единицу; Если передаваемый байт был синхронизирован, но ответ был получен вместе с ошибкой паритета, разряды тайм-аута передачи и ошибки паритета будут установлены в единицу). |

6 |

Тайм-аут приема: 1 – передача была начата клавиатурой, но не закончилась в запрограммированный период времени (2 мс). |

7 |

Ошибка паритета: 0 – последний байт данных получен от клавиатуры с нечетным паритетом; 1 – последний байт данных получен от клавиатуры с четным паритетом. Клавиатура должна посылать байт с нечетным паритетом. |

Программирование контроллера и клавиатуры. Контроллер использует адресное пространство двух портов – 60h и 64h (регистр состояния – 64h; выходной буфер – 60h; входной буфер – 60h и 64h).

Входной буфер имеет два адреса – 64h для команд, посылаемых контроллеру и 60h – для команд, посылаемых клавиатуре и данных, посылаемых клавиатуре и контроллеру.

В рамках лабораторной работы команды управления контроллером не рассматриваются; их описание можно найти в [1] и [2].

Общая последовательность управления клавиатурой следующая:

чтение и анализ регистра состояния (порт ввода 64h) до тех пор, пока входной буфер буде пуст (т.е. контроллер готов принять байт команды);

запись байта команды во входной буфер (порт вывода 60h).

Данная последовательность выполняется для каждого байта команды клавиатуры.

Описание команд клавиатуры приведено в приложении 1.