- •Лабораторная работа №4 Изучение счётчиков

- •1. Краткие теоретические сведения.

- •2. Счётчики.

- •2.1 Суммирующие двоичные счетчики.

- •2.2 Вычитающие двоичные счетчики.

- •2.3 Реверсивные двоичные счетчики.

- •2.4 Синхронные и асинхронные двоичные счетчики.

- •2.5 Десятичные счетчики.

- •3 Задание к работе

- •Содержание отчета

- •Контрольные вопросы

2.4 Синхронные и асинхронные двоичные счетчики.

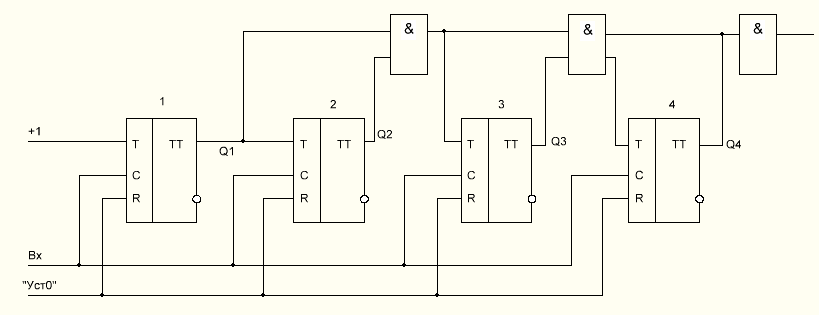

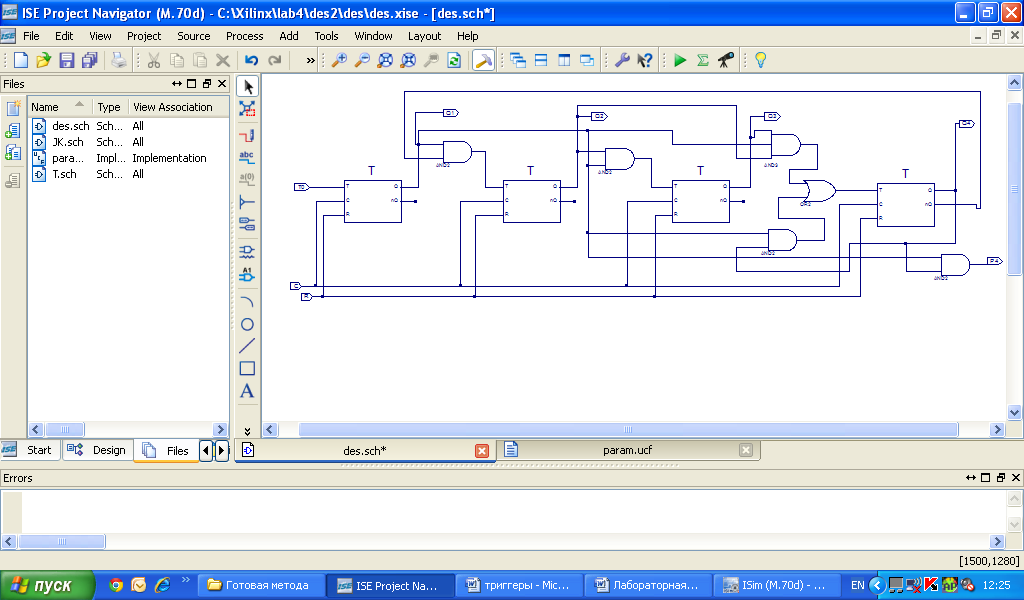

Двоичные счетчики, состояние триггеров которых изменяется одновременно под воздействием сигнала синхронизации на выходах всех триггеров, получили название синхронных. Схема синхронного счетчика со сквозным переносом на Т-триггерах приведена (рис.14), а его условное обозначение (рис.15).

Рис. 14

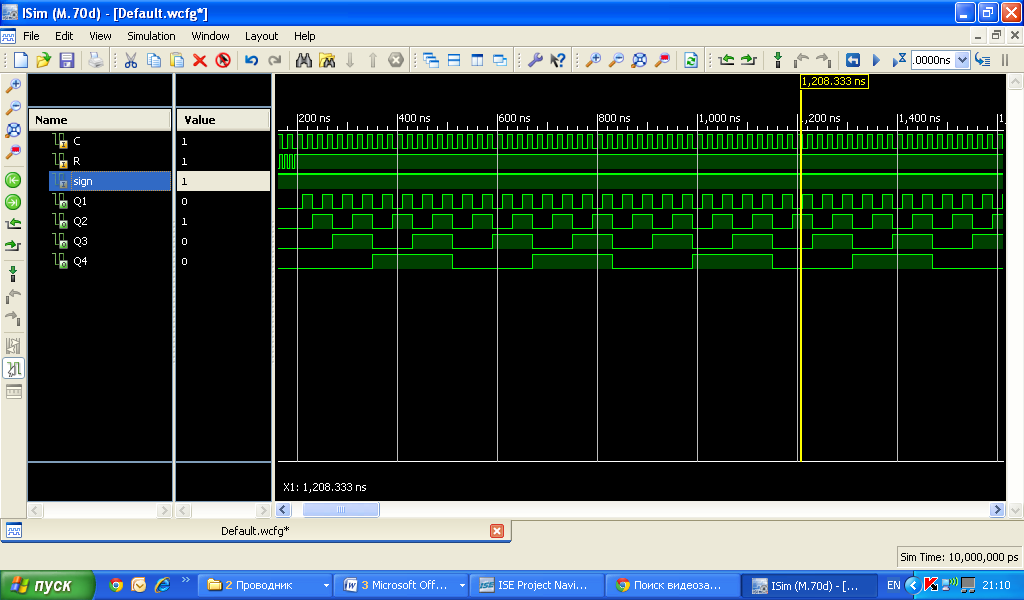

Рис. 15

Синхронные счетчики используются в синхронных цифровых системах. Последовательные цифровые устройства в этих системах обычно зависят друг от друга и управляются от общего источника синхросигналов. В таких условиях нужно, чтобы все триггеры во всех ПЦУ изменяли свое состояние одновременно по сигналу синхронизации, чтобы текущее состояние триггеров использовалось для определения их следующего состояния. Применяемая здесь схема со сквозным переносом легко наращивается простым добавлением схемы И с двумя входами. Однако для определения значения самого правого входа Т n-разрядного счетчика необходимо время, равное времени распространения сигнала через одну схему И, умноженному на п–1.

В асинхронных счетчиках синхронизирующие входы триггеров соединяются с входами соседних триггеров. Поэтому состояние триггера меняется в ответ на изменение состояния соседнего триггера, а не в ответ на воздействие сигнала внешней синхронизации. В асинхронных счетчиках волна изменений состояния распространяется по всей цепочке триггеров, в отличие от синхронных счетчиков, где происходит изменение состояния всех триггеров одновременно.

В триггерах с прямым динамическим входом изменение состояния осуществляется при перепаде уровня от 0 к 1. В асинхронных счетчиках с последовательным переносом вход каждого последующего триггера соединяется с инверсным выходом предыдущего. Сигналы счета поступают на вход Со. С помощью сигнала, поступающего на вход «Уст. 0», счетчик может быть установлен в начальное состояние.

Асинхронные счетчики позволяют обеспечить большую скорость счета. Объясняется это тем, что после переключения первого триггера счетчика на него можно подавать следующий сигнал, не ожидая распространения воздействия от сигнала через весь счетчик. В синхронном счетчике между сигналами на счетный вход должно проходить время, определяемое переключением одного триггера и установлением значений на всех входах Т. С учетом сказанного можно отметить, что все типы суммирующих, вычитающих, реверсивных счетчиков могут быть реализованы в виде как синхронных, так и асинхронных счетчиков.

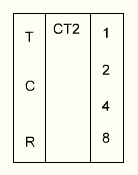

Результат симулирования схемы синхронного двоичного счетчика представлен на рис. 16.

Рис.16. Моделирование работы синхронного двоичного счетчика.

2.5 Десятичные счетчики.

На практике

возникает потребность в построении

счетчиков по произвольному модулю

с числом двоичных разрядов, выбираемых

исходя из условия

с числом двоичных разрядов, выбираемых

исходя из условия

.

.

Это вызывает необходимость исключения лишних состояний в счетчике. Рассмотрим особенности построения таких счетчиков на примере десятичного счетчика.

Для построения

счетчика с

необходимо иметь 4-разрядный двоичный

счетчик, число состояний которого

следует уменьшить с 16 до 10. Счетная

последовательность десятичного счетчика

может быть представлена в двоично-кодированном

десятичном коде (

необходимо иметь 4-разрядный двоичный

счетчик, число состояний которого

следует уменьшить с 16 до 10. Счетная

последовательность десятичного счетчика

может быть представлена в двоично-кодированном

десятичном коде ( – 8421), в котором каждая десятичная цифра

кодируется 4-разрядным двоичным числом.

Счетная последовательность суммирующего

десятичного счетчика в этом случае

совпадает с двоичной последовательностью

от 0000 до 1001, после чего следует 0, и

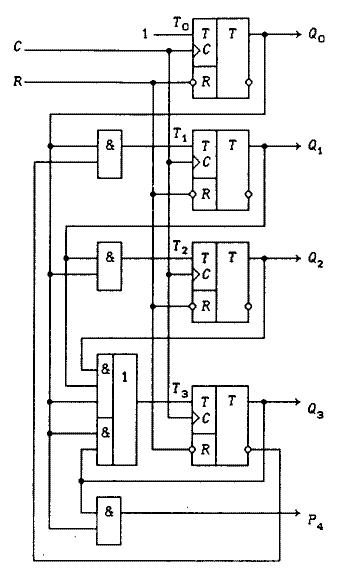

последовательность повторяется. Схема

десятичного счетчика на T-триггерах

с входной логикой (рис.17).

– 8421), в котором каждая десятичная цифра

кодируется 4-разрядным двоичным числом.

Счетная последовательность суммирующего

десятичного счетчика в этом случае

совпадает с двоичной последовательностью

от 0000 до 1001, после чего следует 0, и

последовательность повторяется. Схема

десятичного счетчика на T-триггерах

с входной логикой (рис.17).

Рис. 17

Десятичный счетчик

представляет собой 4-разрядный двоичный

суммирующий счетчик с параллельным

переносом, схема которого дополнена

обратной связью с выхода

.

Кроме того, выход

соединен со всеми выходами К триггера

4. После приема в счетчик восьми

сигналов на его выходах

.

Кроме того, выход

соединен со всеми выходами К триггера

4. После приема в счетчик восьми

сигналов на его выходах

установятся соответственно уровни

0001. При этом на вход J-триггера 2 будет

подаваться нулевой уровень с выхода

.

С приходом девятого сигнала на выходе

триггера 1 установится единичный уровень.

С приходом десятого сигнала триггер 1и

триггер 4 перейдут в нулевое состояние.

Триггеры 2 и 3 сохранят нулевое состояние.

Десятым сигналом счетчик установится

в начальное состояние, и процесс счета

будет повторяться. Закон функционирования

десятичного счетчика приведен в (табл.

3).

установятся соответственно уровни

0001. При этом на вход J-триггера 2 будет

подаваться нулевой уровень с выхода

.

С приходом девятого сигнала на выходе

триггера 1 установится единичный уровень.

С приходом десятого сигнала триггер 1и

триггер 4 перейдут в нулевое состояние.

Триггеры 2 и 3 сохранят нулевое состояние.

Десятым сигналом счетчик установится

в начальное состояние, и процесс счета

будет повторяться. Закон функционирования

десятичного счетчика приведен в (табл.

3).

Таблица 3

Номер входного импульса |

Вх |

Q4t |

Q3t |

Q2t |

Q1t |

Q4t+1 |

Q3t+1 |

Q2t+1 |

Q1t+1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

2 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

3 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

4 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

5 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

6 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

7 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

8 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

9 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

10 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

В общем случае для построения счетчиков по произвольному модулю в схему соответствующего двоичного счетчика вводится обратная связь для исключения лишних состояний. Двоичный суммирующий или вычитающий счетчик переключается до установки некоторого значения . Это состояние выявляется специальной схемой, на выходе которой формируется сигнал установки счетчика в нулевое состояние. Схемы счетчика по модулю наиболее просты при использовании двоичных счетчиков с последовательным переносом. Рассмотрим построенную таким способом схему десятичного счетчика (рис.18).

Рис. 18

Работа счетчика

заключается в следующем. Начиная с

исходного нулевого состояния, счетчик

принимает последовательность сигналов

счета. Триггер 5 находится в состоянии

0. Элемент И фиксирует момент прихода

десятого сигнала (комбинация уровней

на выходах триггеров

1010) и переводит триггер 5

в состояние

1. До прихода одиннадцатого сигнала все

разряды счетчика переводятся в нулевое

состояние установочным сигналом с

выхода

.

После поступления десяти сигналов

счетчик возвращается в исходное

положение. Одиннадцатый сигнал

положительным перепадом возвращает

триггер 5 в исходное состояние 0.

Использование RS-триггера 5 обусловлено

наличием на входе элемента И опасных

состязаний из-за нарушений в работе

счетчика. Триггер 5, переключившись,

сохраняет на выходе единичный уровень

до прихода следующего сигнала счета.

.

После поступления десяти сигналов

счетчик возвращается в исходное

положение. Одиннадцатый сигнал

положительным перепадом возвращает

триггер 5 в исходное состояние 0.

Использование RS-триггера 5 обусловлено

наличием на входе элемента И опасных

состязаний из-за нарушений в работе

счетчика. Триггер 5, переключившись,

сохраняет на выходе единичный уровень

до прихода следующего сигнала счета.

Описание выводов десятичного счетчика приведено на рис.19

Рис.19

Принцип работы десятичного счетчика прекрасно показывает рис.20, демонстрирующий сигналы в проводниках десятичного счетчика.

Рис. 20. Результат симулирования работы десятичного счетчика.

3. Описание цифрового устройства с помощью языка VHDL на примере десятичного счетчика.

Альтернативой графическому вводу схемы цифрового устройства является описание его поведения на одном из языков описания аппаратуры. Существует множество таких языков (Verilog, AHDL, VHDL). Преимущества VHDL становяться очевидными только при разработке сложных проектов, на примере десятичного счетчика это не столь очевидно. Создание области написания VHDL-программы описывалось в предыдущих работах, поэтому останавливаться на этом нет смысла.

Особенностью представления десятичного счетчика на языке описания аппаратуры в том, что его можно реализовать как счетную последовательность чисел. Эта последовательность начинается с 0. Очередное число в этой последовательности получается прибавлением единицы к предыдущему числу. После того как последовательность доходит до максимального числа в данном случае для десятичного счетчика это 9 она снова проходит через 0 и повторяется. Каждому состоянию счетчика соответствует число в счетной последовательности от 0 до 9.

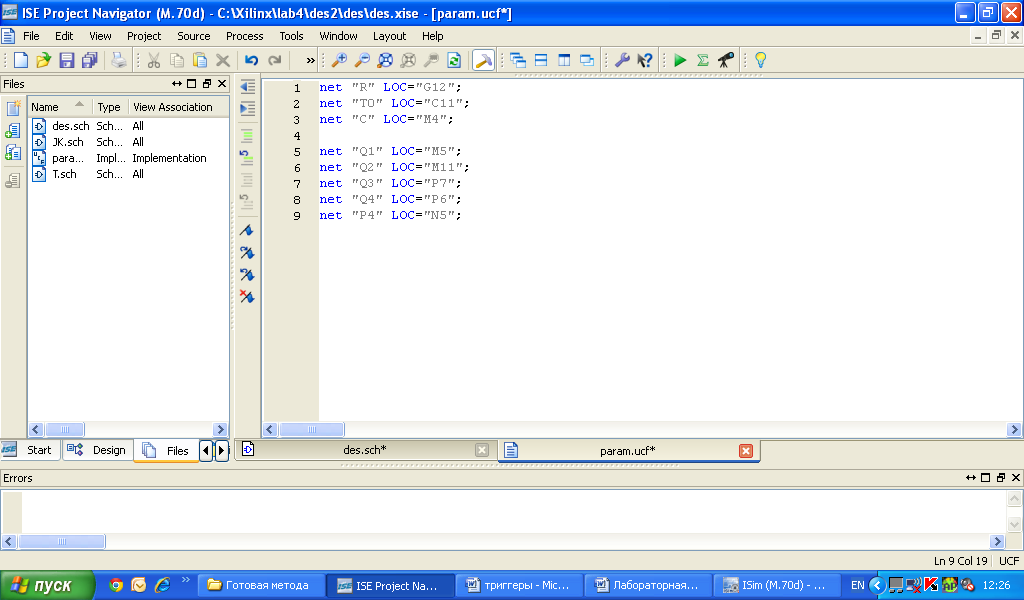

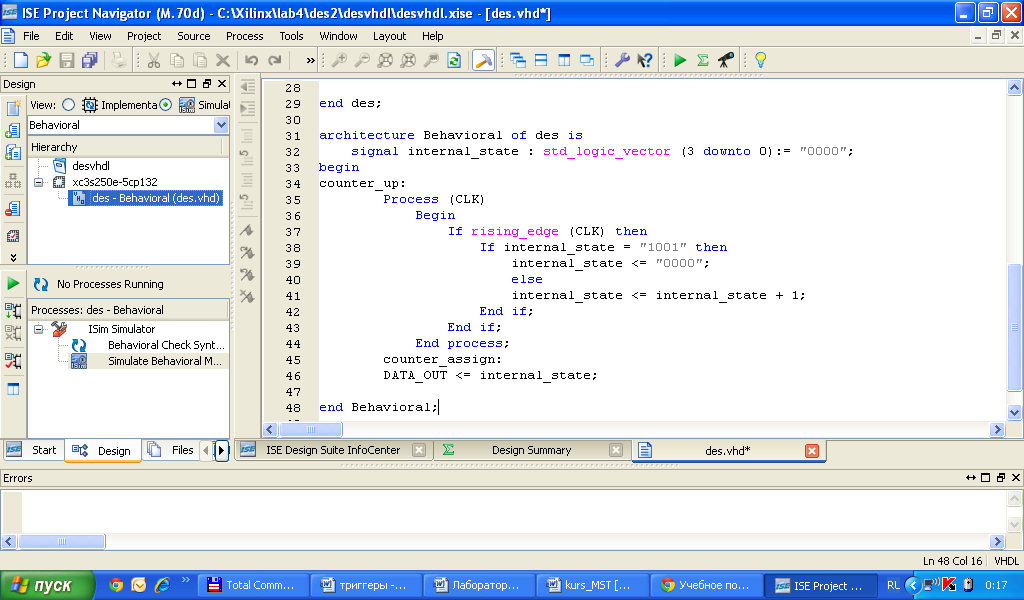

В первых строках программ описываются используемые библиотеки, а также обозначаются входы и выходы схемы (рис.21).

Рис 21. Описание используемых библиотек и входов и выходов устройства.

В следующих строках кода программы описывается непосредственно алгоритм работы, который представляется структурой if… else, где определяющим условием остановки дальнейшего счета является равенство значению “1001”, которое в десятеричной системе соответствует 9. То есть начиная со значения “0000” на выходах устройства происходит добавление единицы до тех пор, пока на выходах не сформируется значение “1001”, после чего счетчик сбрасывается в нулевое состояние и отсчет начинается снова (рис.22).

Рис. 22. VHDL-программа.

Таким образом, десятичный счетчик на языке VHDL можно представить как последовательное прибавление 1 в младший разряд четырехразрядного устройства. Увеличение на единицу ограничивается условием, что максимально возможное значение счета равно 9, после чего счет начинается сначала. Основываясь на десятеричном счетчике можно создать суммирующий двоичный счетчик (а так же другие счетчики, описанные в данной лабораторной работе) убрав ограничение максимального значения счета, таким образом, суммирование будет ограничиваться лишь разрядностью самого устройства.