- •Методические указания к выполнению лабораторных работ по электротехническим дисциплинам

- •6.050502 – Инженерная механика,

- •6.050702 – Автомобильный транспорт

- •Часть 4

- •Введение

- •Лабораторная работа №21 исследование одиночного усилительного каскада

- •21.1. Цель работы

- •21.2. Теоретические сведения

- •21.3. Порядок выполнения работы

- •21.4. Содержание отчета

- •21.5. Контрольные вопросы

- •Лабораторная работа №22 Элементная база и принципы работы электронной лаборатории Electronics Workbench

- •22.1. Цель работы

- •22.2. Теоретические сведения

- •22.3. Порядок выполнения работы

- •21.4. Содержание отчета

- •21.5. Контрольные вопросы

- •Лабораторная работа №23 исследование дифференциального усилителя на биполярных транзисторах

- •23.1. Цель работы

- •23.2. Теоретические сведения

- •23.3. Порядок выполнения работы

- •Лабораторная работа №24 исследование арифметических блоков аналоговых вычислительных устройств

- •24.3. Порядок выполнения работы

- •24.4. Содержание отчета

- •24.5. Контрольные вопросы

- •Лабораторная работа №25 исследование дифференцирующих и интегрирующих устройств аналоговых вычислительных машин

- •25.1. Цель работы

- •25.2. Теоретические сведения

- •25.3. Порядок выполнения работы

- •25.4. Содержание отчета

- •25.5. Контрольные вопросы

- •Лабораторная работа №26 исследование базовых логических элементов цифровых вычислительных машин

- •26.1. Цель работы

- •26.2. Теоретические сведения

- •26.3. Порядок выполнения работы

- •26.4. Содержание отчета

- •26.5. Контрольные вопросы

- •Лабораторная работа №27 исследование основных цифровых комбинационных устройств (дешифратора, демультиплексера, мультиплексера)

- •27.1. Цель работы

- •27.2. Теоретические сведения

- •27.3. Порядок выполнения работы

- •27.4. Содержание отчета

- •27.5. Контрольные вопросы

- •Лабораторная работа №28 исследование триггеров, счетчиков импульсов и регистров сдвига

- •28.1. Цель работы

- •28.2. Теоретические сведения

- •28.3. Порядок выполнения работы

- •28.4. Содержание отчета

- •28.5. Контрольные вопросы

- •Лабораторная работа №29 исследование аналого-цифровых и цифро-аналоговых преобразователей

- •29.1. Цель работы

- •29.2. Теоретические сведения

- •29.3. Порядок выполнения работы

- •29.4. Содержание отчета

- •29.5. Контрольные вопросы

- •Лабораторная работа №30 исследование четырехразрядного параллельного сумматора

- •30.1. Цель работы

- •30.2. Теоретические сведения

- •30.3. Порядок выполнения работы

- •30.4. Содержание отчета

- •30.5. Контрольные вопросы

- •Лабораторная работа №31 изучение учебно-отладочного устройства

- •31.1. Цель работы.

- •31.2. Самостоятельная работа

- •31. 3. Содержание и порядок выполнения лабораторной работы

- •31.4. Содержание отчета

- •31.5. Контрольные вопросы

- •Лабораторная работа №32 изучение арифметических команд и команд пересылки данных

- •32.1. Цель работы.

- •32.2. Самостоятельная работа

- •32.3. Содержание лабораторной работы

- •32.4. Порядок выполнения работы

- •32.5. Содержание отчета

- •32.6. Контрольные вопросы

- •Лабораторная работа №33 обработка массивов информации. Организация циклов

- •33.1. Цель работы.

- •33.2. Самостоятельная работа

- •33.3. Содержание лабораторной работы

- •33.4. Порядок выполнения работы

- •33.5. Содержание отчета

- •33.6. Контрольные вопросы

- •Библиографический список

- •Приложение в Варианты заданий к лабораторной работе 33

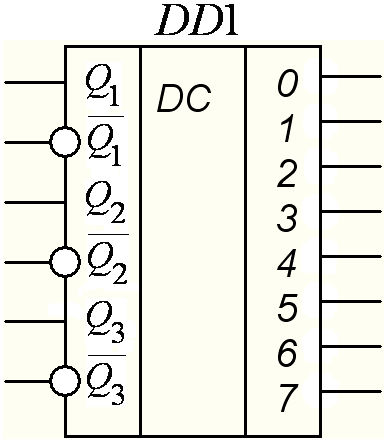

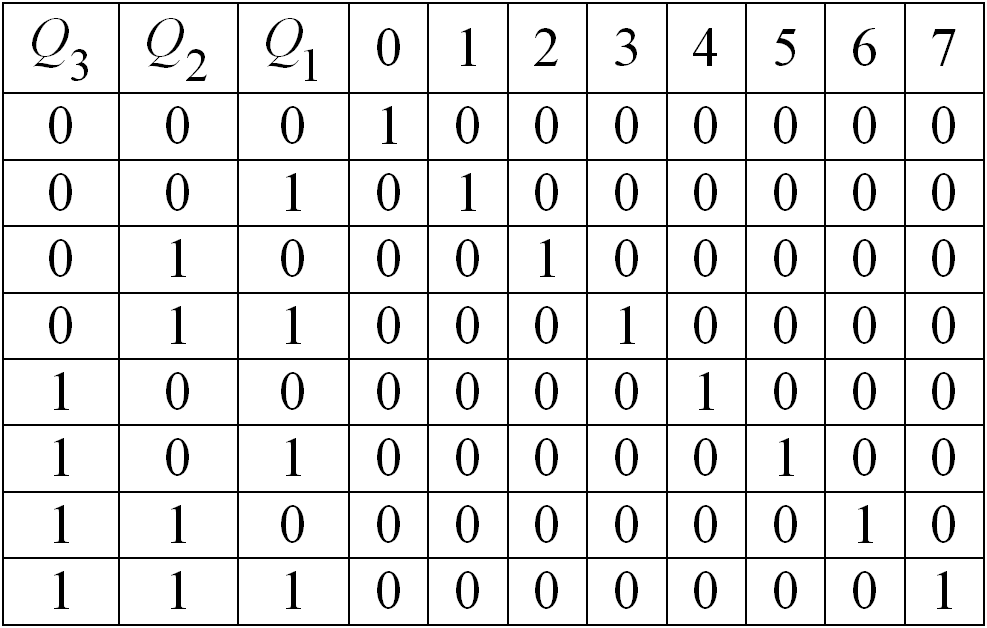

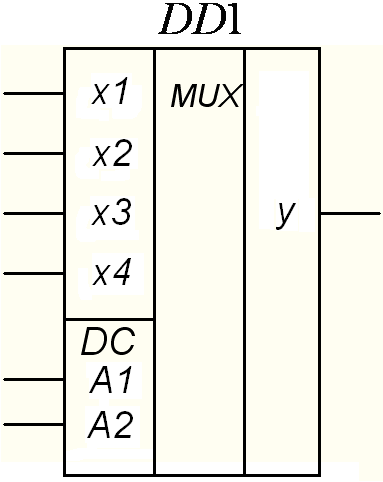

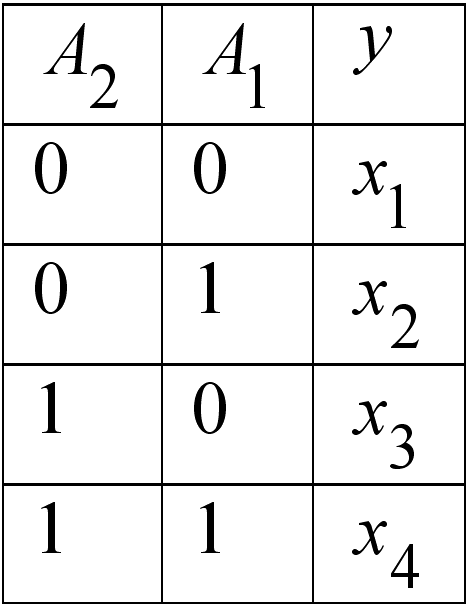

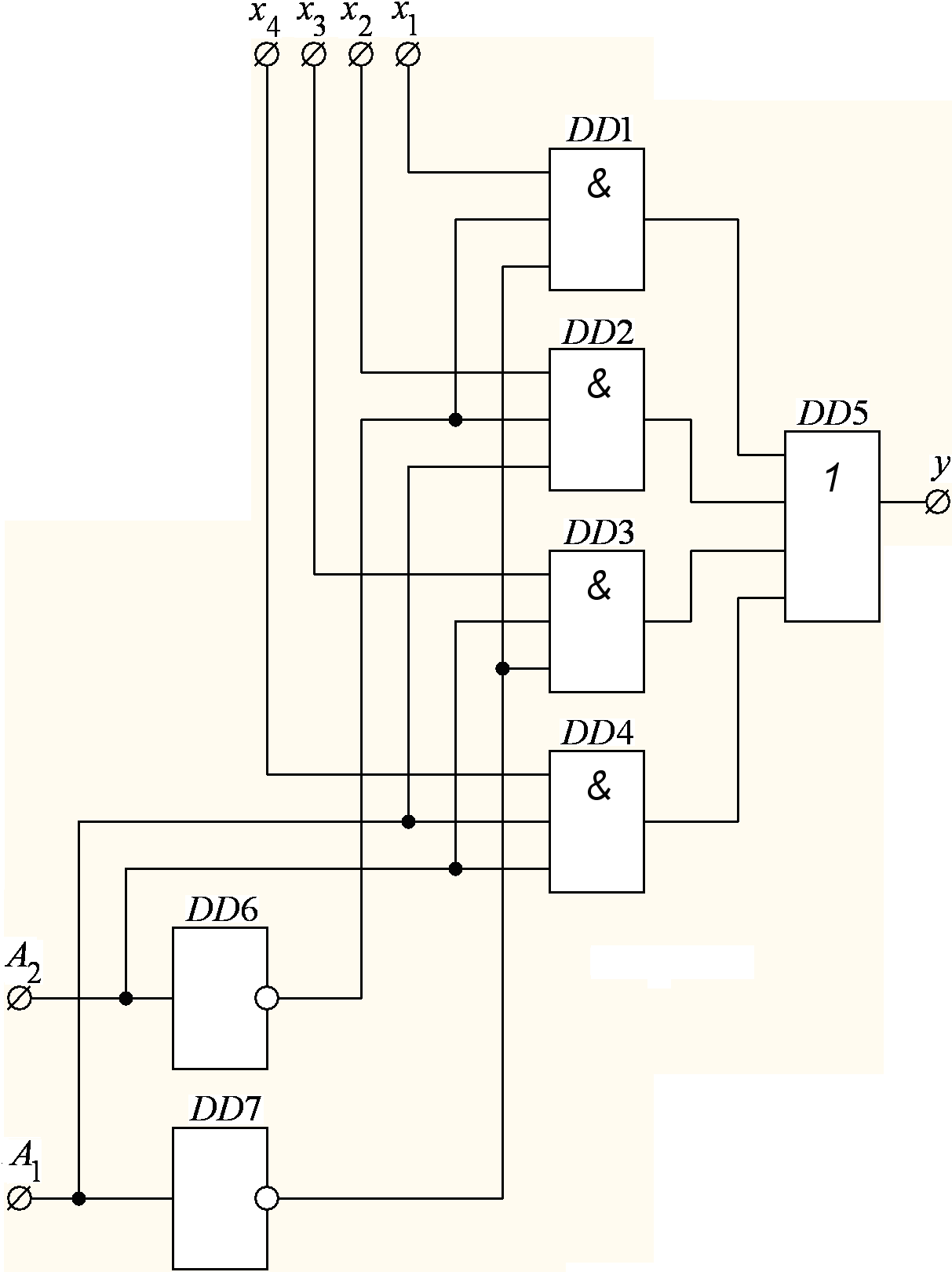

27.3. Порядок выполнения работы

1. Подключить к лабораторному стенду плату П-4.

2. Используя трафарет технологической карты IV-1, манипулируя переключателями, составить таблицу истинности дешифратора.

3. Манипулируя переключателями SA1…SA3 и нажимая и отпуская кнопку SB2, подавать импульсный информационный сигнал на вход демультиплексера. Состояние выходов наблюдать с помощью светодиодов HL1…HL8. Составить таблицу истинности демультиплексера.

4. Используя трафарет технологической карты IV-3, манипулируя переключателями и наблюдая выходной сигнал с помощью светодиодов, составить таблицу истинности мультиплексера.

27.4. Содержание отчета

1. Схемы экспериментальных установок.

2. Таблицы истинности, условные обозначения и названия устройств, исследованных в лабораторной работе.

3. Выводы.

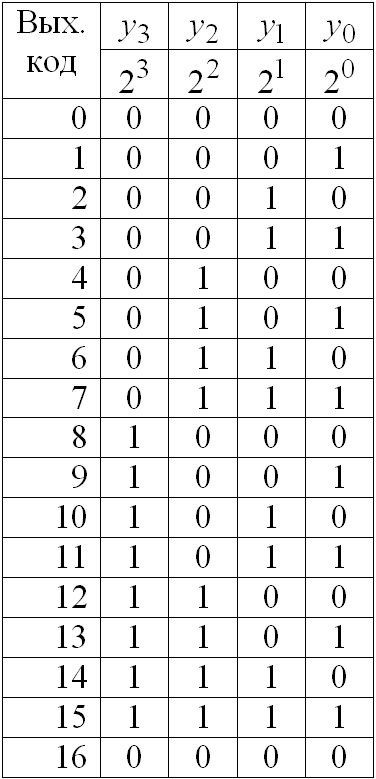

а)

б) |

в) |

Рисунок 27.1 – Условное обозначение, таблица истинности и структура двоично-десятичного дешифратора

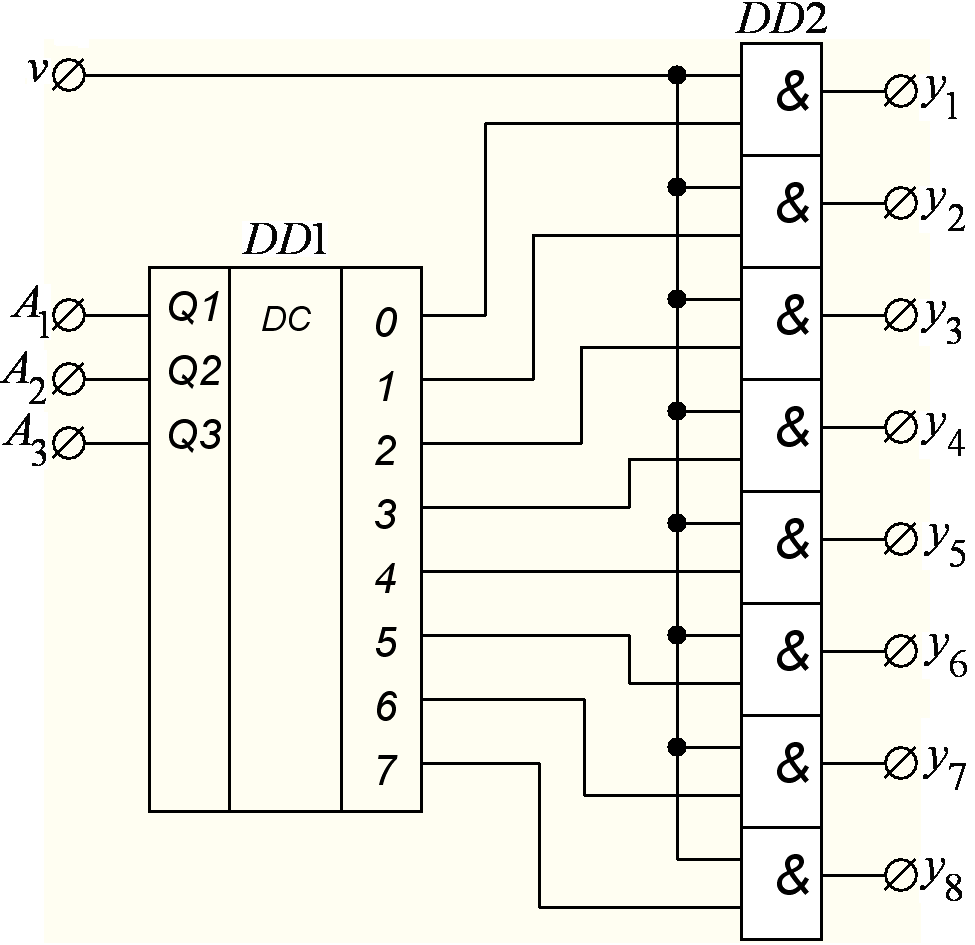

а)

б) |

в) |

Рисунок 27.2 - Условное обозначение, таблица истинности и структура мультиплексора

а) |

б) |

Рисунок 27.3 - Таблица истинности и структура демультиплексора

27.5. Контрольные вопросы

1. Приведите условное обозначение и поясните назначение дешифратора.

2. Изобразите структурную схему дешифратора и приведите его таблицу истинности.

3. Приведите условное обозначение и поясните назначение мультиплексера.

4. Изобразите структурную схему мультиплексера и приведите его таблицу истинности.

5. Приведите структурную схему демультиплексера и поясните его назначение.

6. Приведите таблицу истинности демультиплексера.

Лабораторная работа №28 исследование триггеров, счетчиков импульсов и регистров сдвига

28.1. Цель работы

1. Изучить назначение, структуру и принципы работы триггеров, счетчиков и регистров сдвига.

28.2. Теоретические сведения

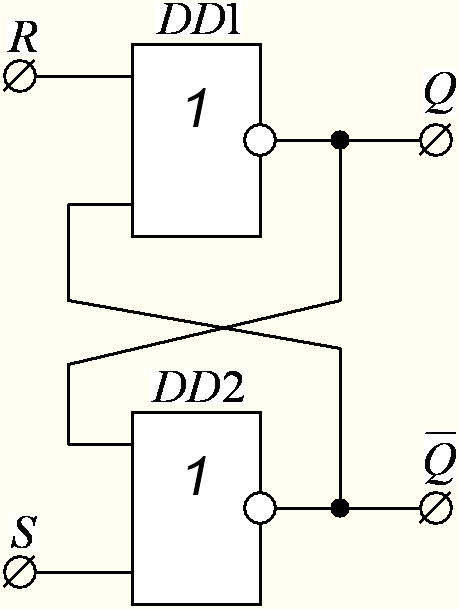

Триггер – это цифровое устройство, имеющее два устойчивых состояния.

Триггеры используются при построении устройств последовательной логики – счетчиков импульсов, регистров сдвига, элементов оперативной памяти.

Триггеры строятся на основе двух логических элементов, охваченных положительными обратными связыми.

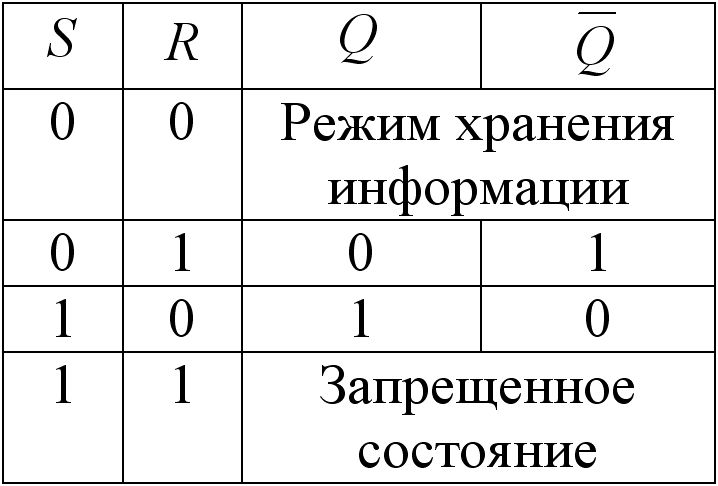

Простейшими

триггерами являются RS-триггеры.

Схема RS-триггера,

составленного из элементов «ИЛИ-НЕ»,

его условное обозначение и таблица

истинности показаны на рисунках 28.1, а,

б, и в, соответственно. На входы триггера

поступают два входных сигнала S

(Set)

– установка и R

(Reset)

– сброс. На выходах триггера формируются

два выходных сигнала

![]() и

и

![]() .

Если S=1

и R=0,

то Q=1,

.

Если S=1

и R=0,

то Q=1,

![]() .

Если R=S=0,

то состояние выходных сигналов

сохраняется, поэтому RS-триггер

можно использовать для запоминания

иформации. Если R=S=1,

то оба выходных сигнала равны нулю;

однако, тогда состояние выходных сигналов

не будет определено, если в какой-либо

момент оба входных сигнала одновременно

станут равными нулю. Поэтому комбинация

R=S=1

является запрещенной комбинацией.

.

Если R=S=0,

то состояние выходных сигналов

сохраняется, поэтому RS-триггер

можно использовать для запоминания

иформации. Если R=S=1,

то оба выходных сигнала равны нулю;

однако, тогда состояние выходных сигналов

не будет определено, если в какой-либо

момент оба входных сигнала одновременно

станут равными нулю. Поэтому комбинация

R=S=1

является запрещенной комбинацией.

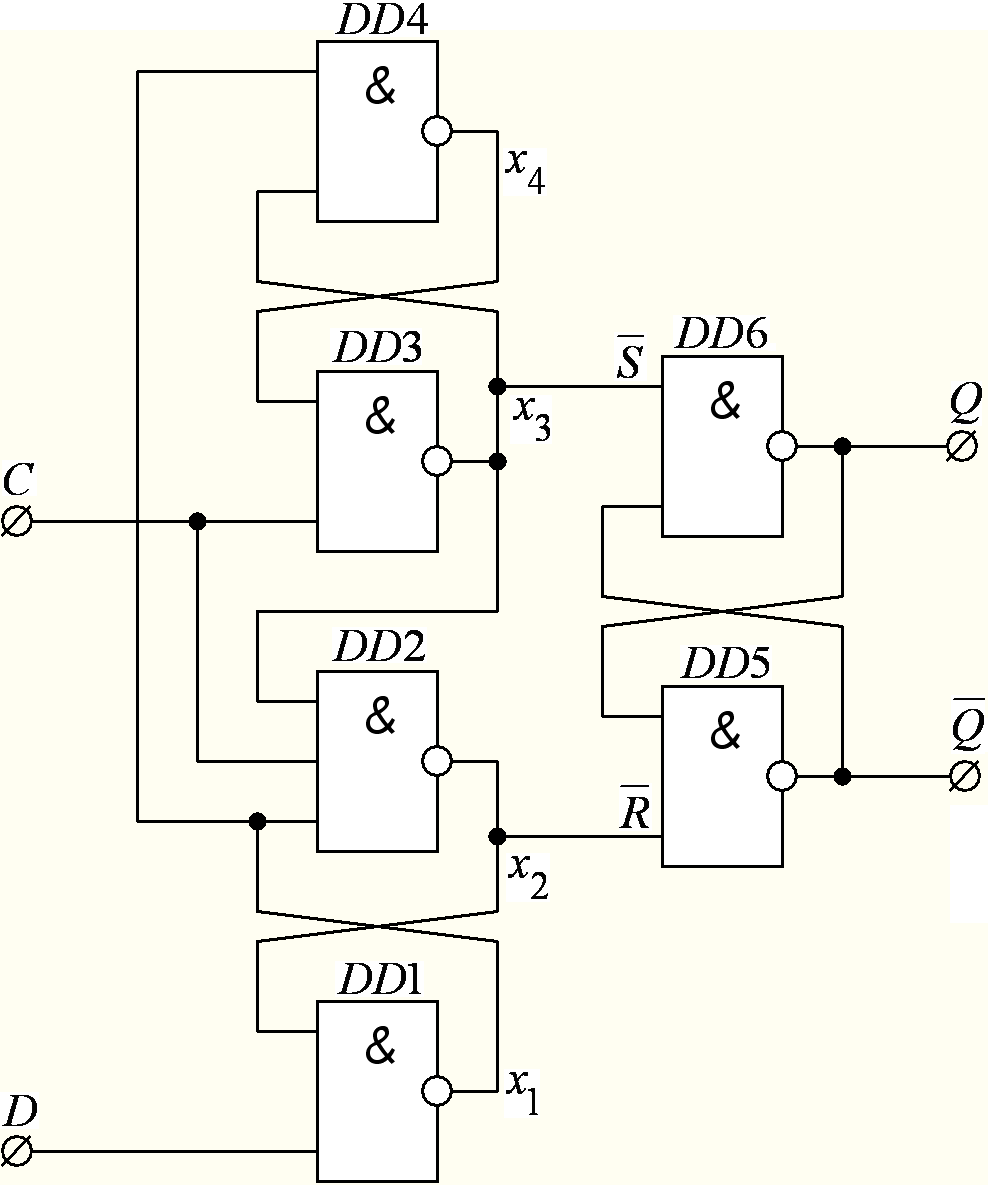

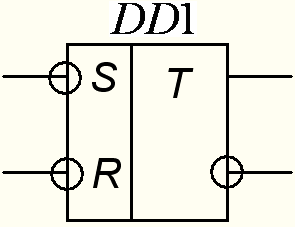

Схема RS-триггера, составленного на элементах «И-НЕ», его условное обозначение и таблица истинности показаны на рисунках 28.2, а, б и в, соотвественно.

Если состояние входных сигналов RS-триггера изменяется, то практически мгновенно изменяется состояние его выходных сигналов. Иными словами, в RS-триггера имеет место сквозная передача сигнала с входа на выход.

а) б) в)

Рисунок 28.1 – RS-триггер на элементах «ИЛИ-НЕ» и его таблица истинности

а) б) в)

Рисунок 28.2 – RS-триггер на элементах «ИЛИ-НЕ» и его таблица истинности

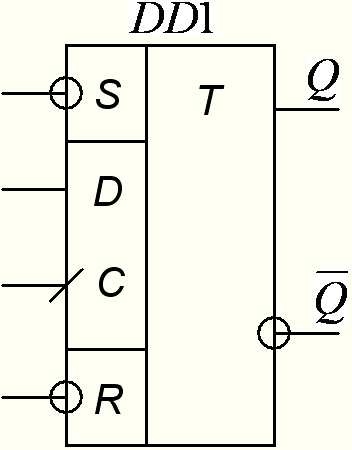

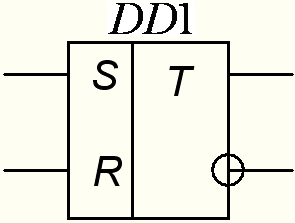

На основе RS-триггера может быть создан динамический D-триггер.

Динамическим триггером называется триггер, в котором отсутствует сквозная передача сигнала с входа на выход. Помимо входов установки S и сброса R, он имеет один информационный вход D (вход данных) и один тактовый вход C, на который подается последовательность тактовых импульсов. Динамический D-триггер можно получить, блокируя входы в тот момент времени, когда считываемая информация передается на выход. При этом различают два типа таких триггеров: триггеры, в которых передача информации происходит на переднем фронте тактового импульса, и триггеры, в которых передача информации осуществляется на отрицательном фронте этого импульса.

Принципиальная схема динамического D-триггера на элементах «И-НЕ» и его условное обозначение показаны на рисунке 28.3.

Рассмотрим структуру D-триггера, управляемого положительным фронтом (рисунок 28.3, а).

Если

сигнал С равен нулю, то

![]() .

При этом выходной триггер, собранный

на элементах DD5

и DD6,

работает в режиме хранения информации.

Пока С=0,

и

.

При этом выходной триггер, собранный

на элементах DD5

и DD6,

работает в режиме хранения информации.

Пока С=0,

и

![]() ,

,

![]() .

Это означает, что всегда в одном из двух

вспомогательных триггеров оба выходных

сигнала равны 1. Это запрещенное состояние

исчезает, когда тактовый сигнал С примет

единичное значение. Устанавливающийся

при этом выходной сигнал определяется

другим вспомогательным триггером,

который находится в незапрещенном

состоянии. Из этого следует, что при

D=0,

.

Это означает, что всегда в одном из двух

вспомогательных триггеров оба выходных

сигнала равны 1. Это запрещенное состояние

исчезает, когда тактовый сигнал С примет

единичное значение. Устанавливающийся

при этом выходной сигнал определяется

другим вспомогательным триггером,

который находится в незапрещенном

состоянии. Из этого следует, что при

D=0,

![]() остается в 1,

переходит в 0; при D=1,

остается в 1,

переходит в 0.

остается в 1,

переходит в 0; при D=1,

остается в 1,

переходит в 0.

а) |

б) |

Рисунок 28.3 – Принципиальная схема и условное обозначение динамического D-триггера

Сигнал, принимающий нулевое значение определяет состояние оконечного триггера, то есть во время появления положительного фронта тактирующего импульса выполняется равенство Q=D.

Рассмотрим,

как производится последующее запирание

входов данной схемы. После передачи

информации оба вспомогательных триггера

находятся в незапрещенном состоянии.

Но в этом случае они блокируют друг

друга, так что все последующие изменения

сигнала D

не вызывают изменение сигналов выходного

триггера: при

![]() заблокирован DD1

и, следовательно

заблокирован DD1

и, следовательно

![]() ;

при

;

при

![]() заблокированы DD2

и DD4

и, следовательно,

заблокированы DD2

и DD4

и, следовательно,

![]() .

Новая информация запишется только

тогда, когда при С=0 один из двух

вспомогательных триггеров перейдет в

запрещенное состояние.

.

Новая информация запишется только

тогда, когда при С=0 один из двух

вспомогательных триггеров перейдет в

запрещенное состояние.

Таблица истинности и временные диаграммы, поясняющие работу динамического D-триггера показаны на рисунке 28.4.

а) |

б) |

Рисунок 28.4 – Таблица истинности и временные диаграммы, поясняющие работу динамического D-триггера

Счетчик импульсов – это цифровое устройство, предназначенное для подсчета числа импульсов, поступивших на его вход.

В

качестве счетчиков импульсов можно

использовать произвольную схему,

установив для нее в определенных границах

однозначное соответствие между числом

поступивших имульсов и состоянием

выходных переменных. Так как каждая

выходная переменная может принимать

лишь два значения, то для n

выходных переменных существует

![]() возможных состояний. Обычно используют

двоичное представление зависимости

между числом поступивших импульсов и

выходным кодом счетчика.

возможных состояний. Обычно используют

двоичное представление зависимости

между числом поступивших импульсов и

выходным кодом счетчика.

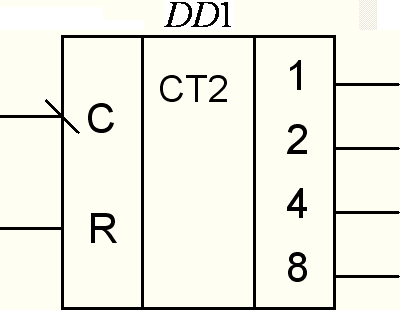

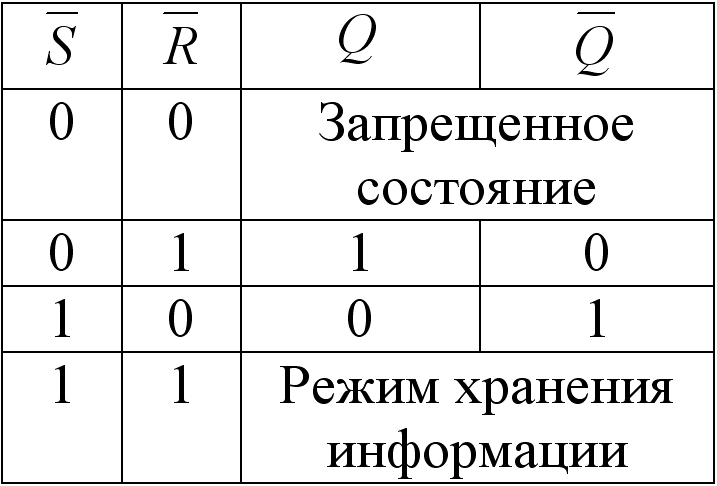

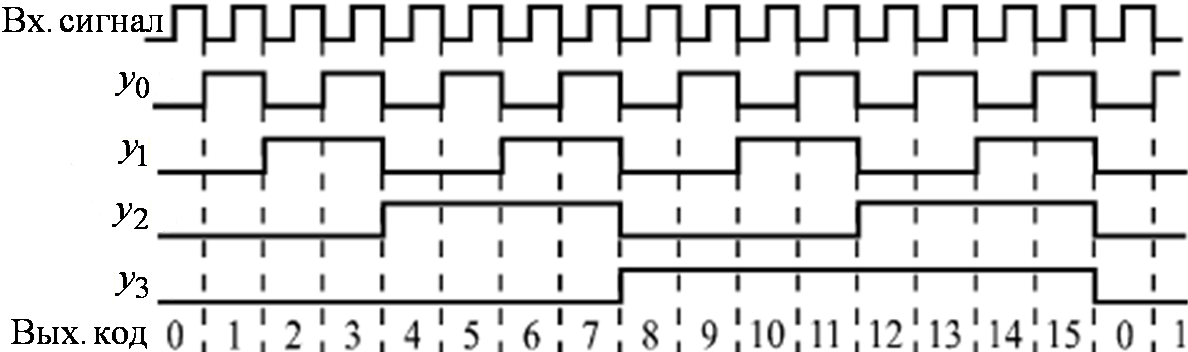

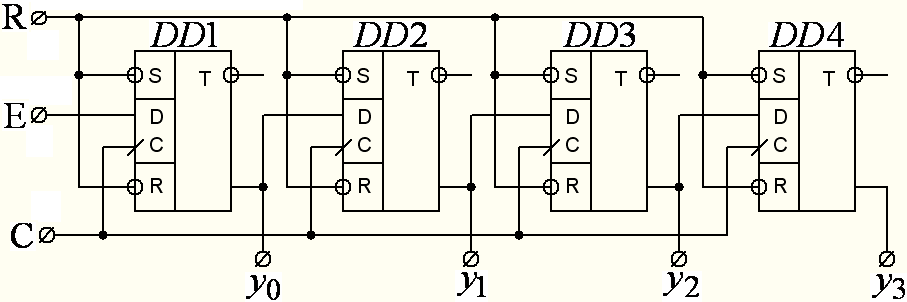

Принципиальная схема простейшего четырехразрядного двоичного асинхронного счетчика на D-триггерах, временные диаграммы сигналов на его выводах, его условное обозначение и таблица истинности показаны на рисунке 28.5. Счетчик имеет счетный вход С, на который подается последовательность импульсов, подлежащих счету, и вход сброса R. Если на вход R подан логический ноль, то на выходах счетчика появляются логические нули (счетчик обнуляется). Если на вход R подана логическая единица, то счетчик может считать входные импульсы.

Регистры сдвига представляют собой несколько D-триггеров (обычно от 4 до 16), соединенных между собой в последовательную цепочку (выход каждого предыдущего триггера соединен с входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Регистры сдвига могут использоваться как элементы памяти и как линии задержки. Память регистра сохраняется до момента выключения питания схемы.

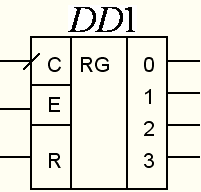

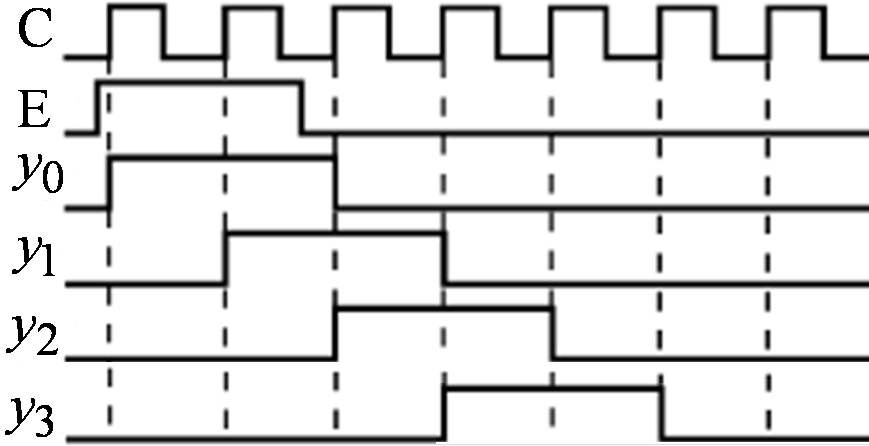

Принципиальная схема и условное обозначение регистра сдвига показаны на рисунках 28.6, а, б, соответственно. Временные диаграммы, поясняющие работу регистра сдвига изображены на рисунке 28.6, в. Регистр сдвига имеет вход данных E, вход сброса R и вход синхронизации С.

а)

б)

в) |

г) |

Рисунок 28.5 - Четырехразрядный двоичный асинхронный счетчик, временные диаграммы сигналов на его выводах, таблица истинности, условное обозначение

Если на вход сброса подан логический нуль, то регистр обнуляется.

Если на вход R подана логическая единица, то регистр способен принимать и обрабатывать входной сигнал, поступающий на вход Е. В данном случае, входной сигнал последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С.

а)

б) в)

Рисунок 28.6 – Принципиальная схема, условное обозначение и временные диаграммы, поясняющие работу регистра двига