- •Содержание

- •1.Введение

- •2. Проектирование логической функции

- •2.1Проектирование логической функции с использованием логических интегральных микросхем

- •2.1.1Минимизация логической функции

- •2.1.2 Проектирование логической функции с использованием любых микросхем серии к155

- •2.1.3 Проектирование логической функции с использованием микросхем к155ла3

- •Печатная плата

- •2.2 Проектирование логической функции с использованием дешифратора к155ид3

- •2.3Проектирование логической функции с использованием мультиплексора к155кп7

- •3. Проектирование делителя частоты на микросхемах к155ие7

- •3.1 Методика проектирования на микросхемах серии к155ие7

- •3.2 Проектирование делителя частоты на микросхемах к155ие6

- •3.3 Методика проектирования на микросхемах серии к155ие6

- •Проектирование системы управления по циклограмме

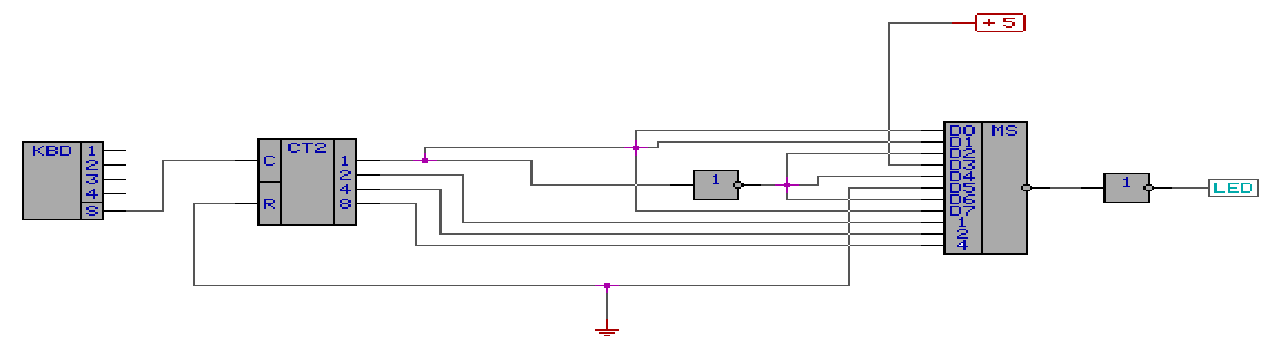

2.3Проектирование логической функции с использованием мультиплексора к155кп7

Мультиплексор К155КП7 имеет восемь информационных входов D0 - D7, три адресных входа 1, 2, 4 .У микросхемы один выход - инверсный. Если на входе стробирования лог. 1, на прямом выходе 0 независимо от сигналов на других входах. Если на входе стробирования лог. 0, сигнал на прямом выходе повторяет сигнал на том входе, номер которого совпадает с десятичным эквивалентом кода на входах 1,2,4 мультиплексора. На инверсном выходе сигнал всегда противофазен сигналу на прямом выходе.

Таблица

истинности для проектирования с помощью

мультиплексора

X4 |

X3 |

X2 |

X1 |

F |

№D |

Вход |

0 |

0 |

0 |

0 |

X |

D0 |

|

0 |

0 |

0 |

1 |

1 |

||

0 |

0 |

1 |

0 |

0 |

D1 |

|

0 |

0 |

1 |

1 |

1 |

||

0 |

1 |

0 |

0 |

X |

D2 |

|

0 |

1 |

0 |

1 |

0 |

||

0 |

1 |

1 |

0 |

1 |

D3 |

1 |

0 |

1 |

1 |

1 |

1 |

||

1 |

0 |

0 |

0 |

X |

D4 |

|

1 |

0 |

0 |

1 |

0 |

||

1 |

0 |

1 |

0 |

0 |

D5 |

0 |

1 |

0 |

1 |

1 |

0 |

||

1 |

1 |

0 |

0 |

1 |

D6 |

|

1 |

1 |

0 |

1 |

0 |

||

1 |

1 |

1 |

0 |

0 |

D7 |

|

1 |

1 |

1 |

1 |

1 |

Таблица

2

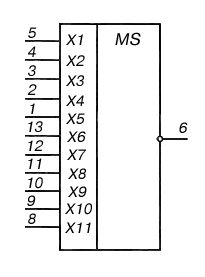

1 - вход X5;

2 - вход X4;

3

- вход X3;

4 - вход X2;

5

- вход X1;

6 - выход Y;

7

- общий;

8 - вход X11;

9

- вход X10;

10 - вход X9;

11

- вход X8;

12 - вход X7;

13

- вход X6;

14 - напряжение

питания;

- вход X5;

2 - вход X4;

3

- вход X3;

4 - вход X2;

5

- вход X1;

6 - выход Y;

7

- общий;

8 - вход X11;

9

- вход X10;

10 - вход X9;

11

- вход X8;

12 - вход X7;

13

- вход X6;

14 - напряжение

питания;

Реализация схемы с использование мультиплексора К555КП7:

Рис. 6 Схема СУ с использованием мультеплексора К555КП7

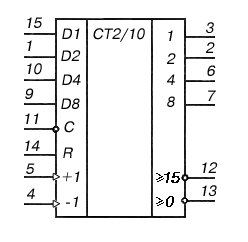

3. Проектирование делителя частоты на микросхемах к155ие7

Микросхемы представляет собой четырехразрядный двоичный реверсивный счетчик. Содержит 276 интегральных элементов. Корпус К155ИЕ7 типа 238.16-2

Условное

графическое обозначение

1

- вход информационный D2;

2 - выход

второго разряда Q2;

3 - выход первого

разряда Q1;

4 - вход "обратный счет";

5

- вход "прямой счет";

6 - выход

третьего разряда Q3;

7 - выход четвертого

разряда Q4;

8 - общий;

9 - вход

информационный D8;

10 - вход информационный

D4;

11 - вход предварительной записи;

12

- выход "прямой перенос";

13 - выход

"обратный перенос";

14 - вход

установки "0" R;

15 - вход информационный

D1;

16 - напряжение питания;

1

- вход информационный D2;

2 - выход

второго разряда Q2;

3 - выход первого

разряда Q1;

4 - вход "обратный счет";

5

- вход "прямой счет";

6 - выход

третьего разряда Q3;

7 - выход четвертого

разряда Q4;

8 - общий;

9 - вход

информационный D8;

10 - вход информационный

D4;

11 - вход предварительной записи;

12

- выход "прямой перенос";

13 - выход

"обратный перенос";

14 - вход

установки "0" R;

15 - вход информационный

D1;

16 - напряжение питания;