- •1) Що вивчає предмет «Архітектура комп’ютерів», що таке комп’ютер (к), опишіть основні напрями використовування к? Опишіть історію виникнення комп’ютерів, і основні покоління еом.

- •3) Багаторівнева комп’ютерна організація – структура призначення рівнів. Опишіть структуру рівнів як інтерфейс між різними елементами пк і кінцевим користувачем.

- •6) Намалюйте й опишіть блок-схему комп’ютера з єдиною шиною. Опишіть основні характеристики шини – структура паралельної шини. Намалюйте схему мультиплексора 2-х шин.

- •7) Структура процесора, основні функції, групи зовнішніх виводів. З яких основних елементів складається будь-який процесор? Намалюйте схему зв’язку процесора з оперативною пам’яттю комп’ютера.

- •8) Цикл Фон-Неймана, стадії виконання команди. На базі схеми зв’язку процесора із озу детально поясніть виконання команди пересилки даних із пам’яті в регістри процесора.

- •9) На базі внутрішньої структури процесора детально поясніть виконання команд умовних та безумовних переходів.

- •Суперскалярная архитектура

- •11) Приведіть схему й опишіть класифікацію напівпровідникових запам’ятовувальних пристроїв. Намалюйте загальний вид мікросхеми пам’яті 32Кх8 та приведіть її основні характеристики та діаграму роботи.

- •12) Види пам’яті комп’ютера (схема та пояснення). Намалюйте комірки зберігання інформації динамічної зберігання інформації динамічної та статичної пам’яті і поясніть їх роботу.

- •13) Ієрархічна структура пам’яті пк (намалюйте схему й поясніть її). Намалюйте схему регістра та опишіть його роботу за допомогою діаграми.

- •Операции в регистрах

- •14) Багаторівнева архітектура шин персонального комп’ютера: локальні шини, системна шина, шина внутрішньої периферії (блок-схема, властивості й призначення шин). Опишіть основні етапи еволюції шин пк.

- •19. Що таке переривання і які типи переривань існують? Які виводи має процесор для реєстрації переривань? Апаратні переривання, контролер переривання.

- •27. Формування 20 розрядної адреси в процесорі i8086, опис блоку й регістрів. Призначення сегментних регістрів cs, ds, ss, es, регістрів покажчиків sp, bp, si, di і регістру ip.

- •28. Архітектура процесорів ia32, режими роботи, дескриптори. Захищений режим роботи процесора, особливості адресації в цьому режимі.

- •29. Система bios, основні функції. Сервіси bios Pnp, dmi, aspi, bios Setup.

- •30. Система bios, структура, сервіси bios – призначення, способи виклику? Програма post, порядок тестування й ініціалізації пристроїв комп’ютера.

Суперскалярная архитектура

Способность выполнения нескольких машинных инструкций за один такт процессора путем увеличения числа исполнительных устройств. Появление этой технологии привело к существенному увеличению производительности, в то же время существует определенный предел роста числа исполнительных устройств, при превышении которого производительность практически перестает расти, а исполнительные устройства простаивают. Частичным решением этой проблемы являются, например, технология HyperThreading.

11) Приведіть схему й опишіть класифікацію напівпровідникових запам’ятовувальних пристроїв. Намалюйте загальний вид мікросхеми пам’яті 32Кх8 та приведіть її основні характеристики та діаграму роботи.

В цифровых системах используются внешние и внутренние запоминающие устройства (ЗУ). Внешние ЗУ реализуют на жестких магнитных (hard drive), интегрально-полупроводниковых (флэш-диски), оптических и магнитооптических дисках (CD, DVD). Внутренние ЗУ в основном – полупроводниковые – предназначены для хранения промежуточных данных и программ обработки данных. Внутренние ЗУ делятся на оперативные ЗУ и постоянные ЗУ.

Оперативные запоминающие устройства (ОЗУ) характеризуются возможностью быстрого ввода/вывода (записи/считывания) информации в виде двоичных чисел в свою любую отдельную ячейку. Поэтому синонимом ОЗУ является память с произвольной выборкой (RAM–Random Access Memory).

Постоянные запоминающие устройства (ПЗУ) в отличие от ОЗУ используются в основном для считывания записанной в них информации. Запись же осуществляется либо “раз и навсегда”, либо относительно редко. Этот класс ЗУ в зарубежной литературе называют ROM (Read–Only Memory – память только для считывания).

Существует также значительное количество ПЗУ с возможностью многократной записи в них информации – перепрограммируемые ПЗУ (ППЗУ).

Структура микросхем памяти

Полупроводниковые ОЗУ, ПЗУ состоят из двух основных частей: накопителя и схемы управления, или периферии. Накопитель – это основная часть ПЗУ, где хранятся данные (двоичные коды). Периферия предназначена для ввода и вывода этих данных. В нее входят дешифраторы, усилители, регистры, разного рода ключевые схемы, коммутаторы и другое.

Накопитель состоит из элементов памяти (ЭП), каждая из них хранит один бит информации. Основу ЭП составляют бистабильные ячейки, основным свойством которых является наличие двух устойчивых состояний – 0, 1.

На рис. 57 представлена типичная структура запоминающего устройства с матричной организацией.

Рис. 57. Структура микросхемы ОЗУ

На приведенной схеме используются следующие сокращения:

ДШх, ДШу – адресные дешифраторы строк и столбцов;

ФЗС – формирователь сигналов записи/считывания;

СУ – схема управления;

АШх, РШ – адресные и разрядные шины;

DI, DO – шины записи и считывания соответственно;

БК – буферный каскад.

Накопитель представляет собой прямоугольную матрицу ЭП, содержащую nx строк и ny столбцов. Емкость накопителя N = nx · ny. Каждый ЭП подключен к адресным (АШ) и разрядным (РШ) шинам. Выбор необходимого ЭП осуществляется путем подачи определенной комбинации адресных переменных (Am … A1 , A0). Адресные дешифраторы строк (ДШx) и столбцов (ДШy) формируют сигналы выборки на соответствующих АШ, которые определяют строку и столбец накопителя, в котором расположен выбираемый ЭП. Таким образом, m адресных входов позволяют выбирать один из N = 2m элементов памяти.

Режим

работы микросхемы определяется сигналами

выбора микросхемы ![]() (CHIP

SELECT) и записи-считывания

(CHIP

SELECT) и записи-считывания ![]() (WRITE/READ).

При подаче низкого потенциала на вход

выбора

(WRITE/READ).

При подаче низкого потенциала на вход

выбора ![]() схема

управления (СУ) разрешает формирование

сигналов выборки на АШx .

Если при этом сигнал на входе

схема

управления (СУ) разрешает формирование

сигналов выборки на АШx .

Если при этом сигнал на входе ![]() ,

то СУ формирует управляющий сигнал, при

котором ФЗС обеспечивает запись в

выбранном ЭП информации, поступающей

на вход DI. Выход DO в этом случае находится

в отключенном состоянии. Если сигнал

,

то СУ формирует управляющий сигнал, при

котором ФЗС обеспечивает запись в

выбранном ЭП информации, поступающей

на вход DI. Выход DO в этом случае находится

в отключенном состоянии. Если сигнал ![]() ,

то СУ переключает ФЗС в режим считывания,

при котором информация из выбранного

ЭП передается на выход DO, при этом

состояние входа DI не влияет на работу

микросхемы.

,

то СУ переключает ФЗС в режим считывания,

при котором информация из выбранного

ЭП передается на выход DO, при этом

состояние входа DI не влияет на работу

микросхемы.

При ![]() микросхема

находится в режиме хранения, т. е.

состояние ЭП не меняется при любых

сигналах на входах (Am …

A0),

DI,

.

Выход DO находится в отключенном состоянии.

микросхема

находится в режиме хранения, т. е.

состояние ЭП не меняется при любых

сигналах на входах (Am …

A0),

DI,

.

Выход DO находится в отключенном состоянии.

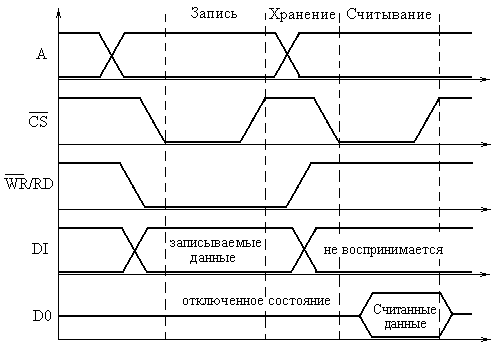

Типовые временные диаграммы, иллюстрирующие работу микросхем памяти, приведены на рис. 58.

Рис. 58. Временные диаграммы работы микросхем памяти с произвольной выборкой