- •1) Що вивчає предмет «Архітектура комп’ютерів», що таке комп’ютер (к), опишіть основні напрями використовування к? Опишіть історію виникнення комп’ютерів, і основні покоління еом.

- •3) Багаторівнева комп’ютерна організація – структура призначення рівнів. Опишіть структуру рівнів як інтерфейс між різними елементами пк і кінцевим користувачем.

- •6) Намалюйте й опишіть блок-схему комп’ютера з єдиною шиною. Опишіть основні характеристики шини – структура паралельної шини. Намалюйте схему мультиплексора 2-х шин.

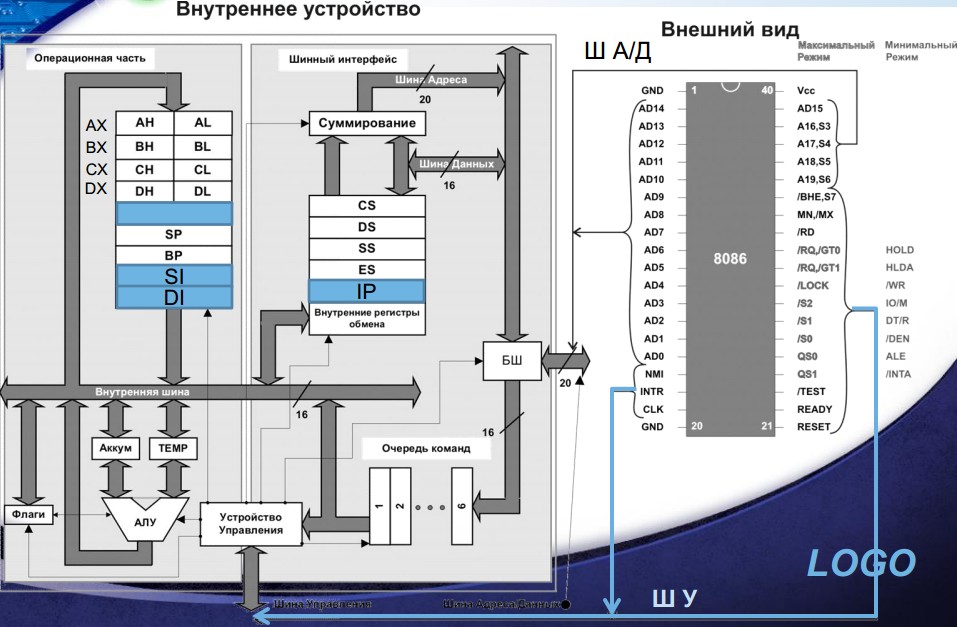

- •7) Структура процесора, основні функції, групи зовнішніх виводів. З яких основних елементів складається будь-який процесор? Намалюйте схему зв’язку процесора з оперативною пам’яттю комп’ютера.

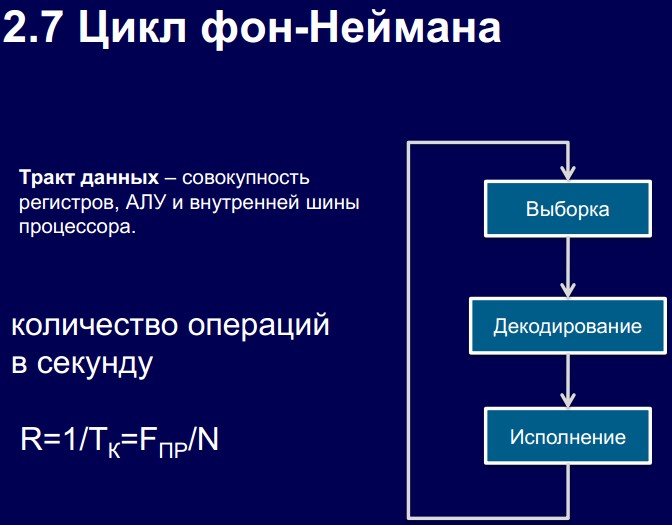

- •8) Цикл Фон-Неймана, стадії виконання команди. На базі схеми зв’язку процесора із озу детально поясніть виконання команди пересилки даних із пам’яті в регістри процесора.

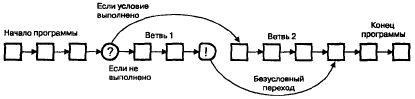

- •9) На базі внутрішньої структури процесора детально поясніть виконання команд умовних та безумовних переходів.

- •Суперскалярная архитектура

- •11) Приведіть схему й опишіть класифікацію напівпровідникових запам’ятовувальних пристроїв. Намалюйте загальний вид мікросхеми пам’яті 32Кх8 та приведіть її основні характеристики та діаграму роботи.

- •12) Види пам’яті комп’ютера (схема та пояснення). Намалюйте комірки зберігання інформації динамічної зберігання інформації динамічної та статичної пам’яті і поясніть їх роботу.

- •13) Ієрархічна структура пам’яті пк (намалюйте схему й поясніть її). Намалюйте схему регістра та опишіть його роботу за допомогою діаграми.

- •Операции в регистрах

- •14) Багаторівнева архітектура шин персонального комп’ютера: локальні шини, системна шина, шина внутрішньої периферії (блок-схема, властивості й призначення шин). Опишіть основні етапи еволюції шин пк.

- •19. Що таке переривання і які типи переривань існують? Які виводи має процесор для реєстрації переривань? Апаратні переривання, контролер переривання.

- •27. Формування 20 розрядної адреси в процесорі i8086, опис блоку й регістрів. Призначення сегментних регістрів cs, ds, ss, es, регістрів покажчиків sp, bp, si, di і регістру ip.

- •28. Архітектура процесорів ia32, режими роботи, дескриптори. Захищений режим роботи процесора, особливості адресації в цьому режимі.

- •29. Система bios, основні функції. Сервіси bios Pnp, dmi, aspi, bios Setup.

- •30. Система bios, структура, сервіси bios – призначення, способи виклику? Програма post, порядок тестування й ініціалізації пристроїв комп’ютера.

8) Цикл Фон-Неймана, стадії виконання команди. На базі схеми зв’язку процесора із озу детально поясніть виконання команди пересилки даних із пам’яті в регістри процесора.

Команды пересылки данных осуществляют обмен данными между регистрами или между регистрами и памятью. Основные команды этой группы имеют обозначение MOV или MVI. По команде MOV происходит пересылка содержимого одного регистра в другой, или содержимого регистра в память, или содержимого памяти в регистр. Например, по команде MOV В, Н происходит передача числа из регистра Н в регистр В. По команде MVI осуществляется непосредственная запись числа в - аккумулятор, регистр или память. Например, команда MVI В, 35 позволяет непосредственно записать число 35 ( в шестнадцатеричном коде) в регистр В.

Команды пересылки данных из одной области памяти в другую MVC, MVN, MVZ и MV1 похожих команд в других классах не имеют.

Команды пересылки данных, возможно, следовало бы называть командами копирования, потому что практически они осуществляют перемещение именно копии данных. Так, например, одна из этих команд перемещает данные из аккумулятора в область памяти. После выполнения данной команды и в области памяти, и в аккумуляторе находятся одни и те же данные. Очень редко в ходе выполнения команды пересылки данных разрушаются данные, находящиеся в исходном месте.

Команды пересылки данных предназначены для пересылки содержимого операнда-источника на место операнда-приемника. Существует четыре группы команд пересылки данных: общего назначения, ввода / вывода, логического адреса, признаков.

Команды пересылки данных не требуют выполнения никаких операций над операндами. Источником и приемником могут быть внутренние регистры процессора, ячейки памяти или устройства ввода / вывода. АЛУ в данном случае не используется.

Команды пересылки данных занимают очень важное место в системе команд любого процессора.

Какие функции выполняют команды пересылки данных. Содержимое каких областей участвует в их реализации.

Код операции в команде пересылки данных задает источник данных и способ адресации. Адресация может быть одного из трех видов: непосредственная, прямая и косвенная.

Третья группа команд - команды внутренней пересылки данных - дает возможность перемещать целиком слова или байты при требуемых в большинстве программ внутренних пересылках данных. Кроме того, команды этого типа позволяют выполнять сдвиговые операции над битами одного слова.

Как и любая другая команда, команда пересылки данных состоит из двух частей: кода операции и адресной части. Во всех командах пересылки данных должны быть указаны как источник, так и место назначения данных.

9) На базі внутрішньої структури процесора детально поясніть виконання команд умовних та безумовних переходів.

Команды условного и безусловного перехода

Оба этих вида команд предназначены для того, чтобы прерывать последовательное выполнение программы и вызывать так называемый переход. Причем условный переход происходит только при соблюдении какого-либо условия. Безусловный переход выполняется всегда, как только программа встретит соответствующую команду. В качестве условий перехода может выступать одно из следующих логических выражений:

- величина А равна величине В;

- величина А не равна величине В;

- величина А меньше величины В;

- величина А больше величины В;

- величина А меньше или равна величине В;

- величина А больше или равна величине В.

В качестве величин для сравнения может выступать содержимое любых внутренних регистров процессора, содержимое любых ячеек

памяти или просто константы.

Пример. Рассмотрим пример применения условного и безусловного переходов. Для наглядности изобразим цепочку команд в программной памяти в виде последовательности графических элементов (см. рис. 2.2). Ход выполнения программы показан при помощи стрелок. Квадратиками обозначены обычные команды (команды перемещения и команды преобразования данных). Кружочек с вопросом —это команда условного перехода. Скругленный элемент с восклицательным знаком — это безусловный переход. Такая программа имеет две ветви. В случае, если условие есть ложь, выполняется ветвь номер 1. В случае, если условие — истина, выполняется ветвь номер 2.

Допустим, что условный переход производит сравнение кода нажатой клавиши с некоторой константой. Тогда действие, выполняемое условным оператором, можно записать так: «Если код нажатой клавиши равен 0, перейти к выполнению ветви номер 2». Соответственно, в случае невыполнения условия (например, считанное число равно 1), программа продолжит

свою работу в обычном режиме и перейдет, таким образом, к выполнению ветви номер 1.

В конце ветви номер 1 стоит оператор безусловного перехода. Он служит для того, чтобы программа ни начала выполнять ветвь номер 2 сразу после выполнения ветви номер 1. В данном случае выполнение перехода обязательно и никакого условия не требуется.

Технически переход выполняется путем записи в регистр адреса нового значения. Изменение значения регистра адреса возможно только при помощи команд передачи управления.

10) Обчислення продуктивності процесора, та збільшення продуктивності процесора, конвеєри, суперскалярна архітектура (намалюйте й опишіть роботу конвеєра процесора)? У чому полягає основний принцип конвеєризації будь-якого процесу?

Конве́йер — это способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности (увеличения числа инструкций, выполняемых в единицу времени), технология, используемая при разработке компьютеров и других цифровых электронных устройств. Идея заключается в разделении обработки компьютерной инструкции на последовательность независимых стадий с сохранением результатов в конце каждой стадии. Это позволяет управляющим цепям процессора получать инструкции со скоростью самой медленной стадии обработки, однако при этом намного быстрее, чем при выполнении эксклюзивной полной обработки каждой инструкции от начала до конца.

Процессоры с конвейером внутри устроены так, что обработка инструкций разделена на последовательность стадий, предполагая одновременную обработку нескольких инструкций на разных стадиях. Результаты работы каждой из стадий передаются через ячейки памяти на следующую стадию, и так — до тех пор, пока инструкция не будет выполнена. Подобная организация процессора, при некотором увеличении среднего времени выполнения каждой инструкции, тем не менее обеспечивает значительный рост производительности за счёт высокой частоты завершения выполнения инструкций.

Не все инструкции являются независимыми. В простейшем конвейере, где обработка инструкции представлена пятью стадиями, для обеспечения полной загрузки, в то время пока заканчивается обработка первой инструкции, должно обрабатываться параллельно ещё четыре последовательных независимых инструкции. Если последовательность содержит инструкции, зависимые от выполняемых в данный момент, то управляющая логика простейшего конвейера приостанавливает несколько начальных стадий конвейера, помещая этим самым в конвейер пустую инструкцию («пузырёк»), иногда неоднократно, — до тех пор, пока зависимость не будет разрешена. Существует ряд приёмов, таких как форвардинг, значительно снижающих необходимость приостанавливать в таких случаях часть конвейера. Однако зависимость между инструкциями, одновременно обрабатываемыми процессором, не позволяет добиться увеличения производительности кратно количеству стадий конвейера в сравнении с бесконвейерным процессором.