- •2.1 Общие сведения об ограничителях

- •2.2 Краткие сведения о характеристиках полупроводниковых диодов

- •2.3 Односторонние ограничители без смещения

- •2.4 Односторонние ограничители со смещением

- •2.5 Двусторонние ограничители без смещения

- •2.6 Двусторонние ограничители со смещением

- •Диодные ключи

- •3.1 Насыщенный ключ в схеме включения с общим эмиттером

- •3.2 Статические режимы ключа

- •3.3 Способы ускорения переключения ключа

- •Основы булевой алгебры

- •Выходные каскады ттл микросхем

- •Сравнение основных характеристик ттл и кмоп микросхем

- •Триггер как элементарный последовательностный автомат.

- •4.1.2 Принципы работы и разновидности триггеров

- •6.1.2 Параллельные регистры

- •6.1.3 Регистры сдвига (последовательный)

- •6.1.4 Реверсивные регистры

- •6.1.5 Последовательно-параллельные регистры

- •6.1.6 Кольцевые счетчики на регистрах

- •6.1.7 Универсальные последовательно-параллельные регистры

- •2. Последовательный регистр.

- •3. Параллельно – последовательный регистр.

- •10.2 Общие сведения о мультиплексорах

Сравнение основных характеристик ттл и кмоп микросхем

Основной родовой признак ТТЛ — использование биполярных транзисторов, причем структуры только п-р-п. КМОП же, как следует из ее названия, основана на полевых транзисторах с изолированным затвором структуры МОП, причем комплементарных, то есть обоих полярностей — и с w- и с /^-каналом. Схемотехника базовых логических элементов ТТЛ и КМОП приведена на рис. 15.1. На западе их еще называют вентилями — чем можно оправдать такое название, мы увидим в конце главы.

Входной многоэмиттерный транзистор ТТЛ мы уже рисовали в главе И — он может иметь сколько угодно (на практике — до восьми) эмиттеров, и элемент тогда будет иметь соответствующее число входов. Если любой из эмиттеров транзистора VT1 замкнуть на «землю», то транзистор откроется, а фа-зорасщепляющий транзистор VT2 (с его работой мы знакомы по рис. 6.8) — закроется. Соответственно, выходной транзистор VT3 откроется, а VT4 — закроется, на выходе будет высокий логический уровень, или уровень логической единицы. Если же все эмиттеры присоединены к высокому потенциалу (или просто «висят» в воздухе), то ситуация будет обратная — VT2 откроется током через переход база-коллектор VT1 (такое включение транзистора называется «инверсным»), и на выходе установится ноль за счет открытого транзистора VT4. Такой ТТЛ-элемент будет осуществлять функцию «И-НЕ» (логический ноль на выходе только при единицах на всех входах).

ТТЛ

Выходной каскад ТТЛ-элемента представляет собой некое подобие комплементарного («пушпульного») каскада класса В, знакомого нам по аналоговым усилителям (см. рис. 8.2). Однако воспроизведение р-п-р-транзисторов оказалось для ТТЛ-технологии слишком сложным, потому такой каскад носит еще название псевдокомплементарного— верхний транзистор VT3 работает в режиме эмиттерного повторителя, а нижний — в схеме с общим эмиттером.

Рис. 15.1. Схемы базовых элементов ТТЛ и КМОП

Кстати, заметим, что из-за недоступности p-w-p-транзисторов воспроизведение схемы «ИЛИ» для ТТЛгтехнологии оказалось крепким орешком, и ее, схемотехника довольно существенно отличается от показанной на рис. 15.1 базовой схемы элемента «И-НЕ».

Заметки на полях

На заре транзисторной техники псевдокомплементарные каскады, подобные выходному каскаду ТТЛ, использовались — о ужас! — для усиления звука. Это построение дало основания для многочисленных попыток приспособить логические элементы, которые, в сущности, представляют собой усилитель с довольно большим (несколько десятков) коэффициентом усиления, для усиления аналоговых сигналов. Излишне говорить, что результаты оказались довольно плачевными, даже с КМОП-элементом, который построен куда более симметрично.

Как видно из схемы, ТТЛ-элемент существенно несимметричен и по входам, и по выходам. По входу напряжение логического нуля должно быть достаточно близко к «земле», при напряжении на эмиттере около 1,5 В (при стандартном для ТТЛ питании 5 В) входной транзистор уже запирается. Причем при подаче нуля нужно обеспечить отвод довольно значительного тока база-эмиттер— около 1,6 мА для стандартного элемента, отчего для элементов ТТЛ всегда оговаривается максимальное количество одновременно подсоединенных к выходу других таких элементов (стандартно — не более десятка). В то же время логическую единицу на входы можно не подавать вовсе. Практически, однако, подавать ее следует — по правилам незадействованные входы ТТЛ должны быть присоединены к питанию через резисторы 1 кОм.

Еще хуже дела обстоят на выходе: напряжение логического нуля обеспечивается открытым транзистором и действительно довольно близко к нулю — даже при нагрузке в виде десятка входов других таких же элементов оно не превышает 0,5 В, а в нормах на сигнал ТТЛ оговорена величина не более 0,8 В. А вот напряжение логической единицы довольно далеко отстоит от питания и составляет при питании 5 В в лучшем случае (без нагрузки) от 3,5 до 4 В, практически же в нормах оговаривается величина 2,4 В.

Такое балансирование десятыми вольта (напряжение нуля 0,8 В, напряжение порога переключения от 1,2 до 2 В, напряжение единицы 2,4 В) приводит к тому, что все ТТЛ-микросхемы могут работать в довольно узком диапазоне напряжений питания — практически от 4,5 до 5,5 В, многие даже от 4,75 до 5,25 В, то есть 5 В ±5%. Максимально допустимое напряжение питания составляет для разных ТТЛ-серий от 6 до 7 В, и при его превышении они обычно горят ясным пламенем. Низкий и несимметричный относительно питания порог срабатывания элемента приводит и к плохой помехоустойчивости.

Самым крупным (и даже более серьезным, чем остальные) недостатком ТТЛ является высокое потребление — до 2,5 мА на один такой элемент, это без учета вытекающих токов по входу и потребления нагрузки по выходу. Так что приходится только удивляться, почему микросхемы ТТЛ, содержащие много базовых элементов, вроде счетчиков или регистров, не требуют охлаждающего радиатора. Сочетание низкой помехоустойчивости с высоким потреблением — смесь довольно гремучая, и при разводке плат с ТТЛ-микросхемами приходится ставить по развязывающему конденсатору на каждый корпус. Все перечисленное в совокупности давно бы заставило отказаться от технологии ТТЛ вообще, однако у них до некоторого времени было одно неоспоримое преимущество: высокое быстродействие, которое для базового элемента в виде, показанном на рис. 15.1, может достигать десятков мегагерц.

В дальнейшем развитие ТТЛ шло по линии уменьшения потребления и улучшения электрических характеристик, в основном за счет использования т. н. переходов Шоттки, на которых падение напряжения может составлять 0,2—0,3 В вместо обычных 0,6—0,7 В (технология ТТЛШ, обозначается буквой S в наименовании серии, отечественный аналог— серии 531 и 530). Базовая технология, которая составляла основу широко распространенной в 1960—70-х годах серии 74 без дополнительных букв в обозначении (аналоги— знаменитые отечественные серии 155 и 133), сейчас практически не используется. ТТЛ-микросхемы в настоящее время можно выбирать из вариантов, представленных малопотребляющими сериями типа 74LSxx (серии 555 и 533) или быстродействующими типа 74Fxx (серия 1531). Причем потребление последних практически равно потреблению старых базовых серий при более высоком (до 125 МГц) быстродействии, а для первых все наоборот— быстродействие сохранено на уровне базового, зато потребление питания снижено раза в три-четыре.

КМОП

КМОП-элементы намного ближе к представлению о том, каким должен быть идеальный логический элемент. Для начала, как можно видеть из рис. 15.1, они практически симметричны, как по входу, так и по выходу. Открытый полевой транзистор на выходе (либо /?-типа для логической единицы, либо «-типа для логического нуля) фактически представляет собой, как мы знаем.

просто сопротивление, которое для обычных КМОП-элементов может составлять от 100 до 300 Ом (под «обычными» или «классическими» КМОП мы подразумеваем здесь серию 4000А или 4000В, см. далее). Для дополнительной симметрии на выходе обычно ставят последовательно два инвертора, подобных показанному на рис. 15.1 справа (жалко, что ли, транзисторов, если потребление не растет?). Поэтому на выходе не сказывается то, что в нижнем плече для схемы «И-НЕ» стоят два таких транзистора последовательно.

Для схемы «ИЛИ» такие транзисторы будут стоять в верхнем плече — она полностью симметрична схеме «И», что тоже плюс технологии КМОП по сравнению с ТТЛ. Обратите также внимание, что выходной каскад инвертора построен не по схеме «пушпульного» каскада, то есть это не потоковые повторители напряжения, а транзисторы в схеме с общим истоком, соединенные стоками, что позволяет получить дополнительный коэффициент усиления по напряжению.

На практике особенности построения элемента приводят к тому, что в КМОП-микросхемах:

? на ненагруженном выходе напряжение логической единицы практически равно напряжению питания, а напряжение логического нуля практически равно потенциалу «земли»;

? порог переключения близок к половине напряжения питания;

? входы практически не потребляют тока, так как представляют собой изолированные затворы МОП-транзисторов;

? в статическом режиме весь элемент также не потребляет тока от источника питания.

Из последнего положения вытекает, что схема любой степени сложности, построенная с помощью КМОП-элементов, в «застывшем» состоянии и даже при малых рабочих частотах, не превышающих десятка-другого килогерц, практически не потребляет энергии! Отсюда ясно, как стали возможными такие фокусы, как наручные часы, которые способны идти от малюсенькой батарейки годами, или sleep-режим микроконтроллеров, в котором они потребляют от 1 до 50 мкА на все десятки тысяч составляющих их логических элементов.

Другое следствие вышеперечисленных особенностей — исключительная помехоустойчивость, достигающая половины напряжения питания. Но это еще не все преимущества. КМОП-микросхемы «классических» серий могут работать в диапазоне напряжений питания от 2 до 18 В, а современные быстродействующие — от 2 до 7 В. Единственное, что при этом происходит— при

снижении питания довольно резко— в разы— падает быстродействие и ухудшаются некоторые другие характеристики.

Кроме того, выходные транзисторы КМОП, как и любые другие полевые транзисторы, при перегрузке (например, в режиме короткого замыкания) работают как источники тока — при напряжении питания 15 В этот ток составит около 30 мА, при 5 В — около 5 мА. Причем это в принципе может быть долгосрочный режим работы таких элементов, единственное, что при этом надо проверить — не превышается ли значение суммарного допустимого тока через вывод питания, которое обычно составляет около 50 мА. То есть, возможно, придется ограничить число выходов, одновременно подключенных к низкоомной нагрузке. Естественно, о логических уровнях в таком режиме уже речи не идет, только о втекающем или вытекающем токе.

И тут мы подходим к основному недостатку «классической» КМОП-технологии — низкому в сравнении ТТЛ быстродействию. Это обусловлено тем, что изолированный затвор МОП-транзистора представляет собой конденсатор довольно большой емкости— в базовом элементе до 10—15 пФ. В совокупности с выходным резистивным сопротивлением предыдущей схемы такой конденсатор образует фильтр низких частот. Обычно рассматривают не просто частотные свойства, а время задержки распространения сигнала на один логический элемент. Задержка возникает из-за того, что фронт сигнала не строго вертикальный, а наклонный, и напряжение на выходе еще только начнет нарастать (или снижаться), когда напряжение на входе достигнет уже значительной величины (в идеале— половины напряжения питания). Время задержки могло достигать у ранних серий КМОП величины 200—250 НС (сравните — у базовой серии ТТЛ всего 7,5 не). На практике при напряжении питания 5 В максимальная рабочая частота «классического» КМОП не превышает 1—3 МГц— попробуйте соорудить на логических элементах генератор прямоугольных сигналов по любой из схем, которые будут разобраны в главе 16, и вы увидите, что уже при частоте 1 МГц форма сигнала будет скорее напоминать синусоиду, чем прямоугольник.

Другим следствием наличия высокой входной емкости является то, что при переключении возникает импульс тока перезарядки этой емкости, то есть чем выше рабочая частота, тем больше потребляет микросхема, и считается, что при максимальных рабочих частотах ее потребление может сравниться с потреблением ТТЛ (по крайней мере, ТТЛ серии 74LS). Дело еще усугубляется тем, что из-за затянутых фронтов импульсов элемент достаточно длительное время находится в активном состоянии, когда оба выходных транзистора приоткрыты (то есть возникает так называемый эффект «сквозного тока»).

Это же затягивание фронтов в сочетании с высокоомным входом приводит к снижению помехоустойчивости при перею1ючении — если на фронте сигнала «сидит» высокочастотная помеха, то это может приводить к многократным переключениям выхода, как это было у компаратора (см. главу 13). По этой причине в спецификациях на микросхемы часто указывают желательную максимальную длительность фронтов управляющего сигнала.

Однако в современных КМОП, в отличие от «классических», большинство недостатков, связанных с низким быстродействием, удалось преодолеть (правда, за счет снижения допустимого диапазона питания). Подробнее о сериях КМОП рассказано далее, а пока несколько еще несколько слов об особенностях этих микросхем.

Незадействованные входы элемента КМОП нужно обязательно подключать куда-нибудь — либо к земле, либо к питанию (резисторов при этом не требуется, так как вход тока не потребляет), либо объединять с соседним входом — иначе наводки на столь высокоомном входе полностью нарушат работу схемы. Причем в целях снижения потребления следует делать это и по отношению к незадействованным элементам в том же корпусе (но не ко всем незадействованным выводам, конечно). «Голый» вход КМОП из-за своей вы-сокоомности может быть также причиной повышенной «смертности» чипов при воздействии статического электричества, однако на практике входы всегда шунтируют диодами, как показано на рис. 11.4. Допустимый ток через эти диоды также оговаривается в спецификациях.

Схема и характеристики инвертора КМОП

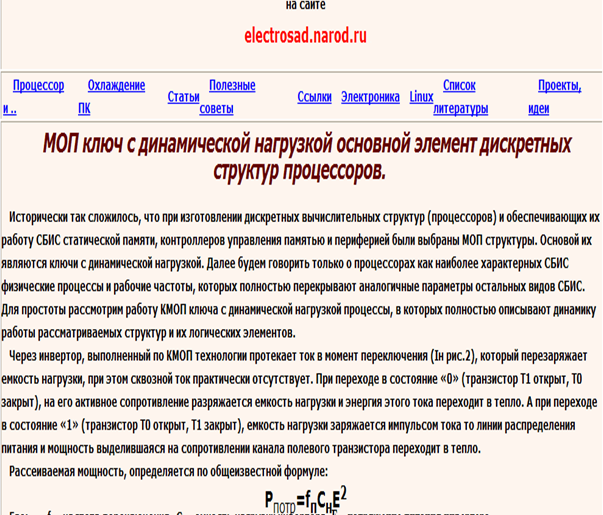

Кроме элементов ТТЛ выпускают элементы КМОП (КМДП). КМОП – комплементарные металл-оксидные полупроводники (полевой транзистор с изолированным затвором). Важнейшим свойством полевых транзисторов является их большое входное сопротивление по постоянному току (Rвх=1012 – 1014 Ом). Благодаря этому полевые транзисторы в статических режимах практически не потребляют тока во входных цепях; тем самым обеспечивается возможность построения ключевых элементов с большой нагрузочной способностью. Главным недостатком полевых транзисторов по сравнению с биполярными является относительно невысокое быстродействие. Приведем для рассмотрения схему построения инвертора на полевых транзисторах (рис.7.1).

Рисунок 7.1 – Принципиальная схема инвертора КМОП

Схемы такого типа могут быть повреждены при воздействии статических зарядов и потенциале более 100 В. Статистический анализ показал, что около 65% всех отказов МДП-приборов обусловлен воздействием статистических зарядов. Непосредственно в КМДП-элементах для такой защиты вводят дополнительные элементы (рис.7.1): диод VD1 между входом и одной из шин питания; два диода между входом и каждой из шин; поликремниевый резистор с двумя диодами VD2 и VD3. Использование диодов снижает вероятность пробоя, но не дает абсолютной защиты схемы. Диоды срабатывают с некоторой задержкой и за это время возможен пробой МДП-вентиля. Диоды VD4 и VD5 предназначены для защиты последующих каскадов. Диод VD6 защищает от отрицательного напряжения питания.

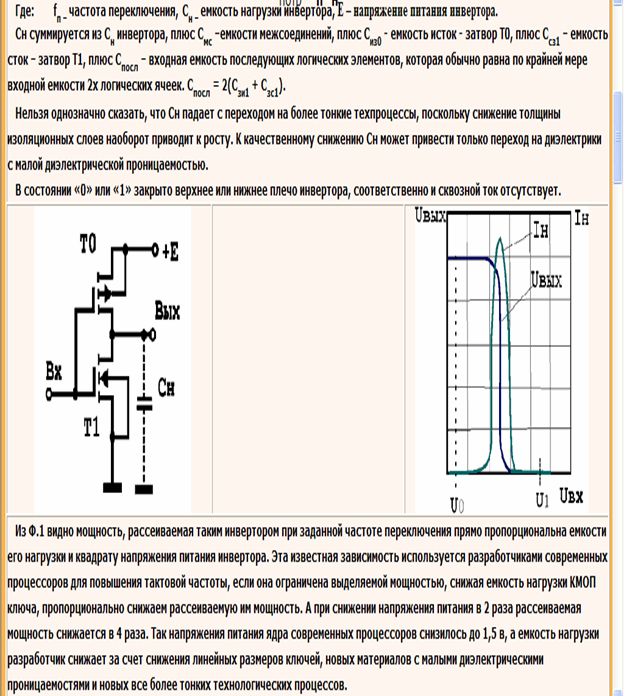

Сравнительные характеристики логических элементов изготовленных по разным технологиям

Для удобства сведем характеристики ЛЭ в таблицу 7.1. (Все параметры приведены в статическом режиме, логический элемент находится в одном из двух устойчивых состояний “0” или “1”)

Таблица 7.1 – Характеристики логических элементов

Параметр |

Старые разработки |

Новые разработки |

|||

ТТЛ серия К155 |

КМОП серия КП6 |

ЭСЛ серия 500 |

ТТЛ серия КР1533 |

КМОП серия КР155 |

|

I0вх |

-1.6 мА |

-0,1 мкА |

0,5 мкА |

-0,1мА |

-0,1 мкА |

I1вх |

0,04 мА |

0,1 мкА |

0,25...0,5мА |

20 мкА |

0,1 мкА |

U0вых не больше, В |

0,4 |

0,3 |

-1,63 |

0,4 |

0,1 |

U1вых не менее, В |

2,4 |

8,2 |

-0,9 |

2,4 |

Uпит-0,1 |

Uпит , В |

+5 |

+9 |

-5,2 |

5 |

2...6 |

t10зд.р., нс |

22 |

200...500 |

2,9...3,4 |

|

9,5 при Uпит=4,5В |

t01зд.р., нс |

15 |

200...500 |

2,9...3,4 |

9 |

8,5 при Uпит=4,5В |

I0потр |

16,5 мА |

0,3 мкА |

21 мА |

4 мА |

40 мкА |

I1потр |

6 мА |

0,3 мкА |

21 мА |

1,8 мА |

40 мкА |

В таблице приняты следующие обозначения:

I0вх – входной ток интегральной микросхемы при уровне логического нуля на входе.

I1вх – входной ток интегральной микросхемы при уровне логической единицы на входе.

U0вых – напряжение получаемое на выходе при уровне логического нуля на входе.

U1вых – напряжение получаемое на выходе при уровне логической единицы на входе.

Uпит – напряжение питания.

t10зд.р. – время задержки переключения из “1” в “0” (время между переключениями на входе и на выходе).

I0потр – ток потребления при нуле на выходе логического элемента. ЭСЛ самые быстродействующие и имеют малое время задержки. Чем меньше Iпотр , тем лучше.

Чем меньше ток на входе, тем лучше. ЭСЛ – эмиттерно-связанная логика работает в линейном режиме. КМОП и ТТЛ работают в ключевом режиме.

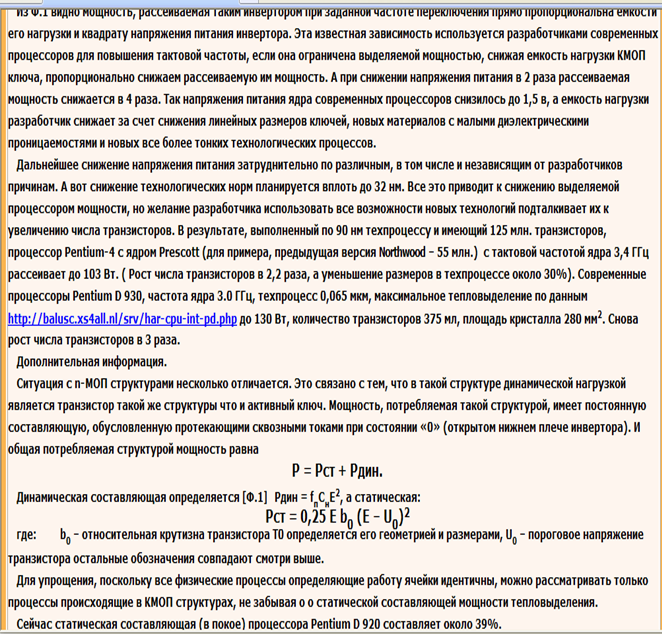

Статический режим – это режим у которого отсутствуют переключения или их очень мало. Чем больше время переключения элемента, тем больше треугольник на рис.7.2 (то есть больше сквозные токи возникающие при переключении КМОП), так как ток будет протекать дольше при открытии и закрытии. Чем чаще происходят переключения, тем больше потребление тока. В динамическом режиме потребление тока возрастает.

Рисунок 7.2 – Иллюстрация сквозных токов возникающих при переключении КМОП

Нагрузочная способность логического элемента – количество входов ЛЭ одноименной серии, которые могут быть подключены к выходу логического элемента и при этом сохраняются в параметры технического условия. Типовые значения нагрузочной способности для ТТЛ – 10 входов.

Зависимость мощности, рассеиваемой на логическом элементе, от частоты переключения. Объяснить, почему наблюдается такая зависимость

ПРО ЄСЛ

для систем с большим быстродействием наиболее перспективен ряд ЭСЛ (логические схемы с эмиттерной связью).

В схемах ЭСЛ транзисторы работают вне области насыщения, поэтому автоматически исключается задержка, вызванная избыточными зарядами. Основным свойством и достоинством схем ЭСЛ является небольшая задержка, величина которой у самых последних типов составляет около 0.01 нс. Принцип действия схем ЭСЛ – логических схем с эмиттерной связью – заключается в переключении точно определённого тока малыми изменениями управляющего напряжения, порядка десятых вольт

6.Триггеры. Определение. Триггеры R-S типа. Определение, описание работы, примеры реализации и применения. Синхронные и асинхронные R-S триггеры. Т-триггеры. Определение, описание работы, примеры реализации и применения. D-триггеры. Определение, описание работы, примеры применения. Триггеры J-K типа. Определение, описание работы, примеры реализации и применения. Применение как T, D и R-S триггера.

Общая характеристика и классификация триггеров

Подавляющее большинство цифровых устройств совмещают функции по переработке и

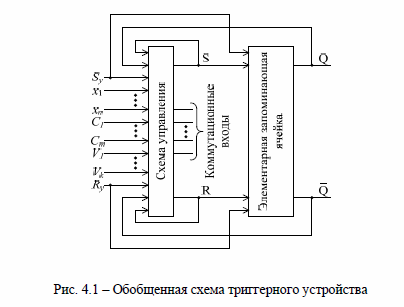

хранению информации. В арифметических и логических устройствах для хранения информации чаще всего используют триггеры – устройства с двумя (или более) устойчивыми состояниями выхода, содержащие элементарную запоминающую ячейку (триггер) и схему управления, преобразующую поступающую информацию в комбинацию сигналов, действующих непосредственно на входы элементарной запоминающей ячейки. Триггеры способны под действием внешних (управляющих, переключающих) сигналов переключаться в любое из этих состояний и находиться в них сколь угодно долго после прекращения их действия. Обобщенную схему триггерного устройства (в дальнейшем просто триггера) можно представить в виде, показанном на рис. 4.1, где 1,..., n x x – информационные входы; 1 m C ,...,C –входы синхронизации, или тактовые входы; 1 k V ,...,V – управляющие входы; y y R ,S – установочные входы; S, R – информационные входы элементарной запоминающей ячейки; Q,Q –выходы. Коммутационные входы используются для внешних соединений в программируемых универсальных триггерах. В реальных схемах триггеров некоторые входные сигналы и связи, пока-

занные на рис. 4.1, могут отсутствовать, а в простейших триггерах может не быть схемы управления. Для информационных входов приняты следующие обозначения: S (Set – установка) –вход для раздельной установки триггера в состояние "1" (Q=1,Q=0 ); R (Reset – сброс) – вход для раздельной установки триггера в состояние "0" (Q=0 , Q=1) ; T (Toggle – релаксатор) – счетный вход триггера; J (Jerk – внезапное включение) – вход для раздельной установки триггера в состояние "1" в универсальном JK-триггере; К ( K i l l – внезапное отключение) – вход для раздельной установки триггера в состояние "0" в универсальном JK-триггере; D (Data –данные, Delay – задержка, Drive – передача) – информационный вход для установки триггера в состояние "0" пли "1"; V (Valve – клапан, вентиль) – управляющий вход для разрешения приема либо информационных, либо тактовых сигналов; тактовый вход С (Clock – первичный источник сигна-

лов синхронизации) разрешает схеме управления запись информации в триггер.

Если у триггера только два устойчивых состояния, то они называются бистабильными.

При этом каждое состояние легко различимо по уровням напряжений на его выходах. Бистабильные триггеры, как правило, имеют два выхода (плеча), хотя о состоянии триггера можно судить по одному из них, который является прямым выходом и обозначается Q; второй выход называется инверсным и обозначается Q. О состоянии триггера достаточно судить по уровню сигнала на одном из его выходов. Последнее обстоятельство привело к разработке ряда триггеров с одним выходом, которые в отличие от парафазных, т. е. триггеров с двумя выходами, называются однофазными. Приняв одно из состояний триггера за 1 (т. е. Q = 1), второе за 0 (т. е.

Q = 0), можно считать, что триггер хранит (помнит) один бит информации, записанной в двоичном коде. При этом в зависимости от того, какая форма сигнала принимается за 1 и 0, т. е. в зависимости от способа кодирования (представления) состояний, все триггеры подразделяются на триггеры с потенциальным и импульсным кодированием. Отличительной особенностью первых является то, что каждому состоянию триггера ставится в соответствие наличие сигнала постоянной амплитуды высокого (близкого к напряжению питания) и низкого (близкого к нулю) логических уровней. При этом если сигнал на выходе триггера Q соответствует высокому уровню напряжения, говорят, что триггер находится в состоянии 1 (Q = 1), а если низкого, то в состоянии 0 (Q = 0).

Классификация триггеров может проводиться по различным определяющим признакам.

По способу организации логических связей различают:

-триггеры с раздельной установкой состояний "0" и "1" (RS-триггеры);

- со счетным входом (T-триггеры); универсальные с раздельной установкой состояний

"0" и "1" (JK-триггеры);

- с приемом информации по одному входу (D-триггеры);

- универсальные с управляемым приемом информации по одному входу (D-триггеры);

-комбинированные (например, RST-, RSJK-, RSD-триггеры и т.п.);

-со сложной входной логикой.

По способу записи информации триггеры подразделяются на несинхронизируемые (асин-

хронные, нетактируемые); синхронизируемые (синхронные, тактируемые).

По способу синхронизации различают триггеры синхронные со статическим управлением

записью и синхронные с динамическим управлением записью.

В синхронных триггерах со статическим управлением записью тактовый импульс начинает оказывать влияние только тогда, когда его уровень возрастает или до уровня "1", или уменьшается до уровня "0" в зависимости от элементной базы, на которой выполняется триггер. Триггеры, состояние которых изменяется в интервале действия уровней "1" или "0" тактового импульса, называются триггерами, срабатывающими по уровню, а триггеры, состояние которых изменяется по окончании действия уровней "1" или "0" тактового импульса, называются триггерами с внутренней задержкой. Информационные сигналы оказывают влияние на триггер лишь в течение действия тактового импульса. В синхронных триггерах с динамическим управлением записью информация регистрируется триггером в момент изменения амплитуды тактового импульса в определенном направлении, т. е. во время нарастания или спада его фронта.

По количеству информационных входов триггеры могут быть одновходовые, двухвходовые и многовходовые. Наибольшее распространение получили одно- и двухвходовые триггеры. Не следует путать количество информационных входов с количеством фактических входов, на которые поступают информационные сигналы, так как реально действующий информационный вход в структуре триггера может быть конъюнкцией дизъюнкцией или какой-либо функцией нескольких логических переменных, действующих на информационных входах, например, J=J1 J2 J3 ;

K=K1 K2 K3 ; J=J1 J2 J3 и т. п.

По количеству тактовых входов различают триггеры однотактные, двухтактные и много-

тактные. Иногда к двухтактным относят двухступенчатые триггеры (MS-схемы), однако надо помнить, что основное назначение последних – получение эффекта временной задержки информационных сигналов в структуре триггера, если такой эффект нельзя реализовать с использованием каких-либо физических методов, например с помощью накопления зарядов и т. п.

По виду выходных сигналов триггеры разделяются на статические и динамические. Статические триггеры – триггеры, у которых выходные сигналы в устойчивых состояниях остаются

неизменными во времени.

Динамические триггеры – триггеры, у которых выходные сигналы вустойчивых состояниях изменяются во времени.

По способу запоминания информации могут быть триггеры с логической и физической организацией памяти. Первые выполняются на логических элементах И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ и т. д., а вторые являются элементами запоминающих устройств, в которых используются нелинейные свойства материалов (ферриты) или нелинейные вольтамперные характеристики компонентов (динисторы).

По способу хранения информации различают триггеры с активным хранением информации (выходной информационный сигнал действует постоянно); с пассивным хранением информации (выходной информационный сигнал может быть получен только с помощью специального опросного сигнала).

Поскольку триггеры в цифровых устройствах взаимодействуют с другими элементами

схемы, кроме их функционального назначения необходимо знать их схемотехнические параметры. Прежде всего, к этим параметрам необходимо отнести параметры логических элементов, на которых выполнен триггер: об K – коэффициент объединения по входу; раз K – коэффициент разветвления по выходу, уровни "0" и "1", входные и выходные токи и т. д.

Специфическими параметрами триггера, в отличие от логических элементов, являются:

1. Разрешающая способность триггера раз t – наименьший интервал времени между входными сигналами минимальной длительности, вызывающими бесперебойное переключение триггера. Очевидно, что раз t зависит от того, какой смысл вкладывается в слова "бесперебойное переключение триггера". Принято считать, что триггер переключается бесперебойно, если любое значение выходного сигнала, определяемое правилами работы, имеет длительность, не меньшую среднего времени задержки распространения зд.р.ср t одного логического элемента схемы;

2. Максимальная частота переключения триггера

Поскольку, как отмечено выше, выходные сигналы триггера при воздействии входных

сигналов с частотой макс. f имеют длительность зд.р.ср t , то, учитывая длительность фронтов

нарастания и спада, можно сделать вывод, что эти выходные сигналы являются недостаточным для надежной передачи информации в логические цепи, так как уровни "1" и "0" в этом случае не будут фиксироваться. Для обеспечения их фиксирования принято уменьшать частоту макс. f в 1,5 раза и считать ее рабочей, т. е.

где l – количество элементов в цепочке от входа информационного или тактового сигнала до выхода элемента, на котором подтверждается состояние триггера.

Из определения и t и зд.пер t следует, что l =k+ 1. Единица в этом выражении характери-

зует задержку распространения одного из логических элементов, на которых выполняется элементарная запоминающая ячейка триггера.

Совокупность параметров раб t , и t и зд.пер t определяет быстродействие триггеров и, в ко-

нечном счете, быстродействие цифровых устройств, построенных на их основе.

15

15