- •5.3. Микроконтроллер avr at90s8515 семейства Classic

- •Организация памяти микроконтроллера

- •Память программ

- •Память данных

- •Использование внешнего озу

- •Регистры общего назначения

- •Регистры ввода/вывода

- •Энергонезависимая память данных

- •Сторожевой таймер

- •Последовательный периферийный интерфейс spi

- •Прерывания

- •Обработка прерываний

- •Программирование микроконтроллеров

- •Защита программного кода и данных

- •Система команд и способы адресации памяти данных

- •Прямая адресация

- •Прямая адресация одного регистра общего назначения

- •Прямая адресация двух регистров общего назначения

- •Прямая адресация регистра ввода/вывода

- •Прямая адресация озу

- •Косвенная адресация

- •Простая косвенная адресация

- •Относительная косвенная адресация

- •Косвенная адресация с преддекрементом

- •Косвенная адресация с постинкрементом

- •Система команд

- •Операнды

- •Типы команд

- •Команды арифметических и логических операций

- •Команды пересылки данных

- •Команды передачи управления

- •Команды операций с битами

- •Команды управления системой

- •Пример программы и её оформление

- •Микропроцессорная система управления на базе мк at90s8515

- •7. Микроконтроллер экр1847вг6

- •8. Частотно-регулируемые привода

- •Режимы управления асинхронными электродвигателями

- •Преобразователь частоты 1336Plus

5.3. Микроконтроллер avr at90s8515 семейства Classic

Микроконтроллер AVR AT90S8515 семейства Classic является 8-разрядным микроконтроллером с RISC - архитектурой (рис. 5.6, табл. 5.17). МК имеет электрически стираемую память программ (FLASH), ОЗУ и память данных (EEPROM), а также разнообразные периферийные устройства: сторожевой таймер, два таймер/счетчика, последовательные асинхронный и синхронный порты, четыре 8-разрядных порта ввода/вывода, аналоговый компаратор.

Организация памяти микроконтроллера

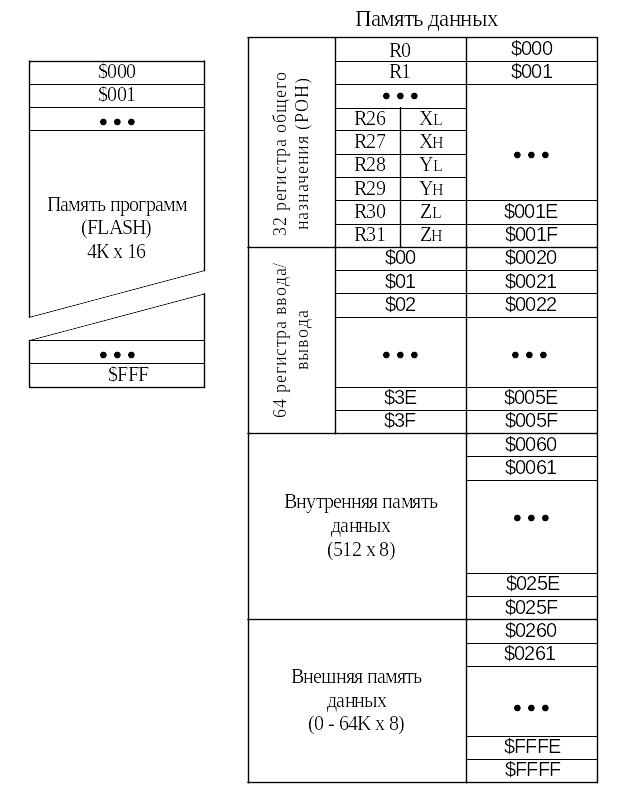

Память микроконтроллеров AVR семейства Classic выполнена по Гарвардской архитектуре (рис. 5.7), в которой разделены не только адресные пространства памяти программ и памяти данных, но также и шины доступа к ним. Причем память данных состоит из трех областей: регистровая память, статическое ОЗУ и память на основе EEPROM. В связи с тем, что регистровая память находится в адресном пространстве ОЗУ, об этих двух областях памяти обычно говорят как об одной. Каждая из областей (ОЗУ и EEPROM) расположена в своем адресном пространстве.

Память программ

Память программ ёмкостью 4 К 16-разрядных слов предназначена для хранения команд, управляющих функционированием микроконтроллера. В памяти программ хранятся также различные константы, не меняющиеся во время работы программы. Память программ в микроконтроллерах семейства Classic представляет собой электрически стираемое ППЗУ (FLASH-ПЗУ). Поскольку все команды занимают в памяти 16 бит (некоторые - 32 бита), память программ имеет 16-разрядную организацию. Для адресации памяти программ используется счетчик команд (РС - Program Counter).

Память данных

Память данных микроконтроллеров семейства Classic разделена на три части: регистровая память, оперативная память (статическое ОЗУ) 512 байт и энергонезависимое ЭСППЗУ (EEPROM) 512 байт.

Регистровая память включает в себя 32 регистра общего назначения (РОН), объединенных в регистровый файл и служебные регистры ввода/вывода (РВВ). Размер регистровой памяти фиксирован и для всех моделей составляет 96 байт, соответственно под РОН отводится 32 байта, а под РВВ - 64 байта.

Использование внешнего озу

Микроконтроллер АТ90S8515 имеет возможность подключения внешнего статического ОЗУ объемом до 64 Кбайт. Для разрешения работы с внешним ОЗУ необходимо установить в «1» разряд SRE регистра MCUCR. При этом микроконтроллер начинает сам управлять режимом работы порта A (вход/выход).

Для подключения

внешнего ОЗУ используются следующие

выводы микроконтроллера: порт A

(PA0...PA7)

- мультиплексированная шина адреса

(младшие 8 разрядов)/шина данных; порт

С (PC0

... PC7)

- шина адреса (старшие 8 разрядов); ALE-

сигнал строба адреса;

![]() (PС7)

- сигнал строба чтения;

(PС7)

- сигнал строба чтения;

![]() (PС6)

- сигнал строба записи.

(PС6)

- сигнал строба записи.

Рис. 5.6. Структурная схема микроконтроллера АТ90S8515

Таблица 5.17. Описание выводов МК AT90S8515. В таблице использованы следующие обозначения: I - вход; O - выход; I/O -вход/выход.

Обозначение |

Номер (тип вывода) |

Описание выводов |

XTAL1 |

19 (I) |

Вход генератора или внешнего тактового сигнала |

XTAL2 |

18 (O) |

Выход генератора |

|

9 (I) |

Вход сброса. |

PA0 (AD0) |

39 (I/O) |

АD0 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA1 (AD1) |

38 (I/O) |

АD1 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA2 (AD2) |

37 (I/O) |

АD2 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA3 (AD3) |

36 (I/O) |

АD3 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA4 (AD4) |

35 (I/O) |

АD4 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA5 (AD5) |

34 (I/O) |

АD5 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA6 (AD6) |

33 (I/O) |

АD6 (мультиплексная ША/ШД для внешнего ОЗУ) |

PA7 (AD7) |

32 (I/O) |

АD7 (мультиплексная ША/ШД для внешнего ОЗУ) |

PB0 (T0) |

1 (I/O) |

Вход внешнего тактового таймера /счетчика Т0 |

PB1 (T1) |

2 (I/O) |

Вход внешнего тактового таймера /счетчика Т1 |

PB2 (AIN0) |

3 (I/O) |

Положительный вход компаратора |

PB3 (AIN1) |

4 (I/O) |

Отрицательный вывод компаратора |

PB4 ( |

5 (I/O) |

Выбор Slave-устройства на шине SPI |

PB5 (MOSI) |

6 (I/O) |

Выход (Master) или вход (Slave) данных модуля SPI |

PB6 (MISO) |

7 (I/O) |

Вход (Master) или выход (Slave) данных модуля SPI |

PB7 (SCK) |

8 (I/O) |

Выход (Master) или вход (Slave) тактового сигнала SPI |

PC0 (A8) |

21 (I/O) |

A8 (Старший байт ША для внешнего ОЗУ) |

PC1 (A9) |

22 (I/O) |

A9 (Старший байт ША для внешнего ОЗУ) |

PC2 (A10) |

23 (I/O) |

A10 (Старший байт ША для внешнего ОЗУ) |

PC3 (A11) |

24 (I/O) |

A11 (Старший байт ША для внешнего ОЗУ) |

PC4 (A12) |

25 (I/O) |

A12 (Старший байт ША для внешнего ОЗУ) |

PC5 (A13) |

26 (I/O) |

A13 (Старший байт ША для внешнего ОЗУ) |

PC6 (A14) |

27 (I/O) |

A14 (Старший байт ША для внешнего ОЗУ) |

PC7 (A15) |

28 (I/O) |

A15 (Старший байт ША для внешнего ОЗУ) |

PD0 (RXD) |

10 (I/O) |

Вход UART |

PD1 (TXD) |

11 (I/O) |

Выход UART |

PD2 (INT0) |

12 (I/O) |

D2 (Вход 0 внешнего прерывания) |

PD3 (INT1) |

13 (I/O) |

D3 ( Вход 1 внешнего прерывания) |

PD4 |

14 (I/O) |

Разряд 4 порта D |

PD5 (OC1A) |

15 (I/O) |

Выход А таймера/счетчика Т1(режим сравнения, ШИМ) |

PD6 ( ) |

16 (I/O) |

Строб записи во внешнее ОЗУ |

PD7 ( ) |

17 (I/O) |

Строб чтения во внешнее ОЗУ |

OC1B |

29 (O) |

Выход В таймера/счетчика Т1 (режим сравнения, ШИМ) |

ICP |

31 (I) |

Вход захвата таймера/счетчика Т1 (режим захвата) |

ALE |

30 (O) |

Строб адреса внешнего ОЗУ |

GND |

20 |

Общий вывод |

VCC |

40 |

Вывод источника питания |

Рис. 5.7. Структура памяти программ и данных МК AT90S8515

Как показано на рис. 5.8, для подключения внешнего ОЗУ к микроконтроллеру дополнительно потребуется регистр-защелка. В качестве защелки можно использовать микросхемы 1533ИР22, 1564ИР22, 1594ИР22 с потенциальным управлением или 1533ИР23 с динамическим управлением или другие аналогичные.

Рис. 5.8. Схема подключения внешней памяти данных