- •Частина 1. Основи цифрової схемотехники

- •§ 1.1. Загальні поняття та визначення

- •§ 1.2. Математичні основи побудови цифрових логічних схем

- •§ 1.3. Логічні функції однієї та двох змінних

- •§ 1.4. Аксіоми та закони алгебри логіки

- •§ 1.5. Суперпозиція логічних функцій

- •§ 1.6. Нормальні і досконалі нормальні форми логічних функцій

- •Практикум 1

- •§ 1.7. Застосування матриць Карно для зображення

- •§ 1.8. Побудова схем на логічних елементах з обмеженою

- •Практикум 2.

- •Глава 2. Проектування цифрових схем комбінаційного типу

- •§ 2.1. Проблеми проектування цу комбінаційного типу

- •Що реалізуються, дднф та дкнф

- •Що реалізуються, дднф та дкнф

- •Практикум 3

- •§ 2.2. Суматори

- •§ 2.3. Побудови комбінаційних схем на базі комутаторів

- •§ 2.4. Селектор-демультиплексор

- •§ 2.5. Виникнення змагань і спосіб їх усунення

- •Практикум 4

- •Глава 3. Послідовна логіка

- •§ 3.1. Часові булеві функції

- •§ 3.2. Булеві функції і роду

- •§ 3.3. Булеві функції іі роду

- •Практикум 5

- •Частина 2. Розробка та проектування цифрових пристроїв

- •Глава 1. Класифікація, технології та сполучення інтегральних схем

- •§ 1.1. Технології та форми представлення інформації

- •§ 1.2. Схемотехніка базових елементів ттл-логіки

- •Та його схемо технічне зображення

- •Та таблиця істинності його роботи

- •Інтегральна мікросхема з дозволом по виходу

- •§ 1.3. Класифікація та система позначень іс

- •Класифікація інтегральних схем по функціональній ознаці

- •Системи позначень інтегральних схем

- •§ 1.4. Сполучення інтегральних схем

- •Глава 2. Проектування цифрових схем комбінаційного типу

- •§ 2.1. Проблеми проектування цк комбінаційного типу

- •§ 2.2. Логічні елементи

- •§ 2.3. Драйвери

- •§ 2.4. Шифратори, дешифратори,

- •§ 2.5. Арифметичні пристрої

- •Глава 3. Проектування цифрових схем послідовного типу

- •§ 3.1. Проблеми й методики проектування послідовних схем

- •§ 3.2. Тригери

- •Що спрацьовує по від’ємному фронту синхросигналу

- •(Керування по додатному фронту)

- •Практикум 6

- •§ 3.3. Регістри

- •§ 3.4. Лічильники

- •Вироблення сигналу скидання для двійково-десяткового лічильника (б)

- •Глава 4. Електронна пам'ять

- •§ 4.1. Класифікація й система параметрів

- •§ 4.2. Побудова оперативної пам’яті

- •§ 4.3. Постійна пам’ять

- •Багатовходового логічного елемента (а) та плм (б)

- •Перемикаючих функцій

- •Глава 5. Релаксаційні пристрої

- •§ 5.1. Система синхронізації

- •§ 5.2. Генератори та формувачі імпульсів

- •Я, схема на ле та діаграма роботи

- •Бібліографічний список

Що спрацьовує по від’ємному фронту синхросигналу

D-тригер (тригер затримки)

D-delay.

D-тригери поділяються на два типи:

1. D-тригер;

2. D-тригер з динамічним керуванням.

D-вхід даних. По синхроімпульсу D-тригер приймає на вході Q той стан, який він має на вході, але з затримкою по часу. На базі D-тригеру будуються лічильники та регістри.

Рис.3.14. D-тригер на базі RS-тригера

D |

С |

Q |

0 0 1 1 |

0 1 0 1 |

зберігання 0 зберігання 1 |

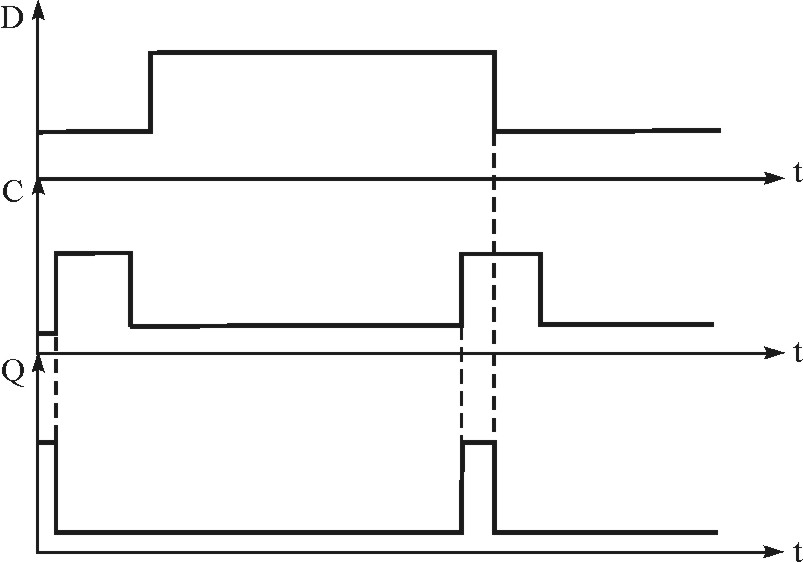

Рис.3.15. Часова діаграма роботи D-тригера

D-тригер з динамічним керуванням

Вихідний сигнал D-тригера з динамічним керуванням перемикається тільки під час додатного або тільки під час від’ємного фронту сигналу С на вході. Напрямок зміни С, по якому записується інформація, визначається нахилом риски на схемі.

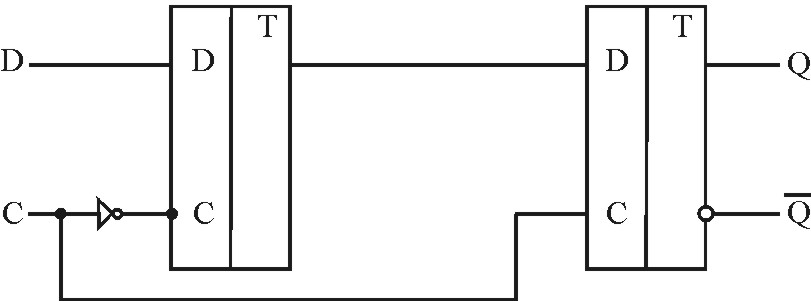

Рис.3.16. Структура динамічного D-тригера по додатному перепаду

Рис.3.17. D-тригер на базі RS з інверсним керуванням

(Керування по додатному фронту)

Рис.3.18. Часова діаграма

К 555 ТМ 2

Таблиця істинності роботи схеми К555ТМ2

Режим роботи |

Входи |

Виходи |

||||

|

|

D |

C |

Q |

|

|

1. асинхронний, який установився |

0 |

1 |

х |

х |

1 |

0 |

2. асинхронний |

1 |

0 |

х |

х |

0 |

1 |

3. невизначеність |

0 |

0 |

х |

х |

1 |

1 |

загрузка «1» |

1 |

1 |

1 |

|

1 |

0 |

загрузка «0» |

1 |

1 |

0 |

|

0 |

1 |

Логічна структура одного D-тригера містить:

основний асинхронний RS-тригер;

додатковий синхронний RS-тригер запису логічної одиниці у основний тригер;

додатковий синхронний RS-тригер запису логічного нуля у основний тригер.

Входи і працюють незалежно від сигналу на тактовому вході.

Асинхронна

установка D-тригера

здійснюється подачею взаємопротилежних

сигналів на входи

і

.

У цей час входи D

і С

на роботу схеми не впливають. Якщо на

і

одночасно подати логічні нулі, то на

виходах будуть логічні одиниці. Після

зняття цих сигналів з

і

стан

тригера буде невизначеним (на виході

рівноймовірно установиться якесь стійке

значення, тому

![]() заборонено).

заборонено).

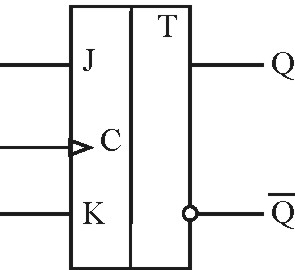

JK-тригер (універсальний RS-тригер)

JK-тригер працює аналогічно RS-тригеру, але при подачі забороненої комбінації перекидається у протилежний стан.

Абревіатура JK-тригера утворена від слів: jerk – швидко ввімкнути;

kill – швидко вимкнути.

Рис.3.19. Схема JK-тригера на базі синхронного RS та його графічне зображення

Таблиця істинності роботи JK-тригера

J |

K |

|

|

0 0 1 1 |

0 1 0 1 |

зберігання 0 1

|

зберігання 1 0

|