- •Частина 1. Основи цифрової схемотехники

- •§ 1.1. Загальні поняття та визначення

- •§ 1.2. Математичні основи побудови цифрових логічних схем

- •§ 1.3. Логічні функції однієї та двох змінних

- •§ 1.4. Аксіоми та закони алгебри логіки

- •§ 1.5. Суперпозиція логічних функцій

- •§ 1.6. Нормальні і досконалі нормальні форми логічних функцій

- •Практикум 1

- •§ 1.7. Застосування матриць Карно для зображення

- •§ 1.8. Побудова схем на логічних елементах з обмеженою

- •Практикум 2.

- •Глава 2. Проектування цифрових схем комбінаційного типу

- •§ 2.1. Проблеми проектування цу комбінаційного типу

- •Що реалізуються, дднф та дкнф

- •Що реалізуються, дднф та дкнф

- •Практикум 3

- •§ 2.2. Суматори

- •§ 2.3. Побудови комбінаційних схем на базі комутаторів

- •§ 2.4. Селектор-демультиплексор

- •§ 2.5. Виникнення змагань і спосіб їх усунення

- •Практикум 4

- •Глава 3. Послідовна логіка

- •§ 3.1. Часові булеві функції

- •§ 3.2. Булеві функції і роду

- •§ 3.3. Булеві функції іі роду

- •Практикум 5

- •Частина 2. Розробка та проектування цифрових пристроїв

- •Глава 1. Класифікація, технології та сполучення інтегральних схем

- •§ 1.1. Технології та форми представлення інформації

- •§ 1.2. Схемотехніка базових елементів ттл-логіки

- •Та його схемо технічне зображення

- •Та таблиця істинності його роботи

- •Інтегральна мікросхема з дозволом по виходу

- •§ 1.3. Класифікація та система позначень іс

- •Класифікація інтегральних схем по функціональній ознаці

- •Системи позначень інтегральних схем

- •§ 1.4. Сполучення інтегральних схем

- •Глава 2. Проектування цифрових схем комбінаційного типу

- •§ 2.1. Проблеми проектування цк комбінаційного типу

- •§ 2.2. Логічні елементи

- •§ 2.3. Драйвери

- •§ 2.4. Шифратори, дешифратори,

- •§ 2.5. Арифметичні пристрої

- •Глава 3. Проектування цифрових схем послідовного типу

- •§ 3.1. Проблеми й методики проектування послідовних схем

- •§ 3.2. Тригери

- •Що спрацьовує по від’ємному фронту синхросигналу

- •(Керування по додатному фронту)

- •Практикум 6

- •§ 3.3. Регістри

- •§ 3.4. Лічильники

- •Вироблення сигналу скидання для двійково-десяткового лічильника (б)

- •Глава 4. Електронна пам'ять

- •§ 4.1. Класифікація й система параметрів

- •§ 4.2. Побудова оперативної пам’яті

- •§ 4.3. Постійна пам’ять

- •Багатовходового логічного елемента (а) та плм (б)

- •Перемикаючих функцій

- •Глава 5. Релаксаційні пристрої

- •§ 5.1. Система синхронізації

- •§ 5.2. Генератори та формувачі імпульсів

- •Я, схема на ле та діаграма роботи

- •Бібліографічний список

ЗМІСТ

ЧАСТИНА 1. ОСНОВИ ЦИФРОВОЇ СХЕМОТЕХНИКИ

Глава 1. Принципи побудови логічних схем

у процесорних системах 4

§ 1.1. Загальні поняття та визначення 4

§ 1.2. Математичні основи побудови цифрових логічних схем 5

§ 1.3. Логічні функції однієї та двох змінних 6

§ 1.4. Аксіоми та закони алгебри логіки 8

§ 1.5. Суперпозиція логічних функцій 9

§ 1.6. Нормальні і досконалі нормальні форми логічних функцій 11

Практикум 1 13

§ 1.7. Застосування матриць Карно для зображення

та перетворення логічних функцій 17

§ 1.8. Побудова схем на логічних елементах з обмеженою

кількістю входів 20

Практикум 2 20

Глава 2. Комбінаційна логіка 23

§ 2.1. Дешифратори 23

Практикум 3 25

§ 2.2. Суматори 27

§ 2.3. Побудови комбінаційних схем на базі комутаторів

(мультиплексорів) 30

§ 2.4. Селектор-демультиплексор 34

§ 2.5. Виникнення змагань і спосіб їх усунення 36

Практикум 4 37

Глава 3. Послідовна логіка 39

§ 3.1. Часові булеві функції 39

§ 3.2. Булеві функції І роду 42

§ 3.3. Булеві функції ІІ роду 42

Практикум 5 44

ЧАСТИНА 2. РОЗРОБКА ТА ПРОЕКТУВАННЯ

ЦИФРОВИХ ПРИСТРОЇВ

Глава 1. Класифікація, технології та сполучення

інтегральних схем 46

§ 1.1. Технології та форми представлення інформації 46

§ 1.2. Схемотехніка базових елементів ТТЛ-логіки 49

§ 1.3. Класифікація та система позначень ІС 54

§ 1.4. Сполучення інтегральних схем 58

Глава 2. Проектування цифрових схем комбінаційного типу 59

§ 2.1. Проблеми проектування ЦК комбінаційного типу 59

§ 2.2. Логічні елементи 62

§ 2.3. Драйвери 65

§ 2.4. Шифратори, дешифратори, мультиплексори

й демультиплексори 66

§ 2.5. Арифметичні пристрої 70

Глава 3. Проектування цифрових схем послідовного типу 75

§ 3.1. Проблеми й методики проектування послідовних схем 75

§ 3.2. Тригери 78

Практикум 6 92

§ 3.3. Регістри 93

§ 3.4. Лічильники 100

Глава 4. Електронна пам'ять 112

§ 4.1. Класифікація й система параметрів

запам’ятовуючих пристроїв 112

§ 4.2. Побудова оперативної пам’яті 115

§ 4.3. Постійна пам’ять 120

Глава 5. Релаксаційні пристрої 125

§ 5.1. Система синхронізації 125

§ 5.2. Генератори та формувачі імпульсів 127

БІБЛІОГРАФІЧНИЙ СПИСОК 130

ДОДАТОК 1 132

ДОДАТОК 2 136

ДОДАТОК 3 148

ДОДАТОК 4 170

ДОДАТОК 5 177

ДОДАТОК 6 182

ДОДАТОК 7 187

Частина 1. Основи цифрової схемотехники

Глава 1. Принципи побудови логічних схем у процесорних системах

§ 1.1. Загальні поняття та визначення

Схемотехніка – це сукупність:

фізично обґрунтованих принципів реалізації схемних елементів,

процесів передачі сигналів у лініях зв’язку,

функціонально обґрунтованих принципів реалізації структури з схемних елементів,

набір угод про форми представлення інформації і правил організації схемних (фізичних) інтерфейсів.

Схемний елемент – електронний (або електричний) пристрій або функціонально закінчений вузол, придатний до об’єднання у відповідності з правилами схемних інтерфейсів.

Схемний (фізичний) інтерфейс – це узгодження про значення (діапазонах значень) фізичного носія інформації, що допускаються при взаємних об’єднаннях схемних елементів.

Велика інтегральна схема (ВІС) – над мініатюрна електронна схема на напівпровідниковій пластинці площею менш 1 см2, що містить сотні й тисячі електронних елементів та виконує певні функції.

Мікропроцесор – програмно-керований електронний пристрій, призначений для обробки цифрової інформації і побудований на одній або декількох ВІС.

Мікропроцесорний комплекс – сукупність ВІС та інших інтегральних мікросхем, які співпадають одна з одною за конструкцією й технічному використанню та призначених для спільного використання.

§ 1.2. Математичні основи побудови цифрових логічних схем

Логічна функція – це функція, яка, як і її аргументи, логічні змінні, може приймати тільки два значення – «0» або «1».

Логічний «0» символізує розімкнений ланцюг, відсутність сигналу, «неправда», низький рівень сигналу.

Логічна «1» символізує замкнений ланцюг, наявність сигналу, «істина», високий рівень сигналу.

У залежності від кількості вхідних змінних розрізняють функції однієї, двох або декількох змінних.

Набор – це комбінація значень логічних змінних.

Задати логічну функцію означає визначити її значення для всіх наборів вхідних змінних.

Функція вважається повністю заданою, якщо визначені її значення для всіх наборів.

Одним із способів завдання логічної функції є завдання її за допомогою таблиці істинності.

Приклад 1.

А |

В |

Х |

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

На рисунку для прикладів 1(2):

А, В, (С) – вхідні змінні;

Х –вихідна функція.

Приклад 2.

А |

В |

С |

Х |

0 0 0 1 1 1 0 1 |

0 0 1 0 1 0 1 1 |

0 1 0 0 0 1 1 1 |

0 1 1 0 0 1 0 1 |

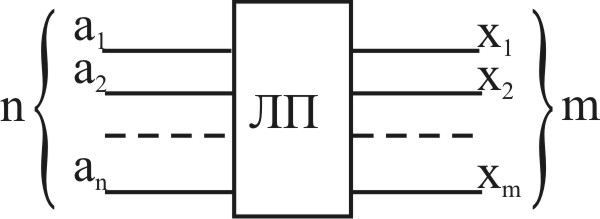

Логічно будь-яку цифрову схему можна представити у вигляді:

n, m – кількість вхідних змінних – (n) та вихідних функцій (m);

ЛП – логічний пристрій;

![]() – максимально

можлива кількість комбінацій вхідних

змінних;

– максимально

можлива кількість комбінацій вхідних

змінних;

![]() – максимально

можлива кількість функцій.

– максимально

можлива кількість функцій.