- •Архитектура системного уровня процессоров ia-32 Задачи архитектуры системного уровня (system-level architecture)

- •Компоненты архитектуры системного уровня

- •Защищенный режим Общие сведениия Назначение защищенного режима микропроцессоров ia-32

- •Режим виртуального процессора 8086

- •Концепция защиты

- •Дескрипторы и таблицы дескрипторов. Системные сегменты

- •Регистры дескрипторов таблиц и системных сегментов

- •Механизм использования глобальной и локальной таблиц дескрипторов

- •Привилегии

- •Кольца защиты Привилегии задач (Task Privilege)

- •Привилегии дескриптора (Descriptor Privilege)

- •Привилегии селектора (Selector Privilege)

- •Привилегии ввода-вывода

- •Дескрипторы системных сегментов

- •Поля байта управления доступом к системным сегментам

- •Межсегментная передача управления

- •Типы и назначение шлюзов

- •Механизм использования шлюза вызова

- •Дескриптор шлюза вызова

- •Поля байта управления доступом дескриптора шлюза

- •Проверка условий, порождающих исключения

- •Инструкции тестирования указателей

- •Виртуальная память

- •Составляющие элементы механизма страничной переадресации

- •Адресация в защищенном режиме

- •Варианты организации страниц виртуальной памяти

- •Управление режимом страничной переадресации

- •Переключение стека

- •Операция переключения задач процессора (Task Switch Operation)

- •Переключение между реальным и защищенным режимами

- •Переключение в защищенный режим из реального:

- •Переключение процессора в реальный режим из защищенного

- •Регистры управления cr1, cr2, cr3

- •Регистр управления cr4

- •Управление прерываниями от fpu

- •Управление блоком fpu

- •Средства отладки по

- •Регистры отладки

- •Средства, предоставляющие дополнительные возможности отладки.

- •Регистр DebugCtlMsr:

- •Режим управления системой (smm)

- •Включение режима

- •Карта контекста процессора в smram

- •Идентификатор smm (Revision Identifier)

- •Базовый адрес smram

- •Некорректность восстановления контекста

- •Инициализация регистров процессора при входе в smm

- •Начальный сброс и тестирование Аппаратный сброс (hardware reset)

- •Установки при сбросе

- •Внутренний тест процессора

- •Начало нормального функционирования процессора

- •Инициализация по сигналу init («мягкий» сброс)

- •Тестирование аппаратных средств процессора

Регистры управления cr1, cr2, cr3

PCD (Page-Level Cache Disable) – запрет кэширования страницы (один из источников сигнала #CD для управления внешним кэшем);

PWT (Page-Level Writes Trough) – кэширование страницы со сквозной записью (один из источников сигнала PWT для управления внешним кэшем).

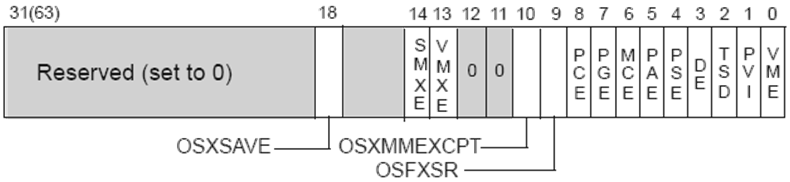

Регистр управления cr4

DE (Debugging Extensions) – расширение возможностей отладки (разрешение останова при обращении к заданным портам ввода-вывода).

MCE (Machine-Check Enable) – разрешение машинного контроля (Р5+) à исключение #МС по машинной ошибке.

VME (Virtual-8086 Mode Extensions) – разрешение использования виртуального флага прерываний в режиме V86 à сокращение лишних вызовов монитора виртуальных машин.

PVI (Protected-Mode Virtual Interrupts) – разрешение использования виртуального флага прерываний в защищенном режиме.

TSD (Time Stamp Disable) – превращение инструкции RDTSC в привилегированную.

РСЕ (Performance-monitoring Counter Enable) – разрешение обращения к счетчикам событий (инструкция RDPMC) на любом уровне привилегий.

PSE (Page Size Extension) – расширение размера страницы (4 Мбайт).

РАЕ (Physical Address Extension) – расширение физического адреса (страницы 2 Мбайт, 36-бит).

PGE (Paging Global Extensions) – глобальность в страничной переадресации (Р6+). При PGE=1 по команде MOV CR3 в TLB очищаются только вхождения с неустановленным битом глобальности G.

OSFXSR – флаг разрешения инструкций FXSAVE/FXRSTOR (Р6+); устанавливается ОС (при инициализации =0). Признак поддержки инструкции процессором – бит FXSR (EDX.24) после вызова CPUID(1).

OSXMMEXCPT – флаг поддержки ОС исключений от блока ХММ (Р6+).

OSXSAVE (XSAVE and Processor Extended States-Enable) – разрешение использования инструкций XSETBV/XGETBV, XSAVE/XRSTOR.

VMXE (VMX Enable) – разрешает функции VMX (virtual-machine extensions).

SMXE (SMX Enable) – разрешает функции SMX (Safer Mode Extensions).

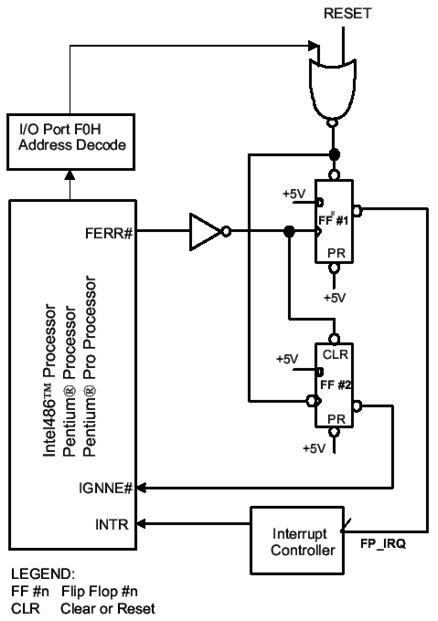

Управление прерываниями от fpu

Управление блоком fpu

NE Numeric Error (CR0.5);

ET Extension Type (CR0.4);

TS Task Switched (CR0.3);

EM Emulation (CR0.2);

MP Monitor Coprocessor (CR0.1).

Средства отладки по

Назначение: передать управление программе-отладчику по наступлению указанного события:

исполнение инструкции ___ _____________ _________;

обращение к _________ _________ или _______ _______-_________;

выполнение очередной инструкции.

Программа-отладчик (debugger) позволяет:

проанализировать и/или модифицировать состояние процессора, памяти и портов в точке останова;

продолжить исполнение отлаживаемой программы, задав новые условия останова.

Передача управления отладчику

исключение 1 (#DB, Debug exception) – __________ __________;

исключение 3 (#ВР, BreakPoint exception) – передача управления отладчику по _______________ ____ _.

Задание событий отладки

______ ___ (______) в регистре EFLAGS – генерация исключения #DB после исполнения любой инструкции;

______ _ (______) в TSS – генерация исключения #DB при переключении на задачу с установленным флагом (286+);

регистры отладки ____-____, ____, ____ – генерация исключения #DB по заданным адресам памяти (386+) и ввода-вывода (Pentium+).