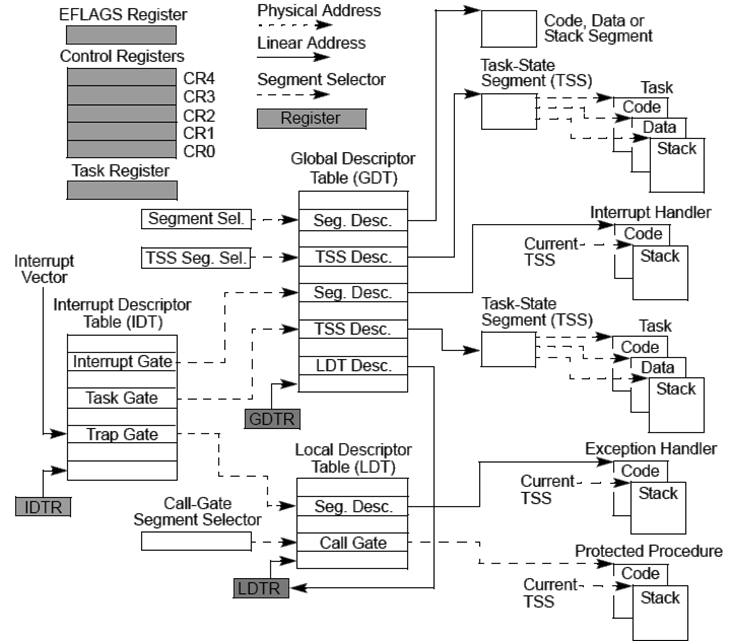

- •Архитектура системного уровня процессоров ia-32 Задачи архитектуры системного уровня (system-level architecture)

- •Компоненты архитектуры системного уровня

- •Защищенный режим Общие сведениия Назначение защищенного режима микропроцессоров ia-32

- •Режим виртуального процессора 8086

- •Концепция защиты

- •Дескрипторы и таблицы дескрипторов. Системные сегменты

- •Регистры дескрипторов таблиц и системных сегментов

- •Механизм использования глобальной и локальной таблиц дескрипторов

- •Привилегии

- •Кольца защиты Привилегии задач (Task Privilege)

- •Привилегии дескриптора (Descriptor Privilege)

- •Привилегии селектора (Selector Privilege)

- •Привилегии ввода-вывода

- •Дескрипторы системных сегментов

- •Поля байта управления доступом к системным сегментам

- •Межсегментная передача управления

- •Типы и назначение шлюзов

- •Механизм использования шлюза вызова

- •Дескриптор шлюза вызова

- •Поля байта управления доступом дескриптора шлюза

- •Проверка условий, порождающих исключения

- •Инструкции тестирования указателей

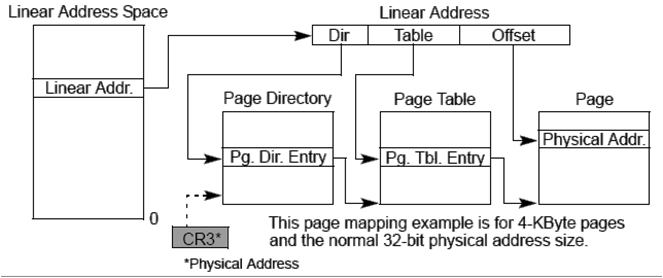

- •Виртуальная память

- •Составляющие элементы механизма страничной переадресации

- •Адресация в защищенном режиме

- •Варианты организации страниц виртуальной памяти

- •Управление режимом страничной переадресации

- •Переключение стека

- •Операция переключения задач процессора (Task Switch Operation)

- •Переключение между реальным и защищенным режимами

- •Переключение в защищенный режим из реального:

- •Переключение процессора в реальный режим из защищенного

- •Регистры управления cr1, cr2, cr3

- •Регистр управления cr4

- •Управление прерываниями от fpu

- •Управление блоком fpu

- •Средства отладки по

- •Регистры отладки

- •Средства, предоставляющие дополнительные возможности отладки.

- •Регистр DebugCtlMsr:

- •Режим управления системой (smm)

- •Включение режима

- •Карта контекста процессора в smram

- •Идентификатор smm (Revision Identifier)

- •Базовый адрес smram

- •Некорректность восстановления контекста

- •Инициализация регистров процессора при входе в smm

- •Начальный сброс и тестирование Аппаратный сброс (hardware reset)

- •Установки при сбросе

- •Внутренний тест процессора

- •Начало нормального функционирования процессора

- •Инициализация по сигналу init («мягкий» сброс)

- •Тестирование аппаратных средств процессора

Операция переключения задач процессора (Task Switch Operation)

сохранение состояния процессора и связи с предыдущей задачей;

загрузка состояния новой задачи и переход к ее выполнению.

Варианты:

____________ _________ _____________ _ ___. Состояние текущей задачи автоматически сохранится в ее TSS, а в процессор загрузится состояние новой (возможно, ранее прерванной) задачи и начнется (продолжится) ее выполнение;

_______________ _______________ _____________________ ____________ (JMP) или _________ (CALL), ссылающейся на TSS или дескриптор шлюза задачи в GDT или LDT;

__________________ _______________ или _______________, если соответствующий элемент в IDT является дескриптором шлюза задачи.

Инструкции CALL, JMP, INT:

старый (кроме случая JMP) и новый TSS помечаются как занятые (модифицируется TYPE в дескрипторах);

в поле обратной ссылки в новом TSS устанавливается значение селектора старого TSS.

Бит NT:

устанавливается в новой задаче инструкциями ______ и ____, переключающими задачи;

сбрасывается ________________, не вызывающим переключения задач;

может устанавливаться и сбрасываться инструкциями ______ и ______.

Переключение между реальным и защищенным режимами

По умолчанию: процессор работает в реальном режиме, с 16-разрядными адресами и данными.

Переключение в защищенный режим из реального:

загрузка в ____ слова с единичным значением бита РЕ (Protect Enable);

или установка бита РЕ инструкцией ______ (для совместимости с ПО 80286).

До переключения: в памяти должны быть сформированы IDT и GDT.

Сразу после переключения: CPL=_.

Переключение процессора в защищенный режим из реального

1. Запрет маскируемых и немаскируемых прерываний.

2. Инициализация ______.

3. Установка флага РЕ, флага ___ (если требуется страничное управление памятью*).

4. Дальний переход (____) или вызов (______)**.

*коды инструкций MOV CR0 и JMP/CALL должны находиться в странице, для которой физический адрес совпадает с логическим.

5. Инициализация (если требуется LDT) регистра LDTR.

6. Загрузка в TR _____________ ____ для начальной задачи защищенного режима.

7. Перезагрузка сегментных регистров (кроме CS), содержимое которых относится к реальному режиму, или выполнение ____________/_________ задачи (регистры перезагружаются автоматически).

8. Инициализация регистра ______.

9. Разрешение маскируемых и немаскируемых аппаратных прерываний.

Переключение процессора в реальный режим из защищенного

1. Запрет маскируемых и немаскируемых прерываний.

2. Если включена страничная трансляция:

обеспечить равенство линейных и физических адресов для:

текущего исполняемого кода (перейти на такую страницу);

таблиц ____ _ ____;

обнулить:

бит ___ в регистре CR0;

поля регистра ____ для очистки TLB.

3. Передать управление читаемому сегменту с лимитом 64 Кбайт.

4. Загрузка* в сегментные регистры SS, DS, ES, FS и GS селектора дескриптора (ненулевой), в котором Limit=64 Кбайт, G=0, Е=0, W=1, Р=1.

5. Формирование IDT реального режима (в пределах первого мегабайта) и инициализация IDTR.

6. Сброс бита ___.

7. Выполнение ____________ ____________ на программу реального режима**.

8. Инициализация сегментных регистров и указателя стека.

9. Разрешение прерываний.

10. Загрузка остальных регистров.

Аппаратные средства системной архитектуры

Модель архитектуры системного уровня IA-32

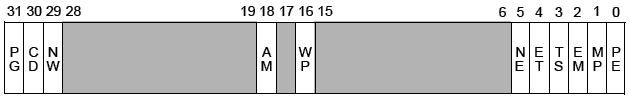

Регистры управления

Управляющие регистры (Control Registers) CR0, CR1, CR2, CR3.

Хранят признаки состояния процессора, общие для всех задач.

Регистр управления CR0

РЕ (Protection Enable) – разрешение защиты.

TS (Task Switch) – ______ __________________ _______; устанавливается автоматически при переключении задач, сбрасывается инструкцией CLTS.

ЕМ (Processor Extension Emulated) – ____________ __________________. EM=1 à исключение #NM (или прерывания от сопроцессора) при каждой команде, относящейся к сопроцессору.

MP (Monitor Processor Extension) – _______________ __________________. MP=1 à исключение #NM по первой ожидающей инструкции FPU после переключения задач (при TS=1) для сохранения и восстановления _____________ __________________.

МР=1, ЕМ=0: при наличии сопроцессора.

МР=0, ЕМ=1: при программной эмуляции сопроцессора.

После сброса: МР=0, ЕМ=0, TS=0 à полная совместимость с 8086/88 (#NM не вырабатывается).

ЕТ (Extension Туре) – индикатор поддержки инструкций АСП; используется в 486+, для 486SX ЕТ=0, для остальных – ЕТ=1.

NE (Numeric Error) – разрешение __________________ (для Intel, но не для PC) механизма сообщения об ошибке FPU через генерацию исключения (486+).

AM (Alignment Mask) – разрешение контроля выравнивания (возможен только на уровне привилегий 3 при АМ=1 и АС=1).

WP (Write Protect) – разрешение _________ __________ _________.

NW (Not Write-through) – запрет сквозной записи кэша и циклов аннулирования.

CD (Cache Disable) – запрет _______________ ______ (попадания в ранее заполненные строки при этом обслуживаются кэшем).

PG (Paging Enable) – включение механизма страничной переадресации памяти.