- •Архитектура системного уровня процессоров ia-32 Задачи архитектуры системного уровня (system-level architecture)

- •Компоненты архитектуры системного уровня

- •Защищенный режим Общие сведениия Назначение защищенного режима микропроцессоров ia-32

- •Режим виртуального процессора 8086

- •Концепция защиты

- •Дескрипторы и таблицы дескрипторов. Системные сегменты

- •Регистры дескрипторов таблиц и системных сегментов

- •Механизм использования глобальной и локальной таблиц дескрипторов

- •Привилегии

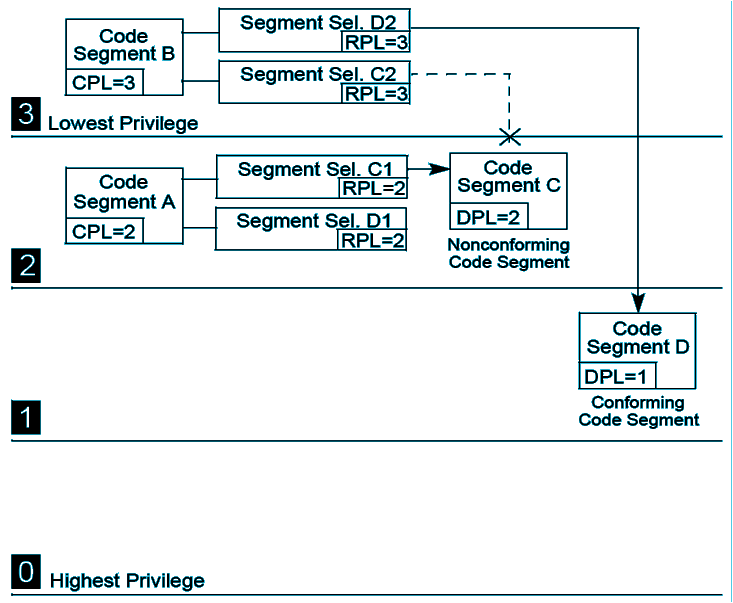

- •Кольца защиты Привилегии задач (Task Privilege)

- •Привилегии дескриптора (Descriptor Privilege)

- •Привилегии селектора (Selector Privilege)

- •Привилегии ввода-вывода

- •Дескрипторы системных сегментов

- •Поля байта управления доступом к системным сегментам

- •Межсегментная передача управления

- •Типы и назначение шлюзов

- •Механизм использования шлюза вызова

- •Дескриптор шлюза вызова

- •Поля байта управления доступом дескриптора шлюза

- •Проверка условий, порождающих исключения

- •Инструкции тестирования указателей

- •Виртуальная память

- •Составляющие элементы механизма страничной переадресации

- •Адресация в защищенном режиме

- •Варианты организации страниц виртуальной памяти

- •Управление режимом страничной переадресации

- •Переключение стека

- •Операция переключения задач процессора (Task Switch Operation)

- •Переключение между реальным и защищенным режимами

- •Переключение в защищенный режим из реального:

- •Переключение процессора в реальный режим из защищенного

- •Регистры управления cr1, cr2, cr3

- •Регистр управления cr4

- •Управление прерываниями от fpu

- •Управление блоком fpu

- •Средства отладки по

- •Регистры отладки

- •Средства, предоставляющие дополнительные возможности отладки.

- •Регистр DebugCtlMsr:

- •Режим управления системой (smm)

- •Включение режима

- •Карта контекста процессора в smram

- •Идентификатор smm (Revision Identifier)

- •Базовый адрес smram

- •Некорректность восстановления контекста

- •Инициализация регистров процессора при входе в smm

- •Начальный сброс и тестирование Аппаратный сброс (hardware reset)

- •Установки при сбросе

- •Внутренний тест процессора

- •Начало нормального функционирования процессора

- •Инициализация по сигналу init («мягкий» сброс)

- •Тестирование аппаратных средств процессора

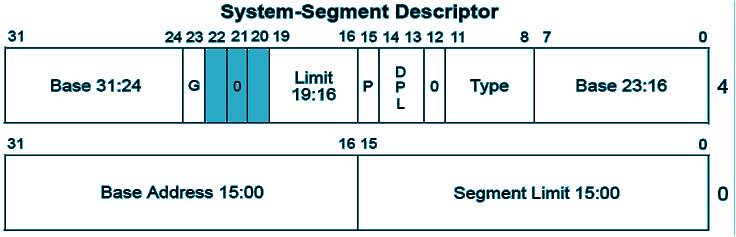

Дескрипторы системных сегментов

Поля байта управления доступом к системным сегментам

Р – действительность (Р=1) или недействительность (Р=0) содержимого сегмента.

DPL – только в дескрипторах TSS.

Туре (0-3, 8-В) – тип сегмента:

0 |

недопустимое значение |

8 |

недопустимое значение |

1 |

доступный TSS процессора 80286 (Available TSS-286) |

9 |

доступный TSS процессора 386+ (Available TSS-386) |

2 |

____ |

А |

не определено (зарезервировано) |

3 |

занятый TSS процессора 80286 (Busy TSS-286) |

В |

занятый TSS процессора 386+ (Busy TSS-386) |

Межсегментная передача управления

Варианты:

________________________ (командами JMP, CALL, INT, RET и IRET) – без изменения CPL к сегментам кода с уровнем привилегий:

равным CPL;

более высоким (если сегмент подчинен);

_____________ (посредством шлюзов различных типов) – с изменением CPL.

Типы и назначение шлюзов

шлюз _________ (Call Gate) – вызов процедур со сменой уровня привилегий. Позволяет автоматически копировать заданное число слов из старого стека в новый;

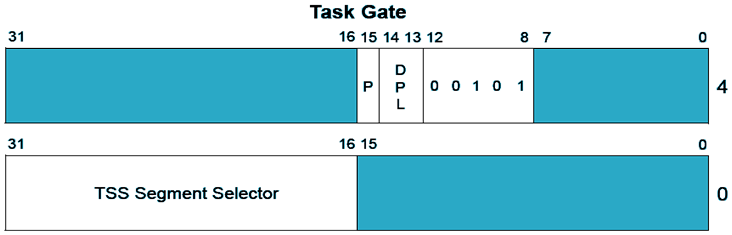

шлюз _________ (Task Gate) – переключение задач;

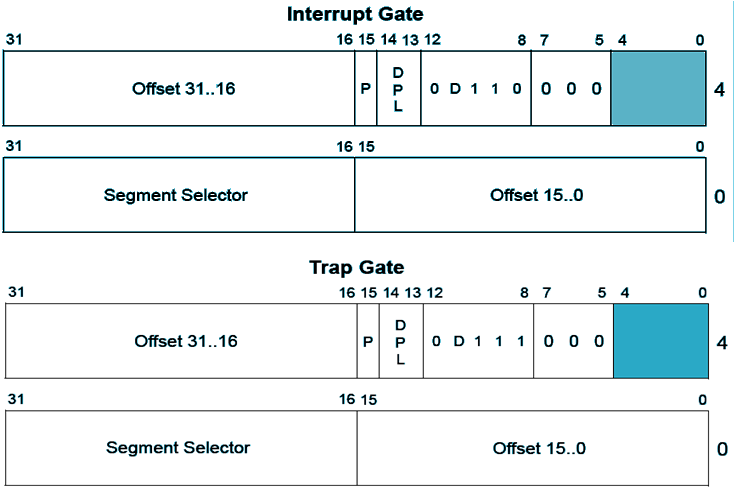

шлюз _______________ (Interrupt Gate) и шлюз __________ (Trap Gate) – определяют процедуры обслуживания прерываний. Шлюз прерывания запрещает аппаратные маскируемые прерывания, сбрасывая флаг IF.

Для каждого типа шлюза используется соответствующий дескриптор (Gate Descriptor).

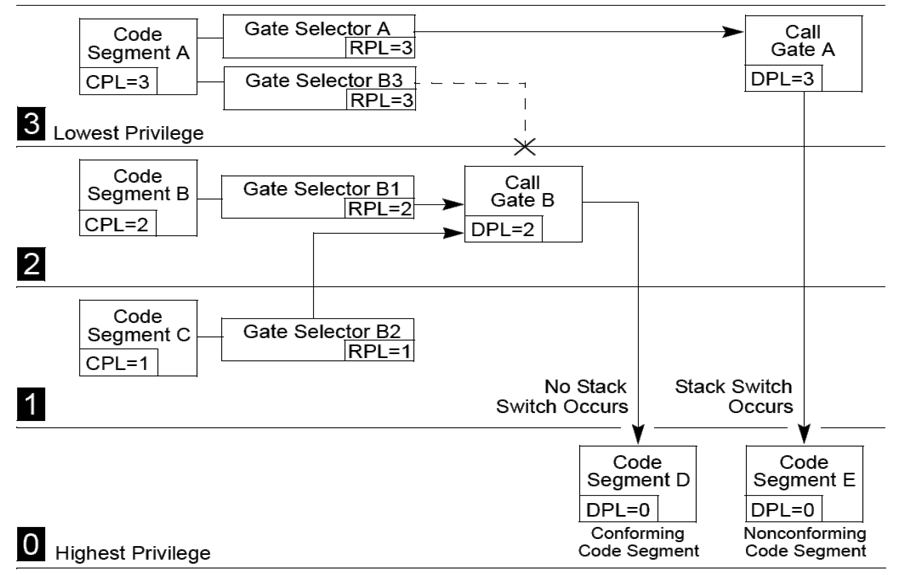

Механизм использования шлюза вызова

Дескриптор шлюза вызова

Segment Selector – селектор целевого ____________ ______ (для шлюзов вызова, прерываний и ловушек) либо селектор целевого ____ (для шлюза задачи);

Offset in Segment – смещение (адрес) _______ _______ в целевом сегменте;

Param. Count (в шлюзах вызовов) – число слов, автоматически копируемых из стека вызывающего процесса в стек вызываемой процедуры. Для сегментов 80286 слова 16-битные, для 386+ – 32-битные.

Поля байта управления доступом дескриптора шлюза

Р – действительность (Р=1) или недействительность (Р=0) шлюза.

DPL – уровень привилегий.

Туре – тип шлюза:

4 |

шлюз вызова 80286 |

C |

шлюз вызова 386+ |

5 |

шлюз задачи (16- и 32-разрядной) |

D |

зарезервирован |

6 |

шлюз прерывания 80286 |

E |

шлюз прерывания 386+ |

7 |

шлюз ловушки 80286 |

F |

шлюз ловушки 386+ |

Структура дескрипторов шлюзов прерываний и ловушек

Структура дескриптора шлюза задачи

Контроль доступа

Контроль доступа к сегментам данных

Производится при загрузке селекторов в сегментные регистры SS, DS, ES, FS и GS:

команды загрузки DS, ES, FS и GS должны ссылаться на дескрипторы сегментов _________ или сегментов ______, допускающих чтение, EPL≤DPL;

команды загрузки SS должны ссылаться на дескриптор сегмента данных, допускающий _________, DPL=RPL=CPL.

Контроль доступа при передаче управления

Производится при загрузке селектора в регистр CS.

Тип ссылочного дескриптора должен соответствовать выполняемой инструкции:

JMP или CALL:

подчиненный сегмент кода с DPL≤CPL;

неподчиненный сегмент с DPL=CPL;

_______________ внутри задачи или _________, которые могут изменить уровень привилегий:

кодовый сегмент с DPL_CPL, только через шлюзы с DPL_CPL;

инструкции возврата, которые не переключают задачи:

кодовый сегмент с DPL_CPL;

__________________ _______ с помощью вызова, перехода или прерывания:

шлюз задачи или TSS с DPL_CPL.