- •1.1. Микропроцессор и его архитектура

- •1.2. Типы мп бис

- •1.3. Универсальные микропроцессоры и их основные характеристики

- •1.4. Однокристальные микроконтроллеры: особенности архитектуры, основные характеристики, область применения.

- •2.1. Структура мк-51. Основные функциональные блоки и их назначение

- •2.2. Организация памяти программ и памяти данных

- •1. Память данных:

- •2. Память программ:

- •2.3. Аппаратные и программные средства микроконтроллера для обработки битовой информации

- •1. Аппаратные.

- •2. Программные.

- •2.4. Система прерывания

- •2.5. Блок таймеров/счетчиков: назначение, структура, режимы работы, применение

- •2.6. Организация последовательного ввода/вывода в микроконтроллере

- •3.1. Структура универсального мп. Основные функциональные блоки и их назначение.

- •3.2. Регистровая структура 32-разрядного мп

- •1 ) Основные функциональные регистры

- •1.1) Регистры общего назначения

- •3.1) Регистры управления.

- •3 .2) Регистры системных адресов и системных сегментов

- •3.3. Организация памяти. Физическое адресное пространство. Логическое адресное пространство (лап): линейное, сегментированное, страничное, сегментно-страничное

- •3.5. Структура расширенного кода команды x86. Вычисление процессором смещения

- •3.8. Механизмы защиты в 32-разрядном микропроцессоре. Защита при управлении памятью. Защита по привилегиям. Механизмы передачи управления между программами на разных уровнях привилегий. Шлюз вызова

- •3.9. Многозадачный режим работы мп, аппаратные средства поддержки многозадачности: регистр задачи, дескриптор сегмента состояния задачи, сегмент состояния задачи. Механизм переключения задач

- •3.10. Назначение, принципы работы и организация кэш-памяти. Типы кэш-памяти. Способы организации кэширования (сквозная и обратная запись). Организация внутренней кэш-памяти

- •3.13. Обмен информацией в режиме прямого доступа в память. Структура и функционирование контроллера прямого доступа в память. Каскадное включение контроллеров прямого доступа в память.

- •3.14. Функции чипсета. Структура микропроцессорной системы при использовании чипсета.

- •4.1. Организация конвейерной обработки информации в мп: структура классического конвейера, оценка производительности мп при конвейерной обработке

- •4.2. Конфликты в конвейере. Влияние конфликтов на производительность процессора. Типы конфликтов и способы минимизации их влияния на производительность мп

- •1. Структурные конфликты

- •4.3. Предсказание переходов: назначение, способы, техническая реализация

- •4.4. Неупорядоченное выполнение команд: суть подхода, проблемы, связанные с реализацией метода и пути их преодоления

- •4.5. Особенности архитектуры мп с технологией mmx и sse

- •4.6. Микропроцессор Pentium 4: особенности микроархитектуры, структура и назначение основных блоков, порядок функционирования

- •4.7. Пути повышения производительности микропроцессоров

- •4.8. Основные черты архитектуры epic

- •4.9. Микропроцессор Itanium: структура, архитектурные особенности

- •4.10. Отличительные черты микропроцессоров с risc-архитектурой

- •5.1. Основные конфигурации мультимикропроцессорных систем: smp-системы, numa-системы, кластеры, mpp-системы

- •5.2. Транспьютеры: структура, назначение, организация и порядок функционирования транспьютерных систем

- •6.1. Основные особенности мпс как объектов контроля

- •6.2. Особенности отладки мпс на различных этапах жизненного цикла

- •7.1. Назначение и особенности цифровой обработки сигналов

- •7.2. Основные особенности архитектуры процессоров цифровой обработки сигналов.

- •7.3. Особенности системы команд и программирования процессоров цифровой обработки сигналов.

- •8.1. Классические методы оценки производительности микропроцессоров: по тактовой частоте, mips, mflops. Достоинства, недостатки, область применимости

- •8.2. Оценка производительности микропроцессоров на основе бенчмарков. Тестовая программа Linpack. Тестовые пакеты specCpu, bdti

- •Допвопрос. Структура микропроцессорной системы

- •Для групп в7-12, к7-12в, к7-12с

- •2010-2011 Учебный год

- •I. Общие положения

- •Микропроцессор и его архитектура.

- •2. Однокристальные микроконтроллеры

- •3. Универсальные микропроцессоры

- •4. Структура и особенности функционирования современных микропроцессоров

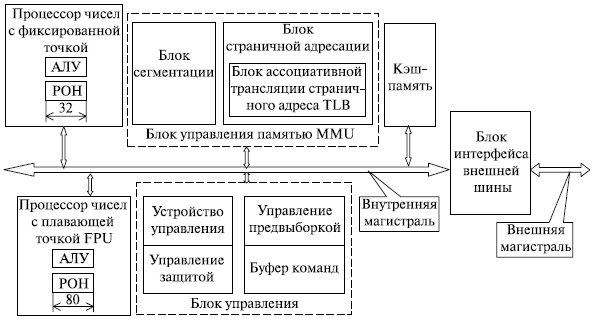

3.1. Структура универсального мп. Основные функциональные блоки и их назначение.

Именно архитектуру i486 можно рассматривать как базовую для IA-32. В нем впервые появились кэш-память и процессор обработки чисел с плавающей точкой.

Процессор обработки чисел с фиксированной точкой:

32-разрядное АЛУ (для обработки двоичных чисел длиной 1, 2 или 4 байта без знака или со знаком, но представленных в дополнительном коде, а также двоично-десятичных, не превышающих 99)

блок регистров общего назначения (содержит восемь 32-разрядных регистров, часть из которых допускает 16- и 8-разрядное обращение)

Процессор обработки чисел с плавающей точкой:

80-разрядное АЛУ

блок из восьми 80-разрядных регистров общего назначения, а также управляющих регистров (для обработки чисел с плавающей точкой, целых чисел со знаком длиной 8 байт и двоично-десятичных чисел величиной от 100 до 99…9 (18 цифр))

На первых этапах развития SIMD-обработки регистры FPU использовались для хранения операндов, представленных в новых форматах

Блок управления памятью (Memory Management Unit — MMU) состоит из двух основных блоков в соответствии с организацией памяти. В общем случае память в МП делится на сегменты, которые, в свою очередь, делятся на страницы.

блок сегментации (или блок сегментного преобразования адреса);

блок страничного преобразования, в состав которого входит т.н. буфер ассоциативной трансляции адресов страниц (TLB).

Кэш-память представляет собой промежуточную ступень между оперативной памятью и регистрами МП и предназначена для хранения наиболее часто используемой информации.

Блок управления: устройство управления под действием кода команды вырабатывает набор управляющих сигналов, поступающих на разные узлы как самого МП, так и на блок интерфейса внешней шины

управление защитой памяти обеспечивает аппаратную защиту программ и данных при управлении памятью и по привилегиям

блок управления предвыборкой команд реализует опережающее заполнение буфера команд, представляющего собой некоторую буферную память. Буфер команд (емкость 32 байта) заполняется командами из следующих ячеек памяти команд по мере своего освобождения, что обеспечивает ускорение обработки МП следующей команды. Данный блок подвергался наиболее существенным переработкам по мере развития IA-32 — причина в широком последующем использовании конвейерной организации работы МП и связанной с этим необходимости совершенствования блока предсказания адреса следующей команды

Блок интерфейса внешней шины осуществляет электрическое согласование параметров внутренней магистрали с сигналами внешних магистралей, формирование необходимых сигналов на внешнюю магистраль и прием сигналов извне. Внешняя магистраль МП состоит из:

шины данных (32 разряда)

32-разрядный адрес передается по 34-разрядной шине адреса А31...А2+(B3,B2,B1,B0). Чтобы с минимальными потерями согласовывать 32-разрядную шину данных с передачей данных меньшей разрядности, младшие разряды адреса (А1 и А0) передаются в дешифрированном виде (B3, B2, B1, B0). Они показывают, какие байты из 32-разрядной шины данных в данный момент реально востребованы: 1 байт, 2 младших байта, 2 старших байта либо все 32 разряда данных

шина управления — 32-разрядная. По ней передаются сигналы записи и чтения содержимого оперативной памяти и внешних устройств, сигналы запросов прерываний, прямого доступа к памяти и т. д.

Особый интерес представляют три режима работы МП:

Реальный режим обеспечивает совместимость на уровне объектных кодов с МП i8086 и МП i286, работающими в реальном режиме. В этом режиме архитектура 32-разрядного МП почти полностью идентична архитектуре 16-разрядного МП. Для программиста же он вообще представляется как МП i8086, выполняющий написанные программы с большей скоростью и обладающий расширенной системой команд и регистрами. Так фирма Intel сохранила прежних клиентов, хотевших модернизировать свои системы, не отказываясь от имевшегося задела в области программного обеспечения, и привлекла тех, кому изначально требовалась высокая скорость обработки информации.

Основное ограничение реального режима — предельная емкость адресуемой памяти равна 1 Мбайт.

Защищенный режим лишен вышесказанного ограничения. Размер адресного пространства в этом случае увеличивается до 4 Гбайт, а общий объем поддерживаемого адресного пространства — до 64 Тбайт. МП в защищенном режиме обладают более высоким быстродействием и возможностями организации истинной многозадачности.

Режим виртуального МП открывает возможность одновременного исполнения программ, написанных для МП i8086, i286 и i386. Поскольку емкость памяти, адресуемой МП, не ограничена значением 1 Мбайт, этот режим позволяет формировать

несколько виртуальных сред i8086.