- •1.1. Микропроцессор и его архитектура

- •1.2. Типы мп бис

- •1.3. Универсальные микропроцессоры и их основные характеристики

- •1.4. Однокристальные микроконтроллеры: особенности архитектуры, основные характеристики, область применения.

- •2.1. Структура мк-51. Основные функциональные блоки и их назначение

- •2.2. Организация памяти программ и памяти данных

- •1. Память данных:

- •2. Память программ:

- •2.3. Аппаратные и программные средства микроконтроллера для обработки битовой информации

- •1. Аппаратные.

- •2. Программные.

- •2.4. Система прерывания

- •2.5. Блок таймеров/счетчиков: назначение, структура, режимы работы, применение

- •2.6. Организация последовательного ввода/вывода в микроконтроллере

- •3.1. Структура универсального мп. Основные функциональные блоки и их назначение.

- •3.2. Регистровая структура 32-разрядного мп

- •1 ) Основные функциональные регистры

- •1.1) Регистры общего назначения

- •3.1) Регистры управления.

- •3 .2) Регистры системных адресов и системных сегментов

- •3.3. Организация памяти. Физическое адресное пространство. Логическое адресное пространство (лап): линейное, сегментированное, страничное, сегментно-страничное

- •3.5. Структура расширенного кода команды x86. Вычисление процессором смещения

- •3.8. Механизмы защиты в 32-разрядном микропроцессоре. Защита при управлении памятью. Защита по привилегиям. Механизмы передачи управления между программами на разных уровнях привилегий. Шлюз вызова

- •3.9. Многозадачный режим работы мп, аппаратные средства поддержки многозадачности: регистр задачи, дескриптор сегмента состояния задачи, сегмент состояния задачи. Механизм переключения задач

- •3.10. Назначение, принципы работы и организация кэш-памяти. Типы кэш-памяти. Способы организации кэширования (сквозная и обратная запись). Организация внутренней кэш-памяти

- •3.13. Обмен информацией в режиме прямого доступа в память. Структура и функционирование контроллера прямого доступа в память. Каскадное включение контроллеров прямого доступа в память.

- •3.14. Функции чипсета. Структура микропроцессорной системы при использовании чипсета.

- •4.1. Организация конвейерной обработки информации в мп: структура классического конвейера, оценка производительности мп при конвейерной обработке

- •4.2. Конфликты в конвейере. Влияние конфликтов на производительность процессора. Типы конфликтов и способы минимизации их влияния на производительность мп

- •1. Структурные конфликты

- •4.3. Предсказание переходов: назначение, способы, техническая реализация

- •4.4. Неупорядоченное выполнение команд: суть подхода, проблемы, связанные с реализацией метода и пути их преодоления

- •4.5. Особенности архитектуры мп с технологией mmx и sse

- •4.6. Микропроцессор Pentium 4: особенности микроархитектуры, структура и назначение основных блоков, порядок функционирования

- •4.7. Пути повышения производительности микропроцессоров

- •4.8. Основные черты архитектуры epic

- •4.9. Микропроцессор Itanium: структура, архитектурные особенности

- •4.10. Отличительные черты микропроцессоров с risc-архитектурой

- •5.1. Основные конфигурации мультимикропроцессорных систем: smp-системы, numa-системы, кластеры, mpp-системы

- •5.2. Транспьютеры: структура, назначение, организация и порядок функционирования транспьютерных систем

- •6.1. Основные особенности мпс как объектов контроля

- •6.2. Особенности отладки мпс на различных этапах жизненного цикла

- •7.1. Назначение и особенности цифровой обработки сигналов

- •7.2. Основные особенности архитектуры процессоров цифровой обработки сигналов.

- •7.3. Особенности системы команд и программирования процессоров цифровой обработки сигналов.

- •8.1. Классические методы оценки производительности микропроцессоров: по тактовой частоте, mips, mflops. Достоинства, недостатки, область применимости

- •8.2. Оценка производительности микропроцессоров на основе бенчмарков. Тестовая программа Linpack. Тестовые пакеты specCpu, bdti

- •Допвопрос. Структура микропроцессорной системы

- •Для групп в7-12, к7-12в, к7-12с

- •2010-2011 Учебный год

- •I. Общие положения

- •Микропроцессор и его архитектура.

- •2. Однокристальные микроконтроллеры

- •3. Универсальные микропроцессоры

- •4. Структура и особенности функционирования современных микропроцессоров

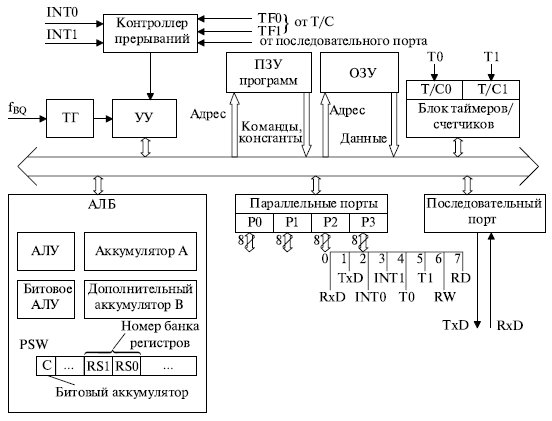

2.1. Структура мк-51. Основные функциональные блоки и их назначение

Архитектура ОМК MCS-51, разработанная фирмой Intel, стала де-факто стандартной для МК. В нашей стране МК данной архитектуры относятся к семейству МК-51. Все они имеют емкость внутренней памяти данных в 128 байт и максимальную внешнюю тактовую частоту 12 МГц.

М К

содержит:

К

содержит:

арифметико-логический блок (АЛБ), включающий:

8-разрядное АЛУ, битовое АЛУ;

регистр-аккумулятор A и дополнительный регистр-аккумулятор B, использующиеся при выполнении операций умножения и деления;

битовый аккумулятор, находящийся в разряде C слова состояния процессора PSW;

ВП программ емкостью 4 Кбайт, где могут храниться константы;

ВП данных емкостью 128 байт, используемую для организации банков РОН, стека и хранения пользовательских данных; часть этой памяти имеет побитовый доступ;

32 двунаправленных интерфейсных линии, индивидуально настраиваемых на ввод или вывод информации и организованных в виде 4 × 8-разрядных портов P0-P3;

два 16-разрядных многорежимных таймера/счетчика TC0 и TC1, используемых для организации временных задержек, внешних событий и тактирования последовательного порта;

двунаправленный дуплексный асинхронный последовательный порт;

двухуровневую приоритетную маскируемую систему прерываний от трех внутренних источников (ТС0, ТС1 и последовательного порта) и двух внешних, поступающих по входам INT0 и INT1;

устройство управления (УУ);

встроенный тактовый генератор (ТГ), тактирование которого проводится внешним генератором с частотой fBQ; частота машинного цикла составляет fBQ / 12, время выполнения команд. МК составляет 1-4 периода машинного цикла.

*Назначение разрядов регистра слова состояния PSW процессора (позиция (мнемоника) —функция):

7 (С) — перенос в арифметических операциях и битовый аккумулятор в логических операциях. 6 (АС) — флаг вспомогательного переноса. Устанавливается и сбрасывается аппаратно при выполнении сложения и вычитания и сигнализирует о переносе или займе. 5 (FO) — флаг, специфицируемый пользователем. 4, 3 (RS1, RS0) — номер рабочего банка регистров. 2 (OV) — переполнение в арифметических операциях. 1 — не используется. 0 (Р) — признак четности числа единиц в аккумуляторе.

2.2. Организация памяти программ и памяти данных

Особенность ОМК — «гарвардская архитектура», при которой память программ и память данных физически и логически отделены друг от друга.

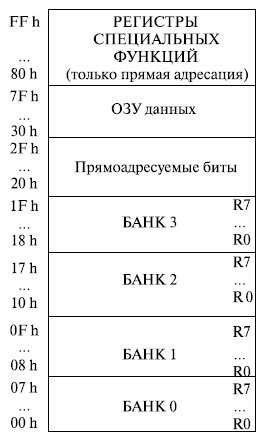

1. Память данных:

Память данных, расположенная на кристалле (внутренняя память данных), имеет емкость 128 байт с адресами 00h-7Fh. Она может быть расширена до 64 Кбайт за счет подключения блоков внешней памяти данных.

00-1Fh: 4 банка по 8 РОН в каждом. Определение банка осуществляется установкой битов RS0 и RS1 в PSW. Наличие нескольких банков сокращает длину команд за счет уменьшения длины поля номера регистра и уменьшает время, необходимое для сохранения и восстановления регистров при работе с подпрограммами и обработчиками прерываний.

20h-2Fh: область ячеек, к которым возможен побитовый доступ.

30h-7Fh: обычная ОП. Во внутреннем ОЗУ данных размещается также область стека. Ее положение определяется значением указателя стека SP.

80h-FFh: указание регистров специальных функций МП (только прямая адресация). Данная область содержит регистры-защелки портов ввода-вывода, регистры Т/С, регистры управления и т. п.

Все ячейки внутреннего ОЗУ данных могут адресоваться с использованием прямой и косвенной адресации.

К внешней памяти данных можно обращаться только на запись или чтение с помощью специальных команд, которые осуществляют обмен информацией между ВП данных и аккумулятором МК и не влияют на ВП данных МК. Таким образом, в системе могут одновременно присутствовать внутренняя память данных с адресами 00h-FFh и внешняя память данных с адресами 0000h-FFFFh.