- •Історія розвитку мп техніки. Закон мура

- •Основні технології виготовлення мпп

- •Сучасний стан та тенденції розвитку мікропроцесорних пристроїв. Наслідки закону Мура.

- •Класифікація мпп та систем

- •Класифікація мікропроцесорів

- •Закон Амдала та його наслідки

- •Структура типового мп

- •Cisk та risc архітектури

- •Гарвардська та принстонська архітектури

- •Поняття та класифікація арифметико – логічних пристроїв

- •13. Регістри

- •Пристрої синхронізації

- •Ієрархія пам’яті мпп

- •Типова мікросхема пам’яті

- •Структури пам’яті

- •Постійна пам'ять

- •Флеш – пам'ять

- •Основна характеристика та режими роботи паралельних портів на прикладі aTmega128

- •Інтерфейс rs-232

- •Структурна схема uart

- •Основні регістри uart

- •Програмування передавання даних за допомогою інтерфейсу uart

- •31. Загальний огляд роботи інтерфейсу spi.

- •Структурна схема spi

- •Основні регістри spi

- •34. Схеми з’єднання пристроїв з spi інтерфейсом

- •35. Програмування spi

- •36.Переваги та недоліки інтерфейсу spi

- •37. Загальний опис протоколу і2с

- •38. Арбітраж

- •39.Структура інтерфейсу і2с

- •40. Регістри і2с

- •41.Модель обміну даних в інтерфейсі usb

- •42. Загальна характеристика роботи usb host-контролера, usb hub, usb device

- •43. Характеристика мови опису апаратури vhdl. Поняття сутності, архітектури, компонента

- •44. Характеристика мови опису апаратури vhdl. Реалізація виконання паралельних та послідовних операцій.

- •45.Характеристика мови опису апаратури vhdl. Поняття сигналу, порту, змінної. Види портів.

31. Загальний огляд роботи інтерфейсу spi.

Інтерфейс розробила компанія Motorola.

Slave – годинники, контролери.

Master генерує за допомогою текстового генератора текст. За цей час одночасно зсуваються регістри як з боку Master, так і з боку Slave.

…

останній етап

SPI працює в 3 режимах:

Run

Wait – тактовий генератор вимикається з боку Master, будь-яке передавання призупиняється, але після повернення в Run може бути відновлено і завершено

Stop – режим зменшеного енергоживлення. Призупиняється передача даних. Якщо SPI сконфігурований як Slave, він завершує передавання і отримання байтів.

MOSI – Master input, slave out

VCC - живлення

SCK – лінія синхроімпульсів

RESET –

CND – заземлення

Структурна схема spi

XTAL

S M

M S

MSB LSB

Mosi(

PB2)

Mosi(

PB2)

SCK (PB1)

SS (PB0)

Логіка

тактування

Блок керування

Регістр

керування

SPI

Регістр стану SPI

Шина даних

Основні регістри spi

-0 – SPISR1 R/W

-1 – SPISR2 R/W

-2 – SPIBR – Регістр ботової швидкості R/W1

-3 – SPISR – Регістр стану R/W1

-4 – зарезервовано R2

-5 – Регістр даних R/W

-6 – зарезервовано

-7 – зарезервовано

34. Схеми з’єднання пристроїв з spi інтерфейсом

Схема з’єднання Master із Slave

Незалежне підключення пристроїв з SPI інтерфейсом

Каскадне

з’єднання

Каскадне

з’єднання

35. Програмування spi

В микроконтроллерах AT89Sxxxx реализована возможность изменения содержимого памяти программ при нахождении МК в целевой системе – ISP – in-system programming. Эта возможность обеспечивается наличием последовательного интерфейса SPI. Этот интерфейс, кроме целей программирования, в некоторых моделях может также обеспечивать обмен данными между несколькими микроконтроллерами. Скорость обмена – до 1,5 Мбит/с.

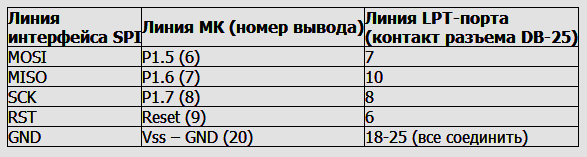

Согласно стандарту интерфейса SPI, в нем присутствуют такие сигналы (в скобках указана соответствующая физическая линия порта МК):

MOSI (P1.5) – master output slave input – информационный выход контроллера, инициирующего обмен (ведущего) – вход ведомого контроллера;

MISO (P1.6) – master input slave output – информационный вход контроллера, инициирующего обмен (ведущего) – выход ведомого контроллера;

SCK (P1.7) – serial clock – линия синхронизации; тактовые импульсы формирует ведущий контроллер;

SS (P1.4) – slave select – линия выбора ведомого устройства; ведомое устройство должно формировать на этом выходе “0”.

Настройка интерфейса SPI для обмена данными с другими микроконтроллерами производится путем установки битов специальных РСФ:

SPCR – SPI control register, SPSR – SPI status register и SPDR – SPI data register. Битовая структура этих регистров в данной статье не рассматривается.

Для целей физического программирования Flash-памяти интерфейс SPI используется совместно с сигналом Reset, а линия SS не задействована. При подаче высокого уровня на вход Reset контроллер переходит в режим сброса, одновременно являющийся режимом записи памяти программ.

Физическое программирование Flash-памяти может быть выполнено непосредственно с ПЭВМ. Для выдачи сигналов программирования можно использовать LPT-порт, а необходимый протокол (последовательность команд, адресов и данных для записи) реализуется специальным программным обеспечением. Таким образом, через линии параллельного LPT-порта реализуется побитовая передача данных.

Программирование выполняется через кабель, построенный по схеме:

Кабель рекомендуется выполнять таким образом, чтобы каждый сигнальный провод образовывал витую пару с проводником GND (можно использовать плоский многожильный кабель с индивидуальной экранировкой проводов). Длина кабеля не должна превышать 1 м.

SPCR=0xD0; (0xC0 – для slave)

SPSR=0×00;

Отправить байт:

SPDR=data;

Принять байт:

data=SPDR;