- •1. Общие положения

- •Характеристики универсальных микропроцессоров:

- •Организация внутренней памяти данных (озу) Преимущества разделения на банки:

- •Память программ

- •3. Аппаратные и программные средства микроконтроллера для обработки битовой информации

- •Сброс флагов запросов прерывания

- •5. Блок таймеров/счетчиков: назначение, структура, режимы работы, применение.

- •Режимы работы таймер/счетчик

- •6. Организация последовательного ввода/вывода в микроконтроллере.

- •7.Включение микроконтроллера в систему управления.

- •0, 1

- •3. Универсальные микропроцессоры

- •Основные функциональные регистры

- •Основные функциональные регистры -Сегментные регистры

- •Типы логического адресного пространства

- •Формирование линейного адреса

- •Формат селектора

- •Формат дескриптора

- •Обращение к глобальной таблице дескрипторов

- •Обращение к локальной таблице дескрипторов

- •Двухэтапное преобразование

- •Формат элемента ктс (таблицы страниц)

- •Структура tlb

- •Механизм замещения строк (lru)

- •Средства защиты должны предотвращать:

- •Обращение к более привилегированным программам через шлюз вызова

- •Структура дескриптора шлюза вызова

- •Для аппаратной поддержки многозадачности используется:

- •Содержимое tss:

- •Дополнительная часть tss:

- •Структура команды межсегментной передачи управления

- •Структура байта доступа в дескрипторе tss

- •Типы кэш памяти

- •Пример:

- •Порядок обработки прерываний

- •Рефлекторные действия процессора

- •Пример (для рефлекторного мк):

- •Типы прерываний

- •Определение адреса обработчика прерываний

- •Шлюзы ловушки и прерывания

- •Шлюз задачи

- •Регистр типов

- •Пример:

- •Время выполнения n-команд

- •Конфликты:

- •Структурные конфликты

- •Причины:

- •Пути решения для Запоминающих Устройств (зу):

- •Традиционные методы

- •Ограничения:

- •Ограничения:

- •Современные направления

- •Достоинства данного подхода:

- •Недостатки:

- •4. Структура и особенности функционирования современных микропроцессоров

3. Универсальные микропроцессоры

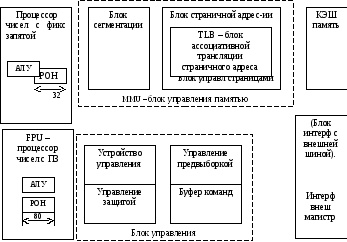

Структура универсального МП. Основные функциональные блоки и их назначение.

Блок интерфейса с внешней шиной позволяет:

- электрическое согласование внутренней магистрали с внешней магистралью;

- формировать необходимых сигналов и принимать необходимых данных из вне;

Буфер команд– буферный регистр, куда пишется несколько последующих команд.

Управление защитой– избегание стандартных ошибок, внутренняя защита (привилегии…).

МП использует:

32х разрядную шину управления (ШУ);

32х разрядную шину данных (ШД);

34х разрядную шину адреса (ША) (А31…..А02, B03, B02, B01, B00 - где: А – данные,B – какие байты в шине в текущий момент передачи активны)

Блок обработки с фиксированной точкой. Содержит:

- 32х разр АЛУ, - 8 на 32 разр РОН

Блок обработки с плавающей запятой (FPU). Содержит:

- АЛУ для обработки чесел с пл зап

- 8 на 80 разр регистр данных

- специальные регистры

Блок управления памятью (MMU).Поддерживает сегментно-станичн организац пам.

Память разбивается на сегменты переменн длины (от 1 до 2^32 байт), кот разбив на стр фикс длины (I486 - 4k). Для получ физич адреса, кот выдается на адресн линии внешн магистр, снач логич-го адреса(блок сегментации), преобразуется в лин, кот затем блоком управл стр-ми преобр-ся в физич.

Буфер ассоциативн –трансляц … адреса. Использ для сокращен врем преобр страничн адр

КЭШ память. Хранен наиболее часто использ инф (ком-ды, данные),(КЭШ совмещенн)

Микропроцессор. Может работать:

- в реальном режиме(однозадачность, фиксир длина сегмента, страниц нет)

- в защищенном режиме(многозадачность, переменная длина сегмента, разбиение на страницы, защита отдельных программ и данных др от др)

Регистровая структура 32-разрядного универсального МП.

Основные функциональные регистры:

Регистры общего назначения (РОН);

Указатель команд;

Регистры флагов;

Сегментные регистры;

Регистры FPU:

Регистры данных;

Регистры тегов;

Регистры состояний;

Регистры управлений;

Указатели команд и данных FPU;

Системные регистры:

Регистры управления;

Регистры системных адресов;

Регистры отладки и тестирования.

Группы 1,2– используются прикладными программистами

Группа 3– используется системными программистами

Г руппа

4– используется при отладке и

тестирование КЭШ памяти

руппа

4– используется при отладке и

тестирование КЭШ памяти

Основные функциональные регистры

Регистры общего назначения (РОН)

Специальные биты указывают, какой разрядности используется регистр (EAX-32 разрядный,AX-16 разрядный,AL(AH)-8-и разрядный).

Используются для хранения промежуточных результатов вычисления, а также как адресные регистры при различных режимах адресации.

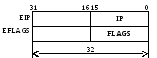

Указатель команд

E IP– указатель команд. Содержит смещение

относит-но начала сегмента

IP– указатель команд. Содержит смещение

относит-но начала сегмента

Регистр флагов:

Содержит признаки результата выполнения команды;

обработкой маскируемых прерываний;

Управляет последовательностью выполняемых задач;

Управляет вводом/выводом

Другие задачи

Биты состояний регистров флагов

ZF– признак нулевого результата;

SF– знак результата;

OF– признак переполнения;

CF– признак переноса;

PF– признак чётности, дополняет до нечётного числа младший байт результата.

Биты управления (PL – уровень привилегий)

IOPL(2 бита) –уровень привилегий I/O. С каким уровнем привилегий прогр разрешено выполнять ввод/вывод (3-ий уровень – польз програ, 0 – максим приор). Вв/выв могут выполнять только сист прогр, пользов прогр не могут сами выполнI/O.

IF–флаг прерываний. Разрешает обработку маскируемых прерываний (EAв МК51)

TF–флаг трассировки. TF=1 после выполн кажд ком возникает прерыван. Использ отладч.

NT–вложенная задача– показывает, что задача была вызв из друг прогр, аналог подпрогр. Возврат из этой задачи должен провод-ся по мех-му перекл задач(полн меняется контекст зад).