ЛЕКЦИЯ №8

3. Интерфейсы передачи данных

Назначение и типы интерфейсов.

Однопроводный интерфейс.

Дифференциальный интерфейс.

ИС для интерфейсов.

Совместимость.

Интерфейсы тестирования и программирования. Интерфейс JTAG.

Литература:

Стешенко В.Б. EDA. Практика автоматизированного проектирования РЭУ. – М.: Изд. Нолидж., 2002 – 768 с.

Г. Угрюмов Цифровая схемотехника.– СПБ, БХВ, Петербург, 2001- 528с.

Юдин А. Интерфейсные микросхемы компании STMicroelectronics и особенности их применения // Компоненты и технологии. 2003. №2, №3. с. 84 – 87

Стешенко В.Б. ПЛИС фирмы «ALTERA»: элементная база, система проектирования и языки описания аппаратуры. – М.: Издательский дом «Додэка», 2002. – 576 с.

Назначение и типы интерфейсов

Интерфейсы предназначены для обмена данных между электронными устройствами.

Интерфейс состоит из аппаратных средств и протокола передачи данных.

Современные ПЛИС имеют встроенные аппаратные средства для реализации интерфейсов (низковольтный GTL, LVTS и т.д.). Необходимы средства сопряжения этих интерфейсов с традиционными (RS232, RS485 и др.).

При длине кабеля (электрического канала связи) больше нескольких десятков сантиметров стандартные логические уровни перестают удовлетворять.

Выбор интерфейса и соответственно протокола обмена данными определяется

длинной линии;

требуемой скоростью передачи данных;

расстоянием между источником и приемником данных;

заданными уровнями сигналов; совместимостью;

видом интерфейса – параллельный или последовательный.

По способу организации передачи данных интерфейсы бывают

однопроводные (single-ended),

дифференциальные (differential).

Физические параметры интерфейса:

VIH – входное напряжение высокого уровня;

VIL – входное напряжение низкого уровня;

VOH – выходное напряжение высокого уровня;

VOL –выходное напряжение низкого уровня.

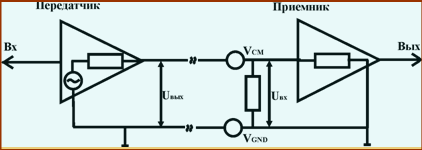

Однопроводной интерфейс (рис. 8.1)

Используется один сигнальный провод.

Логический уровень определяется относительно земли.

Для простых медленных допускается использование общей земли. В более совершенных интерфейсах каждый сигнальный провод имеет свою землю. Они объединяются в «витую пару».

Рис. 8.1.

Преимущество – простые и дешевые в реализации. Удобные для передачи данных на небольшие расстояния.

Примеры: параллельный интерфейс принтера (LPT), последовательный интерфейс (RS232).

Основной недостаток – низкая помехоустойчивость (из-за наводок на общий провод возможен сдвиг уровней сигналов). При длине несколько метров сказывается индуктивность и емкость проводов.

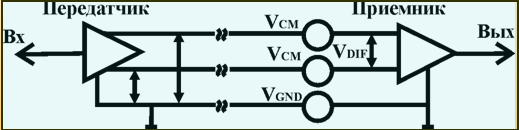

3. Дифференциальный интерфейс (рис. 8.2).

Для передачи данных используется пара проводов.

На приемном конце вычисляется разность между сигналами. Это в значительной мере подавляет синфазную помеху.

Рис. 8.2.

Обладает высокой помехоустойчивостью (например, RS-485 применяется в промышленных компьютерах).

Недостатки:

относительно высокая стоимость;

сложность выполнения парных согласованных каскадов передатчика и приемника.

Пример дифференциального интерфейса – RS–485.

RS-485 спроектирован как балансная система. Это означает, что, помимо земляного, имеется два провода, которые используются для передачи сигнала.

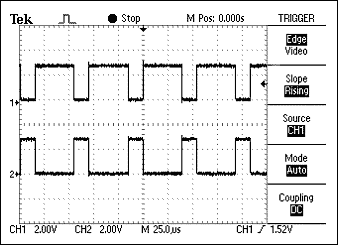

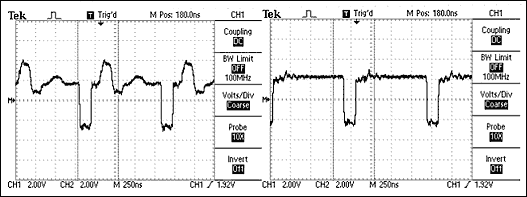

Система называется балансной, потому что сигнал на одном проводе является идеально точной противоположностью сигнала на втором проводе (рис. 8.3).

Рис. 8.3.

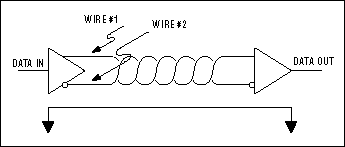

Электрические соединения в интерфейсе RS-485 лучше реализовать с помощью "витой пары".

Витая пара - это просто пара проводов, которые имеют равную длину и свиты вместе (рис. 8.4).

Рис. 8.4.

Использование передатчика, отвечающего требованиям спецификации RS-485, с кабелем на основе витой пары, уменьшает

излучаемые электромагнитные помехи;

индуцируемые электромагнитные помехи (наводка) (рис. 8.5).

Рис. 8.5.

Дифференциальный интерфейс LVDS.

LVDS (Low Voltage Differential Signaling) – это интерфейс для высокоскоростной передачи на короткие расстояния с уровнем синфазного напряжения 1 В и с малыми уровнями дифференциальных сигналов, преобразованных по стандарту ANSI TIA/EIA 644.

Характеристики интерфейса LVDS:

Uл = 300 мВ;

Сопротивления нагрузки линий RT = 100 Ом;

Выходной ток передатчика Iвых = 2,47…4,54 мА;

Максимальная скорость передачи данных 655 Мбит/с.

Достоинство – преемственность по разводке с RS- 422 и RS485

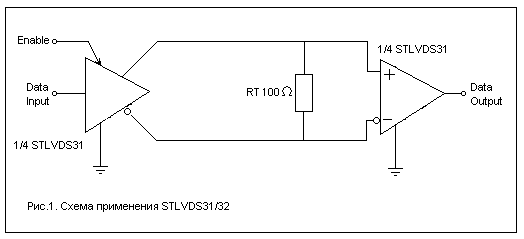

Примером реализации являются высокоскоростные интерфейсные схемы STLVDS31, STLVDS32 (рис. 8.6) и STLVDS104.

Рис. 8.6.

STLVDS31 и STLVDS32 содержат по четыре дифференциальных линейных передатчика и приемника для реализации стандарта LVDS. Они преобразуют 5-вольтовые логические уровни напряжений TTL (LVTTL) в дифференциальный стандарт (типа TIA/EIA 644) при питании схем от источника 3,3 В с обеспечением скорости передачи до 400 Мбит/с.

Интерфейс LVDS поддерживают многие современные ПЛИС:

APEX фирмы «Altera»;

Virtex фирмы «Xilinx».

Сопряжение и «горячее» подключение плат.

При разработке однопроводных интерфейсов возникают проблемы сопряжения модулей (плат) разработанных на новых ИС при подключении к объединительной или кросс–плате (backplane system), особенно если требуется «горячая замена» узлов (т.е. под напряжением питания и при работе устройства).

ТТЛ – уровни фактически являются стандартом для кросс–плат и внутрифирменных стандартов.

Подключаемые модули:

не должны выходить из строя при подключении к работающей системе;

не должны нарушать работу системы.

При «горячем» подключении модуля поведение системы будет предсказуемо при выполнении двух условий:

- на разъеме есть один или несколько контактов земли(GND), более длинных, чем другие;

- интерфейс состоит из микросхем на БТ с выходами с открытым коллектором;

микросхем БиКМОП с тристабильными выходами.

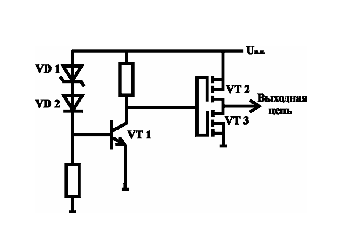

БиКМОП в составе содержит ИС, которые при подключении (включении напряжения питания) держат выход ИС в Z- состоянии (рис. 8.7).

При Uип < Uип уст

транзистор VT1– закрывается,

на VT3–низкий потенциал,

сигнал на выходе ИС отключается независимо от входного сигнала.

Рис. 8.7.

Проблема конфликтов на шине.

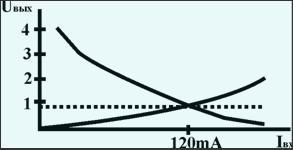

На шине могут появляться одновременно сигналы низкого и высокого уровней (рис. 8.8). В результате возникает ток величиной до 120 мА.

ИС с высоким уровнем напряжения работает в режиме короткого замыкания и сгорает.

Рис. 8.8.

Для избежания такого конфликта требуется дополнительная схема, которая во время включения держала бы выходы в Z–состоянии. Например, ИС TLC7705, используемая для формирования сигнала RESET при включении микросхем SN74ABT541.

Существуют ИС, которые содержат в себе схемы для защиты от шинных конфликтов.

Эти ИС выпускают в двух сериях:

ELT (Enhanced Transceiver Logic) – умощненная приемно-передающая логика, серия SN74ABTE.

BTL (Back Plane Transceiver Logic) - приемно-передающая логика для кросс-плат, серия SN74FB.

В ИС ELT для уменьшения помех при подключении к сигнальной шине имеется дополнительный вывод для подключения источника питания, заряжающего выходную емкость ИС – VCC BIAS.

Для понижения бросков тока и напряжения на шинах питания при подключении модуля используют:

медленное повышение напряжения на подключаемом модуле.

использование собственного источника питания в подключаемых модулях.

Медленное повышение напряжения на подключаемом модуле.

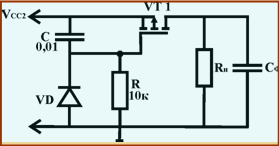

В цепь питания включен коммутатор на транзисторе VT1 (рис. 8.9).

Напряжение на затворе VT1 (р–канального) медленно возрастает с постоянной времени τ = RC.

Во включенном состоянии канал транзистора VT1 имеет маленькое сопротивление

VD – для быстрого разряда после выключения модуля.

Рис. 8.9.