- •Цифровая обработка сигналов в системах передачи информации

- •Рецензент:

- •Введение

- •1 Состав и содержание курсовой работы

- •1.1 Цель и задачи курсового проектирования

- •1.2 Задание на курсовую работу

- •1.3 Объем и содержание курсовой работы

- •1.4. Порядок выполнения

- •2 Правила оформления курсовой работы

- •2.1 Оформление пояснительной записки

- •2.2 Оформление схемы электрической функциональной

- •3 Особенности проектирования систем цифровой обработки сигналов

- •3.1 Анализ системных требований

- •3.2 Разработка структурной схемы

- •3.3 Выбор основных компонентов системы

- •3.3.1 Выбор процессора цос

- •3.3.2 Выбор host- процессора

- •3.3.3 Выбор ацп и цап

- •3.4 Разработка функциональной схемы

- •3.4.1 Организация синхронизации, сброса и начальной загрузки

- •3.4.2 Взаимодействие процессоров по host-интерфейсу

- •3.4.3 Подключение ацп и цап

- •3.4.4 Подключение внешней памяти

- •3.5 Разработка программного обеспечения

- •Список литературы

- •Цифровая обработка сигналов в системах передачи информации

- •424000 Йошкар-Ола, пл. Ленина, 3

- •424006 Йошкар-Ола, ул. Панфилова, 17

3.3.2 Выбор host- процессора

В качестве HOST- процессора обычно рекомендуется использовать 8 и 16-ти разрядные однокристальные микроконтроллеры (Intel MCS-51, Motorola MC68HC908GP32, Atmel AT90S1200, Microchip 16F84 и др.). Выбор HOST-процессора должен быть согласован с типов HOST-интерфейса процессора ЦОС и типом последовательного канала связи, заданным в ТЗ. Обычно фирма-производитель предлагает готовые решения по организации взаимодействия между процессорами ЦОС и рекомендованным HOST-процессором. В пояснительной записке должны быть проанализированы как минимум несколько альтернативных вариантов выбора HOST-процессора.

3.3.3 Выбор ацп и цап

Основными критериями при выборе АЦП и ЦАП являются разрядность и частот дискретизации. Дополнительным критерием может выступать требование к типу интерфейса - параллельному или последовательному способу подключения преобразователей к процессору ЦОС. Актуальными также остаются такие критерии выбора, как диапазон входных сигналов, количество входных каналов, напряжение питания, мощность потребления, доступность технической документации, Ваш опыт работы, техническая поддержка фирмы-производителя, стоимость и др.

Если в качестве требований к точности преобразования в ТЗ задано отношение мощности сигнала к мощности шума (с/ш), то разрядность преобразователя может быть определена из соотношения - С/Ш=(6,02N+1,76), дБ, где N- эффективная разрядность преобразователя.

Частота дискретизации (Fд) выбирается из требований, определяемых теоремой Котельникова – Fд ≥2*Fmax, где Fmax- максимальная частота в спектре входного сигнала. При выборе частоты дискретизации необходимо дополнительно учитывать область применения, в которой могут применятся стандартные частоты. Например, для обработки аудио-сигналов рекомендуется использовать – 44,1 кГц, 48кГц или 96 кГц.

Сигналы от источников информации не всегда согласуются по своим параметрам с параметрами используемого АЦП, вследствие чего на входе необходимо применять устройства предварительной обработки сигналов: усилители, повторители, аттенюаторы, различные преобразователи (ток-напряжение, сопротивление-напряжение), фильтры и т.д

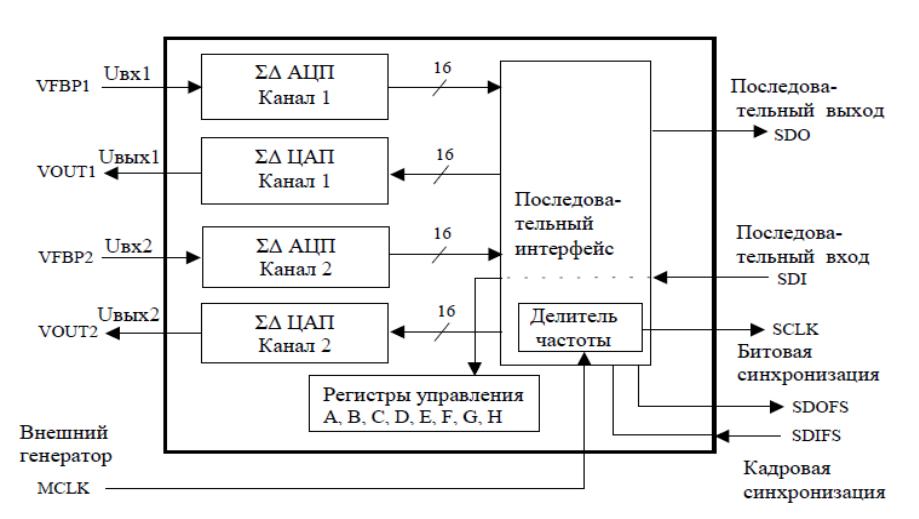

Так как большинство приложений цифровой обработки сигналов требует наличия одновременно АЦП и ЦАП, то широкое развитие получили кодеки с последовательным интерфейсом, обеспечивающие простое подключение к процессорам ЦОС. Например, кодек AD73322 с двумя 16-разрядными АЦП и двумя 16-разрядными ЦАП с возможностью работы с частотой дискретизации до 64 кГц.

Функциональная схема микросхемы AD73322 показана на рисунке 3.4.

Рисунок 3.4.

Кодек AD73322 разработан с использованием сигма-дельта преобразователей для универсального применения, включая обработку речи и цифровую телефонию. Каждый канал обеспечивает отношение сигнал/шум на уровне 77 дБ в пределах голосовой полосы частот.

Каналы АЦП и ЦАП имеют программируемые коэффициенты усиления по входу и выходу с диапазонами до 38 дБ и 21 дБ соответственно. Встроенный источник опорного напряжения допускает использование однополярного питающего напряжения величиной +2.7-5.5 В. Его потребляемая мощность при напряжении питания +3 В составляет 73 мВт.

Частота дискретизации кодека может быть запрограммирована на одно из четырех фиксированных значений: 64 кГц, 32 кГц, 16 кГц и 8 кГц при частоте опорного задающего генератора 16.384 МГц. Последовательный порт кодека позволяет легко организовать подключение к стандартным процессорам ЦОС, например, к процессорам семейства ADSP-21XX. Скорость передачи данных по последовательному порту может программироваться. Вариант подключения кодека к процессору семейства ADSP-218X показан на рисунке 3.5.

Рисунок 3.5.

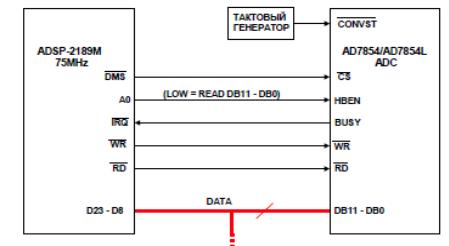

Альтернативным решением может быть выбор преобразователей с параллельным интерфейсом. Например, AD7854 – это 12-разрядный АЦП, работающий с частотой дискретизации 100 или 200 кГц. Схема подключения АЦП AD7854 к процессору ADSP2189 показана на рисунке 3.6.

Рисунок 3.6.

В пояснительной записке необходимо привести результаты сравнительного анализа не менее 3 преобразователей.