- •Содержание

- •Введение

- •1. Цель работы.

- •2. Теоретические основы.

- •3. Используемое оборудование.

- •4. Порядок работы со средой.

- •4.1. Начало работы со средой

- •4.3. Запуск заготовки приложения

- •4.4. Создание простейшей программы

- •4.4. Просмотр выполнения программы в отладчике

- •4.5. Описание данных в программе на ассемблере

- •5. Порядок выполнения работы.

- •Литература

Федеральное агентство по образованию

Г осударственное

образовательное учреждение

осударственное

образовательное учреждение

высшего профессионального образования

«МАТИ» – Российский государственный

технологический университет им. К.Э.Циолковского

Кафедра «Технология производства приборов и информационных систем управления летательных аппаратов»

Программирование на ассемблере MASM32. Изучение среды разработки RADasm и отладчика OllyDbg.

Методические указания к лабораторной работе

по дисциплине «Архитектура ЭВМ и систем»,

для специальности 230102.65 «Автоматизированные системы обработки информации и управления»

Автор: Пахомов М.М.

Москва 2012

Содержание

Введение

1. Цель работы

2. Теоретические основы

3. Используемое оборудование

4. Порядок работы с интегрированной средой разработки

5. Порядок выполнения работы

Литература

Введение

Настоящее методическое пособие является указанием для выполнения первой лабораторной работы по дисциплине «Архитектура ЭВМ и систем».

Данный курс лабораторных работ направлен на изучения основ программирования на 32-х разрядном ассемблере с использованием транслятора MASM32. Основная цель лабораторного курса - дать учащимся теоретические знания и практические навыки низкоуровневого программирования. Выполнив курс лабораторных работ, студент не только освоит основы программирования на ассемблере, но также получит более глубокое и детальное представление о работе компьютера.

1. Цель работы.

1. Научиться работать в интегрированной среде разработки программ на языке ассемблера, состоящей из специализированного пакета программирования MASM32, среды RADAsm и отладчика OllyDbg.

2. Изучить общую структуру программы на языке ассемблера.

3. Изучить программную модель процессора IA-32.

2. Теоретические основы.

Любой программе на ассемблере для ее исполнения выделяется определенный набор ресурсов компьютера. По большей части это ресурсы, предоставляемые процессором. Они необходимы программе для обработки и хранения в памяти команд и данных, а также получения информации о собственном текущем состоянии и состоянии процессора.

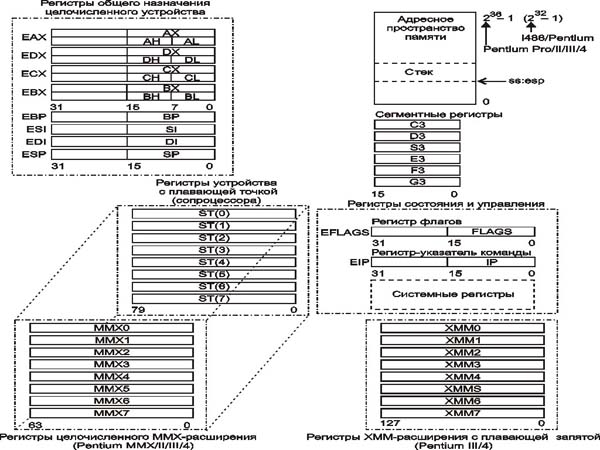

Программную модель процессора в архитектуре IA-32 составляет следующий набор ресурсов (рис. 2.1):

- пространство адресуемой памяти до 2-х в 32-й степени байт (4 Гбайт), для Pentium II и выше — до 2-х в 36 степени байт (64 Гбайт);

- регистры для хранения данных общего назначения;

- сегментные регистры;

- регистры состояния и управления;

- регистры устройства вычислений с плавающей запятой (сопроцессора);

- набор регистров целочисленного MMX-расширения, отображенных на регистры сопроцессора (впервые появились в архитектуре процессора Pentium MMX);

- набор регистров MMX-расширения с плавающей точкой (впервые появились в архитектуре процессора Pentium III);

- программный стек — специальная информационная структура, для работы с которой предусмотрены специальные машинные команды. Кроме того, к ресурсам, поддерживаемым архитектурой IA-32, необходимо отнести порты ввода-вывода, счетчики мониторинга производительности. Программные модели более ранних процессоров (i486, первые Pentium до Pentium MMX включительно) отличаются меньшим размером адресуемого пространства оперативной памяти (максимально 2 в 32-й степени адресов, так как разрядность их шины адреса составляет 32 бита) и отсутствием некоторых групп регистров. На рис. 2.1 для каждой группы регистров в

Рис. 2.1. Программная модель процессора семейства IA-32.

скобках показано, начиная с какой модели она появилась в программной модели процессоров INTEL. Если такого обозначения нет, то это означает, что данная группа регистров присутствовала в процессорах i386 и i486. Еще более ранние процессоры i8086/88, тоже полностью представлены на схеме, но составляют лишь небольшую ее часть. В программную модель этих процессоров входят 8- и 16-разрядные регистры общего назначения, сегментные регистры, регистры FLAGS, IP и адресное пространство памяти размером до 1 Мбайт.

Большинство регистров имеют определенное функциональное назначение. С точки зрения программиста, их можно разделить на две большие группы.

Первую группу образуют пользовательские регистры, к которым относятся:

- регистры общего назначения EAX/AX/AH/AL*, EBX/BX/BH/BL, EDX/DX/DH/DL, ECX/CX/CH/CL, EBP/BP, ESI/SI, EDI/DI, ESP/SP предназначены для хранения данных и адресов, программист может их использовать (с определенными ограничениями) для реализации своих алгоритмов;

* В обозначениях многих регистров программной модели присутствует наклонная разделительная черта. Это не разные регистры, а части одного большого 32-разрядного регистра. Наклонная черта означает, что эти регистры можно использовать в программе как отдельные объекты. Так сделано для обеспечения работоспособности программ, написанных для прежних 16-разрядных моделей процессоров фирмы Intel, начиная с i8086. Процессоры i486 и Pentium включают в себя в основном 32-разрядные регистры. Их количество, за исключением сегментных регистров, такое же как и у i8086, но емкость больше, что и отражено в обозначениях, — они имеют приставку E (Extended).

- сегментные регистры CS, DS, SS, ES, FS, GS служат для хранения значений, интерпретация которых зависит от режима работы процессора. В реальном режиме сегментные регистры содержат адрес параграфа начала сегмента в памяти. В защищенном режиме сегментные регистры хранят индекс входа в одну из системных таблиц дескрипторов — GDT или LDT;

- регистры сопроцессора ST(0), ST(1), ST(2), ST(3), ST(4), ST(5), ST(6), ST(7) предназначены для написания программ, оперирующих данными с плавающей запятой;

- целочисленные регистры целочисленного MMX-расширения MMX0, MMX1, MMX2, MMX3, MMX4, MMX5, MMX6, MMX7;

- регистры XMM-расширения с плавающей запятой XMM0, XMM1, XMM2, XMM3, XMM4, XMM5, XMM6, XMM7;

- регистры состояния и управления (регистр флагов EFLAGS/FLAGS и регистр указателя команды EIP/IP) содержат информацию о состоянии процессора, исполняемой программы и позволяют изменить это состояние.

Во вторую группу входят системные регистры, то есть предназначенные для обеспечения различных режимов работы, сервисных функций, а также регистры, специфичные для определенной модели процессора. К системным регистрам, поддерживаемым IA-32, относятся:

- управляющие регистры CR0–CR4 — определяют режим работы процессора и характеристики текущей исполняемой задачи;

- регистры управления памятью GDTR, IDTR, LDTR и TR используются в защищенном режиме работы процессора для локализации управляющих структур этого режима;

- отладочные регистры DR0–DR7 предназначены для контроля и управления различными аспектами отладки;

- регистры типов областей памяти MTRR используются для аппаратного управления кэшированием в целях назначения соответствующих свойств областям памяти;

- машинно-зависимые регистры MSR задействуются для управления процессором, контроля за его производительностью, получения информации об ошибках.

Регистры общего назначения привлекаются для хранения операндов команд целочисленного устройства, а также адресов и компонентов адреса.

На хранение операндов не накладываются особые ограничения, но в определенных условиях некоторые из регистров имеют жесткое функциональное назначение, закрепленное на уровне логики работы машинных команд. В этой связи среди всех регистров общего назначения особо следует выделить регистр ESP. В нем хранится указатель на вершину стека программы, и хранить здесь какие-либо операнды неразумно и небезопасно.

Перечислим регистры, относящиеся к группе регистров общего назначения и физически находящиеся в процессоре внутри арифметико-логического устройства ( регистры АЛУ):

- регистр-аккумулятор (accumulator register) EAX/AX/AH/AL применяется для хранения промежуточных данных, в некоторых командах его использование обязательно;

- базовый регистр (base register) EBX/BX/BH/BL задуман как место хранения базового адреса некоторого объекта в памяти;

- регистр-счетчик (count register) ECX/CX/CH/CL применяется в командах, производящих некоторые многократные действия;

- регистр данных (data register) EDX/DX/DH/DL, так же как и регистр EAX/AX/AH/AL, хранит промежуточные данные (в некоторых командах его явное использование обязательно, в других его участие подразумевается неявно).

Следующие два регистра предназначены для поддержки так называемых цепочечных операций, то есть операций, производящих последовательную обработку цепочек элементов, каждый из которых может иметь длину 32, 16 или 8 бит:

- регистр индекса источника (source index register) ESI/SI в цепочечных операциях содержит текущий адрес элемента в цепочке-источнике;

- регистр индекса приемника (destination index register) EDI/DI в цепочечных операциях содержит текущий адрес в цепочке-приемнике.

Для работы со стеком в системе команд процессора есть специальные команды, а в программной модели процессора для этого существуют специальные регистры:

- регистр указателя стека (stack pointer register) ESP/SP содержит указатель на вершину стека в текущем сегменте стека;

- регистр указателя базы кадра стека (base pointer register) EBP/BP предназначен для организации произвольного доступа к данным внутри стека.

Сегментные регистры необходимы для аппаратной поддержки сегментной организации программы. Это означает, что любая программа состоит как минимум из трех сегментов: кода, данных и стека. Логически машинные команды в архитектуре IA-32 построены так, что при выборке каждой команды для доступа к данным программы или к стеку неявно используется информация из вполне определенных сегментных регистров. В зависимости от режима работы процессора по их содержимому определяются адреса памяти, с которых начинаются соответствующие сегменты. В программной модели IA-32 имеется шесть сегментных регистров CS, SS, DS, ES, GS, FS, служащих для доступа к четырем типам сегментов.

Сегмент кода. Содержит команды программы. Для доступа к этому сегменту служит регистр сегмента кода (code segment register) CS. Он содержит значение, которое по-разному интерпретируется процессором, в зависимости от текущего режима работы. В реальном режиме — это адрес первого параграфа сегмента, в защищенном — индекс элемента в таблице дескрипторов (глобальной GDT или локальной LDT).

Сегмент данных. Хранит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр сегмента данных (data segment register) DS, в который помещен адрес сегмента данных текущей программы.

Сегмент стека. Представляет собой область памяти, называемую стеком. Работу со стеком процессор организует по следующему принципу: последний записанный в эту область элемент выбирается первым. Доступ к области стека выполняется через регистр сегмента стека (stack segment register) SS, содержащий адрес сегмента стека.

Дополнительный сегмент данных. Неявно алгоритмы выполнения большинства машинных команд предполагают, что обрабатываемые ими данные расположены в сегменте данных, адрес которого находится в регистре сегмента данных DS. Если программе недостаточно одного сегмента данных, то она имеет возможность одновременно задействовать еще три дополнительных сегмента данных, адреса которых должны содержаться в регистрах дополнительного сегмента данных (extension data segment registers) ES, GS, FS. Среди них следует особо выделить регистр ES. Он используется для обеспечения цепочечных команд процессора, адресуя собой операнд-источник.

В процессор Intel включены регистры состояния и управления (см. рис. 2.1), постоянно содержащие информацию о состоянии самого процессора и программы, команды которой он в данный момент обрабатывает:

- регистр указателя команды EIP/IP;

- регистр флагов EFLAGS/FLAGS.

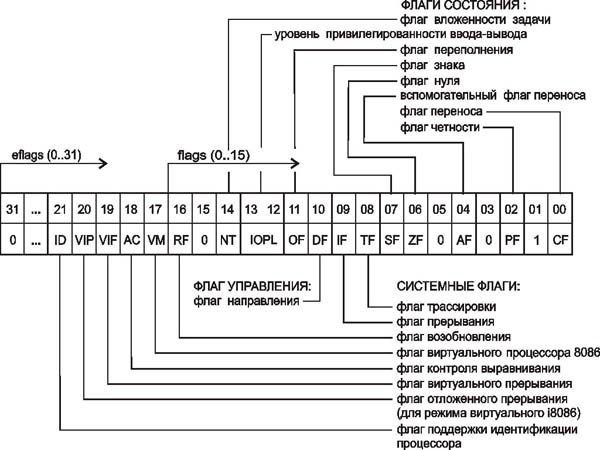

С помощью этих регистров можно также ограниченным образом управлять состоянием процессора. Регистр указателя команд (instruction pointer register) EIP/IP имеет разрядность 32/16 бит и содержит смещение следующей подлежащей выполнению команды относительно начала сегмента кода. Этот регистр непосредственно недоступен программисту, то есть его нельзя указывать в качестве операнда команд. Но к нему возможен косвенный доступ, так загрузка и изменение его содержимого производятся в результате работы различных команд управления программным потоком, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур. Возникновение прерываний также приводит к модификации содержимого регистра EIP/IP. Разрядность регистра флагов (FLAG REGISTER) EFLAGS/FLAGS равна 32/16 бит. Отдельные биты данного регистра имеют функциональное назначение и называются флагами. Младшая часть регистра EFLAGS/FLAGS полностью аналогична регистру FLAGS процессора i8086. На рис. 2.2 показано содержимое регистра EFLAGS.

Исходя из особенностей использования, флаги регистра EFLAGS/FLAGS делятся на три группы:

1. Флаги состояния — отражают особенности результата исполнения арифметических или логических операций и могут изменяться сознательно:

Флаг переноса (carry flag) CF — если равен 1, то арифметическая операция произвела перенос из старшего бита результата (или перенос инициирован командой сдвига) или в старший бит результата. Старшим является 7-й, 15-й или 31-й бит в зависимости от размерности операнда; если CF равен 0 — переноса не было. Этот флаг показывает условие переполнения для беззнаковой арифметики.

Флаг четности (parity flag) PF — если равен 1 — то 8 младших разрядов (этот флаг действителен только для 8 младших разрядов операнда любого размера) результата содержат четное число единиц; если равен 0 — среди 8 младших разрядов результата количество единиц нечетно.

Вспомогательный флаг переноса (auxiliary carry flag) AF — применяется только для команд, работающих с BCD-числами. Фиксирует

Рис.2.2. Содержимое регистра флагов.

факт заема из младшей тетрады результата: если равен 1 — в результате операции сложения был произведен перенос из разряда 3 в старший разряд или при вычитании был заем в разряд 3 младшей тетрады из значения в старшей тетраде; если равен 0 — переносов и заемов в третий разряд (из третьего разряда) младшей тетрады результата не было.

Флаг нуля (zero flag) ZF — когда равен 1 — результат нулевой; при равенстве 0 — результат ненулевой.

Флаг знака (sign flag) SF — отражает состояние старшего бита результата (биты 7, 15 или 31 для 8-, 16- или 32-разрядных операндов соответственно): если равен 1 — старший бит результата равен 1; если равен 0 — старший бит результата также 0.

Флаг переполнения (overflow flag) OF — используется для фиксации факта потери значащего бита при арифметических операциях со знаком: если равен 1 — в результате операции происходит перенос в старший знаковый бит результата или заем из старшего знакового бита результата (биты 7, 15 или 31 для 8-, 16- или 32-разрядных операндов соответственно); нулевое значение говорит об отсутствии переноса или заема.

2. Флаг направления DF (directory flag) — десятый бит регистра EFLAGS. Флаг DF используется цепочечными командами и определяет направление поэлементной обработки данных этими командами: DF = 0 — от начала цепочки к ее концу, то есть от младших адресов к старшим; DF = 1 — от конца цепочки к ее началу, то есть от старших адресов к младшим. Состояние флага DF можно изменить командами CLD (снять флаг DF) И STD (установить флаг DF).

3. Системные флаги и поле IOPL — управляют вводом-выводом, маскируемыми прерываниями, отладкой, переключением между задачами и режимом виртуального процессора 8086:

Флаг трассировки (trace flag) TF — предназначен для организации пошаговой работы процессора: если он равен 1 — процессор генерирует прерывание с номером 1 после выполнения каждой машинной команды (может использоваться при отладке программ); если равен 0 — обычная работа.

Флаг прерывания (interrupt enable flag) IF — предназначен для разрешения или запрещения (маскирования) аппаратных прерываний (прерываний по входу INTR): когда он равен 1 — аппаратные прерывания разрешены; при равенстве 0 — аппаратные прерывания запрещены.

Уровень привилегированности ввода-вывода (input/output privilege level) IOPL — используется в защищенном режиме работы процессора для контроля доступа к командам ввода-вывода в зависимости от назначенного задаче приоритета.

Флаг вложенности задачи (nested task) NT — используется в защищенном режиме работы процессора для запоминания того факта, что одна задача связана с другой по цепочке вызовов. Работа цепочки связанных задач организуется с помощью команд CALL, IRET, регистра задач TR и сегмента TSS.

Флаг возобновления (resume flag) RF — применяется при обработке прерываний от регистров отладки.

Флаг режима виртуального процессора 8086 (virtual 8086 mode) VM — признак текущего режима процессора: если он равен 1 — процессор функционирует в режиме виртуального процессора 8086; равенство 0 означает работу в реальном или защищенном режиме.

Флаг контроля выравнивания (alignment check) AC — предназначен для разрешения контроля выравнивания при обращениях к памяти. Используется совместно с битом AM в системном регистре CR0. Процессоры IA-32 (начиная с i80486) разрешают размещать команды и данные, начиная с любого адреса. Установка данных битов (при уровне привилегий CPL = 3), как правило, будет приводить к возникновению исключительной ситуации при попытках обращения к данным и командам по адресам, некратным 2 или 4.

Флаг виртуального прерывания (virtual interrupt flag) VIF (только Pentium) — при определенных условиях, одно из которых — работа процессора в V-режиме, является аналогом флага IF. Флаг VIF используется совместно с флагом VIP (при CR4.VME = 1).

Флаг отложенного виртуального прерывания (virtual interrupt pending flag) VIP (только Pentium) — устанавливается в 1 для индикации отложенного прерывания. Применяется при работе в режиме виртуального процессора i8086 совместно с флагом VIF (при CR4.VME = 1). Может быть установлен только программно, процессор лишь читает его.

Флаг идентификации (identification flag) ID — используется для того, чтобы показать факт поддержки процессором инструкции CPUID. Если программа может установить или сбросить этот флаг, то это означает, что данная модель процессора поддерживает инструкцию CPUID.

Системные регистры выполняют специфические функции в системе. Использование их жестко регламентировано. Именно они обеспечивают работу защищенного режима. Их также можно рассматривать как часть архитектуры процессора, которая намеренно оставлена видимой для того, чтобы позволить квалифицированному системному программисту выполнить самые низкоуровневые операции.