- •Компьютерная и микропроцессорная техника в электротехнологии

- •Введение

- •Лабораторная работа № 1. Использование специальных возможностей excel

- •Лабораторная работа № 2. Средства автоматизации научно-исследовательских работ. Среда mathcad. Часть I.

- •Литература

- •Лабораторная работа № 3. Средства автоматизации научно-исследовательских работ. Среда mathcad. Часть II.

- •Литература

- •Лабораторная работа №4. Matlab в задачах вычислительной математики

- •Лабораторная работа №5. Введение в Simulink

- •Графопостроитель ху Graph

- •Блок алгебраического контура Algebraic Constraint

- •Разработка структурной модели и ее исследование.

- •Задание:

- •3.2. Задание:

- •Выводы по работе.

- •Лабораторная работа №6. Моделирование логических устройств в среде matlab/Simulink.

- •Лабораторная работа №7. Исследование работы триггеров в среде Simulink. Регистры и счетчики. Связь логических и структурных схем в Simulink.

- •Лабораторная работа № 8. Изучение архитектуры микропроцессорной системы "микротренажер мт-1804".

- •Лабораторная работа №9. Изучение архитектуры микропроцессорной системы "электроника-580".

- •Литература

- •Дополнительная литература

- •Лабораторная работа №10. Программирование микропроцессорной системы "электроника-580.

- •Литература

- •Дополнительная литература

- •Требования к оформлению отчетов по лабораторным работам

- •Содержание

Выводы по работе.

Из анализа переходных процессов в исследуемой системе видно, что на этапе разогрева печи и на каждом из участков регулирования (в режиме установившихся автоколебаний) система является линейной и разомкнутой.

При отработке такой системой ступенчатого воздействия, соответствующего двукратному превышению номинальной мощности над средней, интервалы включенного и выключенного состояния регулирующего релейного элемента оказываются равными, а статическая ошибка, следовательно, нулевой.

При изменении уровня задающего воздействия или же введении в систему возмущения (изменение условий отдачи тепла от печи) вышеобозначенные интервалы становятся не равными друг другу, а статическая ошибка системы отличной от нуля. При этом в подобных системах величина статической ошибки может быть как положительной, так и отрицательной.

Увеличение ширины петли гистерезиса релейного элемента ведет к уменьшению частоты коммутаций.

При учете инерционности датчика температуры ширина зоны нечувствительности двухпозиционного регулятора температуры становится больше ширины петли гистерезиса релейного элемента. С ростом инерционности датчика зона нечувствительности регулятора увеличивается. Очевидно, что при этом частота коммутаций будет уменьшаться.

При увеличении заданного значения температуры ширина зоны нечувствительности регулятора остается неизменной, а частота коммутаций в функции величины заданного значения температуры представляет собой четную функцию относительно заданного значения температуры, соответствующего двукратному превышению номинальной мощности над её средним значением.

Лабораторная работа №6. Моделирование логических устройств в среде matlab/Simulink.

1. Моделирование работы простейших логических элементов («И», «ИЛИ», «НЕ»).

1.1. Составление логической схемы в среде Simulink.

После запуска MATLAB в командном окне Command Window наберите и выполните команду >> simulink для запуска приложения Simulink или воспользуйтесь для этого меню MATLAB. После открытия окна Simulink Library Browser выполните команду File > New > Model для открытия окна новой модели (рис. 6.1).

После открытия окна модели соберите схему, приведенную на рис. 6.2, с использованием подбиблиотек Logic and Bit Operations (блок Logical Operator), Sources (блок Constant), Sinks (блоки Display, Scope) [1].

Рис. 6.1. Командное окно MATLAB, окно библиотеки стандартных блоков, окно модели

Рис. 6.2. Схема с элементом «И»

1.2. Настройка параметров блоков схемы.

Следует отметить, что в настройках блока Logical Operator есть возможность изменять тип логического элемента (AND («И»), OR («ИЛИ»), NAND («НЕ-И», NOR («НЕ-ИЛИ»), XOR («исключающее ИЛИ»), NOT («НЕ»)), а также число его входов [1]. Окно с настройками блока приведено на рис. 6.3.

Рис. 6.3. Окно с настройками блока Logical Operator

Также следует помнить, что, к примеру, блоки NAND и NOR можно заменить последовательным соединением простейших логических элементов «И» (AND) с «НЕ» (NOT) и «ИЛИ» (OR) с «НЕ» (NOT) соответственно.

1.3. Проверка работы логического элемента. Составление таблицы истинности.

Для запуска моделирования необходимо нажать кнопку Start simulation в меню сверху. Результаты моделирования заносите в табл. 4.1 для каждого из простейших логических элементов (x,y – исходные операнды, f – результат логической операции).

Табл. 6.1. Результаты моделирования работы логического элемента

-

x

y

f

0

0

0

1

1

0

1

1

2. Моделирование работы логического элемента «исключающее ИЛИ».

Моделирование работы логического элемента «исключающее ИЛИ» проводите по приведенному ниже алгоритму.

2.1. Вывод логического выражения для операции «исключающее ИЛИ» по таблице истинности.

2.2. Построение логической схемы в среде Simulink.

Рис. 6.4. Логическая схема для операции «исключающее ИЛИ»

2.3. Проверка работы схемы.

Заполните табл. 6.1 для операции «исключающее ИЛИ».

2.4. Сравнение результатов, полученных на собранной схеме рис. 6.4, с результатами, полученными с использованием стандартного блока Simulink «исключающее ИЛИ» (блок Logical Operator, в настройках выбрать XOR).

2.5. Понятие подсистемы и маски, маскирование подсистем.

Для схемы рис. 6.4 создайте подсистему. Для этого выделите все блоки и связи между ними, кроме блоков Constant, Constant1, Display, затем нажмите правой кнопкой мыши и в появившемся контекстном меню выберите Create Subsystem (Создать подсистему). Схема по рис. 6.4 преобразуется в схему на рис. 6.5. Доступ к блокам и связям между ними, входящим в состав подсистемы, осуществляется двойным нажатием левой кнопкой мыши на значок подсистемы Subsystem (рис. 6.5).

Использование подсистем в Simulink существенно упрощает работу со сложными моделями. О масках и маскировании подсистем смотрите в [1].

Рис. 6.5. Логическая схема для операции «исключающее ИЛИ» с использованием подсистемы

3. Построение одноразрядного арифметического сумматора.

Моделирование работы одноразрядного арифметического сумматора проводите по приведенному ниже алгоритму.

3.1. Получение логического выражение для i-го разряда результата операции и переноса из i-го разряда в i+1-й разряд по таблице истинности, их упрощение. Составление логической схемы в среде Simulink (рис. 6.6).

Рис. 6.6. Логическая схема одноразрядного арифметического сумматора

3.2. Проверка работы схемы. Составление таблицы истинности (табл. 6.1).

3.3. Создание подсистемы «Одноразрядный сумматор».

4. Построение четырехразрядного сумматора с использованием созданной подсистемы «Одноразрядный сумматор».

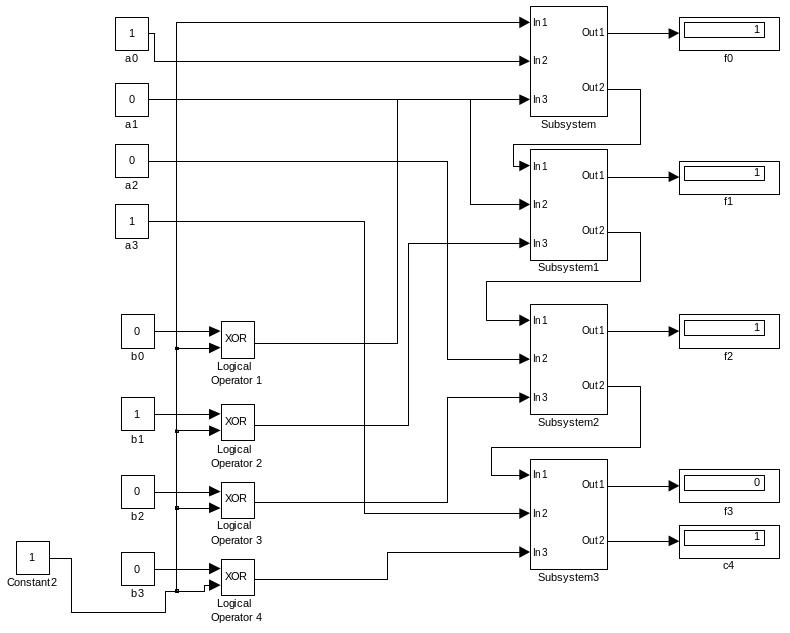

Рис. 6.7. Схема четырехразрядного арифметического сумматора в Simulink

5. Построение четырехразрядного сумматора-вычитателя.

Используя логическую схему на рис. 6.7, разработайте схему с задаваемой логикой – логическую схему сумматора-вычитателя (рис. 6.8).

Рис. 6.8. Логическая схема сумматора-вычитателя

В схеме рис. 6.8 элементы «исключающее ИЛИ» (блоки Logical Operator 1 – 4) играют роль управляемых инверторов. Значение управляющего сигнала в схеме задается блоком Constant2 (если значение равно 0, схема работает как сумматор (f=a+b), если 1 – как вычитатель (f=a-b)).

Литература

Черных И.В. SIMULINK: среда создания инженерных приложений / Под общ. ред. к.т.н. В.Г. Потемкина. – М.: ДИАЛОГ-МИФИ, 2003.