- •Электроника

- •Содержание

- •1.1 Основы алгебры логики………………………………………………..5

- •1 Цифровые интегральные микросхемы

- •1.1 Основы алгебры логики

- •1.1.1 Основные определения

- •1.1.2 Некоторые логические функции и реализующие их логические элементы

- •1.1.3 Основные законы и соотношения алгебры логики

- •Сочетательный закон

- •Распределительный закон

- •1.2 Параметры цифровых интегральных микросхем

- •1.2.1 Параметры цифровых интегральных микросхем (цимс), имеющие размерность напряжение.

- •1.2.2 Параметры, соответствующие размерности тока.

- •1.2.3 Параметры, имеющие размерность мощности.

- •1.3.2 Характеристики дтл.

- •1.4 Транзисторно – транзисторная логика.

- •1.5 Ттл со сложным инвертором.

- •1.6 Ттл с открытым коллекторным выходом.

- •1.7 Ттл с тремя состояниями на выходе

- •1.8 Транзисторно-транзисторная логика Шоттки

- •1.9 Комплиментарная мдп логика

- •2 Операционные усилители

- •2.1 Параметры и характеристики оу

- •2.3 Дифференциальный усилитель

- •2.4 Составной транзистор

- •2.5 Источник тока

- •2.6 Схема сдвига уровня

- •2.7 Эмиттерный повторитель

- •2.8 Инвертирующий усилитель на оу.

- •2.9 Неинвертирующий усилитель

- •3 Технологические основы производства полупроводниковых интегральных микросхем

- •3.1 Подготовительные операции

- •3. 2 Эпитаксия

- •3.3 Термическое окисление

- •3.4 Литография

- •3.5 Легирование

- •3.5.2 Ионная имплантация.

- •3.6.1 Термическое (вакуумное) напыление.

- •3.6.2 Катодное напыление.

- •3.6.3 Ионно-плазменное напыление.

- •4 Полупроводниковые

- •4.1 Методы изоляции элементов в ппимс

- •4.1.1 Изоляция элементов обратно смещенными pn-переходами.

- •4.1.2 Резистивная изоляция.

- •4.1.3 Диэлектрическая изоляция

- •4.2 Планарно-эпитаксиальный биполярный транзистор

- •4.2.1 Этапы изготовления

- •4.2.2 Распределение примесей.

- •4.2.3 Эквивалентная схема.

- •4.3 Планарно-эпитаксиальный биполярный транзистор

- •4.4 Разновидности биполярных транзисторов

- •4.4.1 Многоэмиттерный транзистор.

- •4.4.2 Транзистор с барьером Шоттки.

- •4.4.3 Транзисторы р-n-р

- •4.5 Интегральные диоды

- •4.6 Полевые транзисторы

- •4.6.1 Полевые транзисторы с управляющим p-n переходом

- •4.6.3 Мноп-транзистор.

- •4.7 Полупроводниковые резисторы

- •4.7.1 Диффузионные резисторы.

- •4.7.2 Ионно-легированные резисторы.

- •4.8 Полупроводниковые конденсаторы

- •5.1 Подложки гимс.

- •5.2 Резисторы.

- •5.3 Конденсаторы

- •5.4 Катушки индуктивности

1.9 Комплиментарная мдп логика

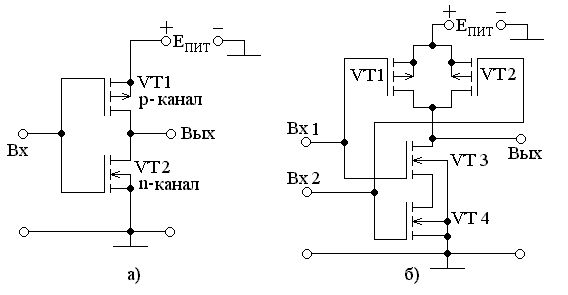

Комплиментарная МДП (КМДП) логика включает в себя парыp- иn-канальных полевых транзисторов с индуцированным каналом. Простейшая схема, выполняющая операцию НЕ представлена на рисунке 1.18а.

Рисунок 1.18

Принцип её работы поясним с помощью таблицы 1.10.

Таблица 1.10

|

Вх |

UВХ, В |

VT1 |

VT2 |

IС |

UВЫХ, В |

Вых |

|

0 |

0 |

Откр |

Закр |

0 |

10 |

1 |

|

1 |

10 |

Закр |

Откр |

0 |

0 |

0 |

Предположим, что напряжение питания равно ЕПИТ=10 В. Как будет показано ниже напряжениеU0=0 В, аU1=10 В. Пороговое напряжение, подаваемое на затвор, у таких транзисторов составляет примерноUЗИ ПОРОГ 4 В. Тогда при подаче на вход напряжения логического0(первая строчка таблицы) транзисторVT2 будет закрыт, а транзисторVT1 будет открыт. Так как напряжение между его затвором и истоком, который соединен с подложкой, равноUЗИ=-10 В, а пороговое напряжение для р-канального транзистора составляетUЗИ ПОРОГ -4 В. Поскольку транзисторVT2 закрыт, ток стокаIС=0. Напряжение на выходе составитUВЫХ= 10 В и, следовательно, это соответствует логической1.

При подаче на вход логической 1U1=10 В (вторая строчка таблицы) транзисторVT1 будет закрыт, поскольку напряжение между его затвором и истоком составляетUЗИ=0 В, а транзисторVT2 будет открыт. Так как транзисторVT1 закрыт, ток стока так же будет равенIС=0. Напряжение на выходе составитUВЫХ= 0 В и, следовательно, это соответствует логическому0. Таким образом, в статическом состоянии ток через схему отсутствует за исключением тока утечки, который составляет единицы мкА.

Рассмотрим схему, приведенную на рисунке 1.18б. Принцип её работы также поясним с помощью таблицы 1.11.

Таблица 1.11

|

Вх 1 |

Вх 2 |

UВХ 1, В |

UВХ 2, В |

VT1 |

VT2 |

VT3 |

VT4 |

I |

UВЫХ, В |

Вых |

|

0 |

0 |

0 |

0 |

Откр |

Откр |

Закр |

Закр |

0 |

10 |

1 |

|

1 |

0 |

10 |

0 |

Закр |

Откр |

Откр |

Закр |

0 |

10 |

1 |

|

0 |

1 |

0 |

10 |

Откр |

Закр |

Закр |

Откр |

0 |

10 |

1 |

|

1 |

1 |

10 |

10 |

Закр |

Закр |

Откр |

Откр |

0 |

0 |

0 |

При подаче на оба входа логического 0, как было рассмотрено выше транзисторыVT1 иVT2 открыты, а транзисторыVT3 иVT4 закрыты. На выходе будет высокий потенциал и ток через схему отсутствует (первая строчка таблицы 1.11).

При подаче на вход хотя бы одной логической 1один из транзисторовVT3 илиVT4 открывается, а один из транзисторовVT1 илиVT2 закрывается. Поскольку один из транзисторов закрытVT3 илиVT4, то ток через схему отсутствует, а на выходе будет высокий потенциал, т.е. логическая1(вторая и третья строка таблицы).

При подаче на оба входа логических 1оба транзистораVT3 иVT4 открыты, а транзисторыVT1 иVT2 закрыты. На выходе будет логический0и ток через транзисторы по-прежнему отсутствует (четвертая строчка таблицы). Таким образом, данная схема выполняет операцию И-НЕ. В статическом режиме она не потребляет тока.

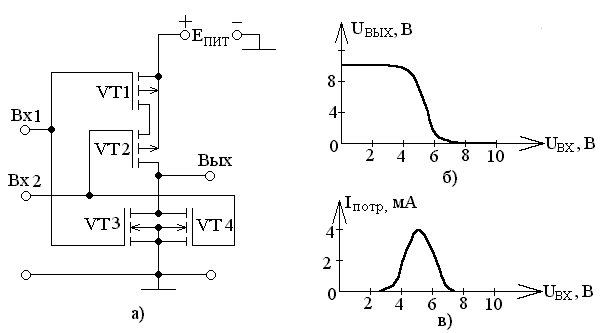

Схема ИЛИ-НЕ представлена на рисунке 1.19а, а её принцип работы поясним с помощью таблицы 1.12.

Таблица 1.12

|

Вх 1 |

Вх 2 |

UВХ 1, В |

UВХ 2, В |

VT1 |

VT2 |

VT3 |

VT4 |

I |

UВЫХ, В |

Вых |

|

0 |

0 |

0 |

0 |

Откр |

Откр |

Закр |

Закр |

0 |

10 |

1 |

|

1 |

0 |

10 |

0 |

Закр |

Откр |

Откр |

Закр |

0 |

0 |

0 |

|

0 |

1 |

0 |

10 |

Откр |

Закр |

Закр |

Откр |

0 |

0 |

0 |

|

1 |

1 |

10 |

10 |

Закр |

Закр |

Откр |

Откр |

0 |

0 |

0 |

В этом случае, в отличие от предыдущего, при подаче на один из входов логической 1(вторая и третья строчки таблицы) на выходе будет логический0, так как один из транзисторовVT1 иVT2 закрыт, а один из транзисторовVT3 илиVT4 открыт, т.е. на выходе будет нулевой потенциал.

Рисунок 1.19

Характеристики КМДП

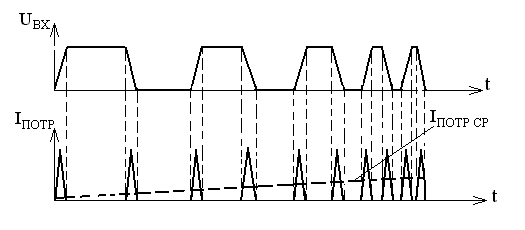

Характеристика прямой передачи приведена на рисунке 1.19б. При подаче низкого потенциала на вход, как было показано выше, на выходе будет высокий потенциал (логическая 1). Увеличивая напряжения на входе (при достижении порогового напряжения) открываются транзисторыVT3 иVT4 и начинают закрываться транзисторыVT1 иVT2, напряжение на выходе падает до нуля. Аналогично можно и объяснить характеристику тока потребления от входного напряжения (рисунок 1.19в), т.е. при напряжении от 3 до 7 вольт все транзисторыприоткрытыи в этом случае через схему протекает ток. Это приводит к тому, что при увеличении частоты переключения средний ток, потребляемый схемой, увеличивается (рисунок 1.20) и на высоких частотах он может сравняться с током потребления ТТЛ и ТТЛШ.

Рисунок 1.20

Ниже приведены параметры некоторых серий микросхем КМДП. Средний ток потребления от источника питания IПОТР СРприведен в статическом режиме. Из таблицы видно, что с совершенствованием технологии растут энергетические показатели.

Таблица 1.13

|

|

Серия | |||

|

Параметры |

561 |

564 |

1564 |

1554 |

|

ЕПИТ, В |

10 |

10 |

5 |

5 |

|

IПОТР СР, мкА |

4 |

1,5 |

1,25 |

1 |

|

tЗД Р СР, нс |

110 |

110 |

18 |

8 |

|

WДЖ, 10-12 |

4,4 |

1,65 |

0,1125 |

0,04 |