- •Электроника

- •Содержание

- •1.1 Основы алгебры логики………………………………………………..5

- •1 Цифровые интегральные микросхемы

- •1.1 Основы алгебры логики

- •1.1.1 Основные определения

- •1.1.2 Некоторые логические функции и реализующие их логические элементы

- •1.1.3 Основные законы и соотношения алгебры логики

- •Сочетательный закон

- •Распределительный закон

- •1.2 Параметры цифровых интегральных микросхем

- •1.2.1 Параметры цифровых интегральных микросхем (цимс), имеющие размерность напряжение.

- •1.2.2 Параметры, соответствующие размерности тока.

- •1.2.3 Параметры, имеющие размерность мощности.

- •1.3.2 Характеристики дтл.

- •1.4 Транзисторно – транзисторная логика.

- •1.5 Ттл со сложным инвертором.

- •1.6 Ттл с открытым коллекторным выходом.

- •1.7 Ттл с тремя состояниями на выходе

- •1.8 Транзисторно-транзисторная логика Шоттки

- •1.9 Комплиментарная мдп логика

- •2 Операционные усилители

- •2.1 Параметры и характеристики оу

- •2.3 Дифференциальный усилитель

- •2.4 Составной транзистор

- •2.5 Источник тока

- •2.6 Схема сдвига уровня

- •2.7 Эмиттерный повторитель

- •2.8 Инвертирующий усилитель на оу.

- •2.9 Неинвертирующий усилитель

- •3 Технологические основы производства полупроводниковых интегральных микросхем

- •3.1 Подготовительные операции

- •3. 2 Эпитаксия

- •3.3 Термическое окисление

- •3.4 Литография

- •3.5 Легирование

- •3.5.2 Ионная имплантация.

- •3.6.1 Термическое (вакуумное) напыление.

- •3.6.2 Катодное напыление.

- •3.6.3 Ионно-плазменное напыление.

- •4 Полупроводниковые

- •4.1 Методы изоляции элементов в ппимс

- •4.1.1 Изоляция элементов обратно смещенными pn-переходами.

- •4.1.2 Резистивная изоляция.

- •4.1.3 Диэлектрическая изоляция

- •4.2 Планарно-эпитаксиальный биполярный транзистор

- •4.2.1 Этапы изготовления

- •4.2.2 Распределение примесей.

- •4.2.3 Эквивалентная схема.

- •4.3 Планарно-эпитаксиальный биполярный транзистор

- •4.4 Разновидности биполярных транзисторов

- •4.4.1 Многоэмиттерный транзистор.

- •4.4.2 Транзистор с барьером Шоттки.

- •4.4.3 Транзисторы р-n-р

- •4.5 Интегральные диоды

- •4.6 Полевые транзисторы

- •4.6.1 Полевые транзисторы с управляющим p-n переходом

- •4.6.3 Мноп-транзистор.

- •4.7 Полупроводниковые резисторы

- •4.7.1 Диффузионные резисторы.

- •4.7.2 Ионно-легированные резисторы.

- •4.8 Полупроводниковые конденсаторы

- •5.1 Подложки гимс.

- •5.2 Резисторы.

- •5.3 Конденсаторы

- •5.4 Катушки индуктивности

4.6 Полевые транзисторы

4.6.1 Полевые транзисторы с управляющим p-n переходом

Полевые

транзисторы (ПТ) с управляющим p-n

переходом, хорошо вписываются

в общую технологию биполярных ИС и

потому часто изготавливаются совместно

с биполярными транзисторами на одном

кристалле.

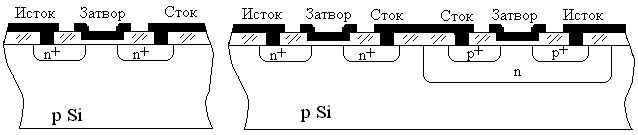

Типичные струк- туры ПТ с каналами

различного типа проводимости

показаны на рисунке 4.14.

|

а) |

б) |

Рисунок 4.14

В структуре n-канального ПТ, показанной на рисунке 4.14а, p-слой затвора образуется на этапе базовой диффузии, а n+-слои, обеспечивающие омический контакт с областями истока и стока, - на этапе эмиттерной диффузии. Заметим, что р-слой затвора окружает сток со всех сторон, так что ток между истоком и стоком может протекать только через управляемый канал под р-слоем.

В n-карманах, предназначенных для ПТ, вместо скрытого n+-слоя целесообразно сформировать скрытый p+-слой. Назначение этого слоя - уменьшить начальную толщину канала и тем самым напряжение отсечки. Осуществление скрытого p+-слоя связано с дополнительными технологическими операциями. Для того чтобы скрытый р+-слой проник в эпитаксиальный n-слой достаточно глубоко, в качестве акцепторного диффузанта используют элементы с большим коэффициентом диффузии (бор или галлий).

На подложку, а значит, и на p+-слой для изоляции элементов подают постоянный максимально отрицательный потенциал; поэтому они не выполняют управляющих функций.

Структура р-канального ПТ, показанная на рисунке 4.14б, совпадает со структурой обычного n-p-n транзистора. Роль канала играет участок базового р-слоя, расположенный между n+- и n-слоями. Если при совместном изготовлении ПТ и биполярного транзистора не использовать дополнительных технологических процессов, то толщина канала будет равна ширине базы n-p-n транзистора (0,5-1 мкм). При такой малой толщине канала получаются большой разброс параметров ПТ и малое напряжение пробоя. Поэтому целесообразно пойти на усложнение технологического цикла, осуществляя p-слой ПТ отдельно от базового р-слоя, с тем чтобы толщина канала была не менее 1-2 мкм. Для этого проводят предварительную диффузию р - слоя ПТ до базовой диффузии. Тогда во время базовой диффузии р-слой ПТ дополнительно расширяется, и его глубина оказывается несколько больше глубины базового слоя.

Для того чтобы области истока и стока соединялись только через канал, n+-слой делают более широким (в плане), чем p-слой. В результате n+-слой контактирует с эпитаксиальным n-слоем и вместе они образуют «верхний» и «нижний» затворы. На рисунке 4.14б, контакт между «верхним» и «нижним» затворами условно показан штриховой линией.

4.6.2 МДП-транзисторы

Вообще говоря, совместное изготовление МДП- и биполярных транзисторов на одном кристалле, в едином технологическом цикле возможно, но является специальным случаем. Как правило, биполярные и МДП-транзисторные ИМС разрабатываются и изготавливаются раздельно. Эти два типа ИМС предназначе- ны либо для решения разных функциональных задач, либо для решения одной и той же задами, но с использованием преимуществ соответствующего класса транзисторов. Главную роль в современной микроэлектронике играют МДП-транзисторы, в которых диэлектриком является SiO2, их называют МОП-транзисторами.

МОП-транзистор.

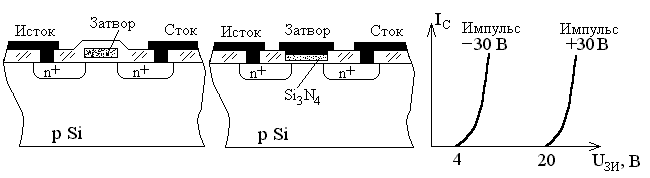

Поскольку интегральные МДП-транзисторы не нуждаются в изоляции, их структура внешне не отличается от структуры дискретных вариантов. На рисунке 4.15а воспроизведена структура МОП-транзистора с индуцированным n-каналом. Отметим особенности этого транзистора как элемента ИМС.

|

а) |

б) |

Рисунок 4.15

Из сравнения с биполярным транзистором очевидна, прежде всего, технологическая простота МОП-транзистора. Необходимы всего лишь один процесс диффузии и четыре процесса фотолитографии (под диффузию, под тонкий подзатворный окисел, под омические контакты и под металлизацию). Технологическая простота обеспечивает меньший брак и меньшую стоимость.

Отсутствие изолирующих карманов способствует лучшему использованию площади кристалла, т. е. повышению степени интеграции элементов. Однако, с другой стороны, отсутствие изоляции делает подложку общим электродом для всех транзисторов. Это обстоятельство может привести к различию параметров у внешне идентичных транзисторов. Действительно, если на подложку задан постоянный потенциал, а истоки транзисторов имеют разные потенциалы (такое различие свойственно многим схемам), то будут разными и напряжения между подложкой и истоками UПИ. Это равносильно различию пороговых напряжений МДП-транзисторов.

Как известно, главным фактором, лимитирующим быстродействие МДП-транзисторов, обычно являются сопротивление каналов и паразитные емкости. Другие варианты МДП-транзисторов, где эти параметры сведены к минимуму, рассмотрены в 4.

В комплементарных МОП-транзисторных ИМС (КМОП) на одном и том же кристалле необходимо изготовлять транзисторы обоих типов: с n- и с р-каналами. При этом один из типов транзисторов нужно размещать в специальном изолирующем кармане. Например, если в качестве подложки используется р-кремний, то n-канальный транзистор можно осуществить непосредственно в подложке, а для р-канального транзистора потребуется карман с электронной проводимостью, на который подается максимальный положительный потенциал (рисунок 4.15б). Получение такого кармана в принципе несложно, но связано с дополнительными технологическими операциями (фотолитография, диффузия доноров и др.). Кроме того, затрудняется получение низкоомных р+-слоев в верхней (сильно легированной) части n-кармана.

Другим способом изготовления КМОП-транзисторов на одной подложке является КНС технология (кремний на сапфире) 5.

Что касается сочетания МОП-транзисторов с биполярными, то в принципе оно осуществляется просто n-канальные транзисторы изготавливаются непосредственно в р-подложке на этапе эмиттерной диффузии, а p-канальные — в изолирующих карманах на этапе базовой диффузии.

В процессе развития микроэлектроники усовершенствование МОП-транзисто- ров происходило по двум главным направлениям: повышение быстродействия и снижение порогового напряжения. В основе последней тенденции лежало стрем -ление снизить рабочие напряжения МОП-транзисторов и рассеиваемую ими мощность. Поскольку полная мощность кристалла ограничена, уменьшение мощности, рассеиваемой в одном транзисторе, способствует, повышению степени интеграции, а уменьшение напряжений питания облегчает совместную работу МОП-транзисторных и низковольтных биполярных ИС без специальных согласующих элементов.

Способы уменьшения порогового напряжения.

Транзисторы со структурой, показанной на рисунке 4.16а, обычно называют МОП-транзисторами с кремниевым затвором. Такие транзисторы характерны не только малой емкостью перекрытия, но и малым пороговым напряжением: 1-2 В вместо обычных 2,5-3,5 В. Это объясняется тем, что материал затвора и подложки один и тот же - кремний. Следовательно, контактная разность потенциалов между ними (MC) равна нулю, что и приводит к уменьшению порогового напряжения [4]. Примерно такой же результат дает использование молибденового затвора.

|

а) |

б) |

в) |

Рисунок 4.16

Помимо контактной разности, потенциалов, для уменьшения порогового напряжения можно варьировать и другими параметрами. Например, можно заменить тонкий окисел SiO2 тонким напыленным слоем нитрида кремния Si3N4, у которого диэлектрическая проницаемость (7) примерно в полтора раза больше, чем у двуокиси кремния (=4,5). Это приводит к увеличению удельной емкости С0, а значит, к уменьшению соответствующих слагаемых порогового напряжения. Нитрид кремния в качестве подзатворного диэлектрика обеспечивает также дополнительные преимущества: меньшие шумы, большую временною стабильность ВАХ и повышенную радиационную стойкость МДП-транзистора.

Сочетая перечисленные методы, можно обеспечить пороговые напряжения практически любой сколь угодно малой величины.

Следует, однако, иметь в виду, что слишком малые значения порогового напряжения (0,5-1 В и менее) в большинстве случаев неприемлемы по схемотехническим соображениям (малая помехоустойчивость).