Задача №3

1.Поясните назначение и особенности передачи данных.

2.Перечислите способы защиты информации от ошибок и поясните принцип формирования полных кодовых комбинаций циклического кода.

3.Начертите функциональную схему кодирующего устройства циклического кода, образованного,заданным в табл.5 образующим полиномом и поясните принцип ее работы.

№ варианта |

1 |

2 |

3 |

4 |

5 |

Образующий полином |

х4+х+1 |

х3+х2+1 |

х+х+1 |

х4+х3+1 |

х4+х3+х2+х+1 |

№ варианта |

6 |

7 |

8 |

9 |

10 |

Образующий полином |

х5+х2+1 |

х5+х3+1 |

х5+х4+х2+х+1 |

х5+х4+х2+х+1 |

х5+х4+х3+х+1 |

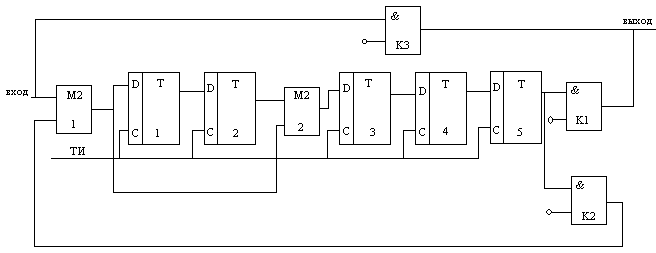

Образующий полином имеет вид х5+х2+1. В этой схеме по цепи обратной связи через электронный ключ К2 поступают разряды на второй вход первого сумматора поступает сумма по модулю 2, полученная на выходе первого сумматора. В этом случае все операции кодирования будут происходить на ξ – число проверочных, n – общее число разрядов в полной кодовой комбинации.

Работа происходит в следующей последовательности (см.табл.2)

Предположим, что кодированию подлежит комбинация вида 101111001011110001011. Под действием 1 – го тактового импульса 1 – й разряд комбинации поступает на 1-й вход 1-го сумматора по модулю 2, записывается в первую ячейку памяти и одновременно на 2-й вход 2-го сумматора, соответственно записывается в 3-ю ячейку памяти.

Под действием 2-го тактового импульса 2-й разряд кодовой комбинации поступает не первый вход 1-го сумматора, записывается в 1-ю ячейку памяти, записанный ранее разряд переписывается во 2-ю ячейку. Одновременно этот же разряд поступает на 2-й вход 2-го сумматора, записывается в 3-ю ячейку памяти, а записанный там ранее разряд переписывается на 4-ю ячейку памяти. Дальше работа проходит аналогично. В цепи обратной связи появятся разряды только после 4-го тактового импульса и поступят на 2-й вход 1-го сумматора. Всю работу можно проследить с помощью табл.2

После 2-го ТИ в 5-ти ячейках памяти запишутся проверочные разряды. Поэтому при действии 22-го ТИ электронный ключ К2 должен быть заперт, а К1 – открыт. На выход схемы должны поступать только проверочные разряды.

№ ТИ |

Вход |

М2 |

Т1 |

Т2 |

М22 |

Т3 |

Т4 |

Т5 |

Цепь обратной связи |

Выход |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

1 0 1 1 1 1 0 0 1 0 1 1 1 1 0 0 0 1 0 1 1 - - - - - |

1+0 0+0 1+0 1+1 1+0 1+0 0+0 0+0 1+1 0+1 1+1 1+0 1+1 1+0 0+0 0+0 0+0 1+0 0+1 1+0 1+1 - - - - - |

1 0 1 0 1 1 0 0 0 1 0 1 0 1 0 0 0 1 1 1 0 |

0 1 0 1 0 1 1 0 0 0 1 0 1 0 1 0 0 0 1 1 1 0 |

0+1 0+0 1+1 0+0 1+1 0+1 1+0 1+0 0+0 0+1 0+0 1+1 0+0 1+1 0+0 1+0 0+0 0+1 0+1 1+1 1+0 - - - - - |

1 0 0 0 0 1 1 1 0 1 0 0 0 0 0 1 0 1 1 0 1 1 0 - - - |

0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 0 1 0 1 1 0 1 1 0 - - |

0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 0 1 0 1 1 0 1 1 0 - |

- - - 1 0 0 0 0 1 1 1 0 1 0 0 0 0 0 1 0 1 - - - - - |

1 0 1 1 1 1 0 0 1 0 1 1 1 1 0 0 0 1 0 1 1 1 0 1 1 0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |