- •«Пермский национальный исследовательский политехнический университет»

- •«Встроенные микропроцессорные системы»

- •Составитель о.В. Гончаровский

- •Оглавление

- •2. Программное обеспечение встроенных систем ……….

- •Введение

- •Аппаратные средства встроенных систем

- •Организация аппаратных средств встроенных

- •1.2. Элементы архитектуры процессоров встроенных систем

- •1.2.1. Множество команд

- •1.2.3.1. Адресное пространство

- •1.2.3.2. Порядок байт

- •1. 2.3.3. Когерентность памяти

- •1. 2.3.4. Защита памяти

- •1. 2. 4. Модель прерываний

- •1.2. 5.Модель управления памятью

- •1.2.5.1. Страничная организация памяти

- •1.2.5.2. Сегментация памяти

- •1.3. Типы процессоров

- •1.4. Формы параллелизма в процессорах

- •1.4.1. Конвейеризация

- •1.4.2. Параллелизм уровня команд

- •1.5.Технологии памяти

- •1.5.1. Оперативная память

- •1.5.1. 1. Статическое озу

- •1.5.2. Постоянное запоминающее устройство (rom)

- •1.6. Иерархия памяти

- •1.6.1. Распределение или карта памяти

- •1.6.2. Блокнотная и кэш память

- •1.6.2.2. Ассоциативная по множеству кэш-память

- •1.6.2.3. Обновление кэш-памяти.

- •1.6.2.4. Протокол когерентности кэширования с обратной записью

- •1.7. Магистраль микропроцессорной системы

- •1.8. Базовые устройства ввода-вывода встроенных систем

- •1.8.1. Порты ввода-вывода общего назначения

- •1.7.2. Таймер-счетчик

- •1.8.3. Импульсно-кодовая модуляция.

- •1.8.4. Многоканальный аналого-цифровой преобразователь

- •1.9. Базовые последовательные интерфейсы ввода-вывода

- •1.9.2. Последовательный интерфейс spi

- •1.9.4.1. Введение в usb

- •1.9.4.2. Интерфейс Open Host Controller для usb

- •Вопросы для самопроверки

- •Модуль 2

- •1.10. Язык проектирования аппаратуры vhdl

- •1.10.2. Введение в vhdl

- •1.10.2.1. Программирование на vhdl для моделирования и синтеза [22]

- •1.10.2.3. Операторы присваивание и process [22]

- •1.10.2.4. Цикл моделирования vhdl

- •1.10.2.5. Многозначная логика и стандарт ieee 1164

- •1.11. Проектирование устройств ввода-вывода и контроллеров

- •1.12. Интегрированная среда разработки аппаратных средств

- •Вопросы для самопроверки

- •Модуль 3

- •2. Программное обеспечение встроенных систем

- •2.1 Модель вычислений

- •2.2 Автомат с конечным числом состояний

- •2.3. Асинхронный язык проектирования sdl

- •2.4. Синхронный язык проектирования Lustre

- •2.5. Многозадачность.

- •2.5.1. Язык программирования Си

- •2.5.2. Потоки

- •2.5.2.1. Реализация потоков

- •2.5.2.2. Взаимное исключение

- •2.5.2.3. Взаимная блокировка

- •2.5.2.4. Модели непротиворечивости памяти

- •2.5.2.5. Проблемы с потоками

- •2.5.3. Процессы и передача сообщений

- •2.6. Интегрированная среда разработки прикладного программного

- •2.6.2. Комплект программ Telelogic Tau sdl Suite

- •2.6.3. Средства разработки программного обеспечения

- •2.7.1. Моделирование, эмуляция и макетирование

- •2.7.2. Формальная верификация

- •2.7.3. Оценка производительности

- •2.7.3.1. Оценка wcet

- •2.7.3.2. Исчисление реального времени

- •2.7.4. Модели энергии и мощности

- •2.7.5. Тепловая модель

- •Задания

- •1. Конвейеризация

- •2. Иерархия памяти

- •3. Базовые устройства ввода-вывода встроенных систем

- •5. Многозадачность

- •6. Валидация и оценка проекта

- •Заключение

- •Библиографический список

- •Встроенные микропроцессорные системы

1.10.2. Введение в vhdl

Существует два популярных представителя группы языков HDL (Hardware Description Language), предназначенных для описания цифровых аппаратных средств, это Verilog и VHDL: первый более краткий, менее гибкий, менее приятный; второй многословный, очень гибкий и более приятный.

История VHDL восходит к 80-м годам прошлого века. В это время многие системы проектирования использовали графические HDL, когда наиболее общим строительным блоком был логический вентиль. Однако разработчики использовали и текстовые HDL, преимущество которых состояло в простоте представления сложных преобразований с использованием переменных, циклов и рекурсий. По мере усложнения устройств текстовые HDL почти полностью вытеснили графические.

Язык VHDL (VHSIC Hardware Description Language) был разработан в рамках программы VHSIC (Very High Speed Integrated Circuits) министерства обороны Соединенных Штатов.

В 1987 VHDL приобрел статус стандарта IEEE (IEEE Std. 1076 - 1987). В 1993 после ревизии начальной версии стал VHDL’93, и далее на его основе VHDL’98, VHDL’2000, VHDL’2002, VHDL’2006, VHDL’2008, а подмножество VHDL AMS (Analog Mixed Signal) позволяет описывать как чисто аналоговые, так и смешанные, цифро-аналоговые схемы.

При разработке VHDL использовался язык программирования ADA, как отправная точка, т.к. оба языка разрабатывались для министерства обороны. В свою очередь ADA базируется на PASCAL, поэтому VHDL является синтаксическим сленгом PASCAL. Однако синтаксис VHDL более сложный.

1.10.2.1. Программирование на vhdl для моделирования и синтеза [22]

Программа на VHDL используется как модель, отражающая некоторое устройство. Система моделирования исполняет программу на VHDL, имитируя работу реального устройства. Поведение устройства представляется в модели через события изменения сигналов и формируемые временные диаграммы сигналов. Наблюдая это поведение, разработчик анализирует свой проект, делает выводы о его правильности. Здесь программа на VHDL рассматривается как модель – VHDL программа-модель.

Синтез является обратным процессом. При синтезе программа на VHDL рассматривается как спецификация, детальное описание, исходные данные и требования, по которым должна быть сгенерирована реализация физического устройства на СБИС. Синтезирующие компиляторы САПР по программе на VHDL генерируют реализацию проектируемого устройства. Здесь программа на VHDL выступает как программа-спецификация для синтеза.

Не всякая программа-модель может быть использования как программа-спецификация для синтеза. Не для всякой программы на VHDL ее поведение при моделировании будет соответствовать поведению устройства, синтезированного по этой же программе. Поэтому говорят о синтезируемом подмножестве языка VHDL. Имеется в виду та часть конструкций и понятий VHDL, которые могут использоваться в программе-спецификации для синтеза, исключая запрещенные для синтеза конструкции. Однако такого стандартизованного подмножества не существует.

Компиляция устройства по VHDL программе-спецификации может использовать разные наборы элементов (элементный базис). Базис реализации может состоять из элементов разного уровня – от вентилей и логических блоков табличного типа (LUT) до макроячеек сложных функциональных блоков – мультиплексоров, регистровых блоков, блоков памяти, умножителей и процессорных ядер. После компиляции производится оптимизация схемы с целью увеличения быстродействия или сокращения аппаратных затрат, уменьшения размеров на кристалле. Оптимизация схемы приводит к ее трансформациям, иногда весьма существенно меняющей структуру, которая просматривается в исходном тексте. Результатом может быть расхождение в поведении модели устройства и поведении реализации устройства, синтезированной по той же программе на VHDL. Разработчик должен учитывать возможность таких трансформаций, когда пишет программу-спецификацию.

Те или иные программные конструкции VHDL синтезирующий компилятор может принимать или игнорировать, т.е. данная конструкция, ее секция или атрибут не будут влиять на результат синтеза схемы.

1.10.2.2. Entity и architecture

VHDL, как и все HDL, включает необходимые средства для поддержки моделирования одновременной работы аппаратных компонент. Аппаратные компоненты моделируются с помощью конструкции entity. Entity содержит несколько операторов process для моделирования одновременных действий. Entity образуется из двух типов составляющих: декларации entity и одной или нескольких architecture (рис. 45).

Рис. 45. entity состоит из декларации entity и одной или нескольких architecture

В качестве примера рассмотрим полный сумматор (full adder) на рис. 46.

Рис. 46. Полный сумматор и его интерфейсные сигналы

Его декларации entity соответствует следующий текст:

entity

full_adder

is

--

декларации

entity

port

(

a,

b, carry_in: in

Bit;

-- входные

порты

sum,

carry_out: out

Bit

--

выходные

порты

)

;

end

full

adder;

Два дефиса (--) обозначают начало комментария и действуют до конца строки. Architecture состоит из заголовка и тела. Различают два стиля написания архитектурных тел: структурное и поведенческое.

Поведенческое тело включает только информацию достаточную для вычисления значений выходных сигналов по значениям входных и состоянию внутренних сигналов. Поведенческое тело full_adder выглядит следующим образом (<= обозначает оператор присвоения значения сигналу):

architecture

behavior

of

ful_adder

is

--

architecture begin

sum

<=

(a xor b) xor carry_in after

10

ns;

carry_out

<=

(a and b) or (a and carry_in) or (b and carry_in) after

10

ns; end

behavior;

Напротив структурное тело описывает композицию из более простых

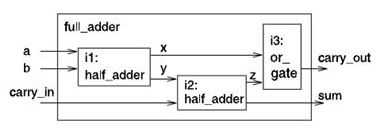

Entit (рис. 47) . В примере компоненты названы от i1 до i3 и принадлежат к типам half _adder или or_gate.

Рис. 47. Схема структурного тела full_adder

В текстовом виде эта структура представляется следующим образом:

architecture

structure

of

full

adder is

--

заголовок

component

half_adder port

(in1,

in2: in

Bit;

carry: out

Bit;

sum: out

Bit); end

component;

component

or_gate port

(in1,

in2: in

Bit;

o: out

Bit); end

component; signal

x,

y, z: Bit;

-- локальные

сигналы begin

--

секция

карты

портов i1:

half_adder -- введение

компонента i1 типа

half_adder

port

map

(in1=>

a, in2=> b, carry => x, sum => y); -- связи

между

портами

i2:

half_adder port

map

(in1=>

y, in2=> carry_in, carry=>z, sum => sum);

i3:

or_gate port

map

(in1=>

x, in2=> z, o => carry_out);

end

structure;

Конструкции port map описывают связи между локальными компонентами, портами component и портами entity с помощью символов =>.