- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

7.3. Системный контроллер вг88

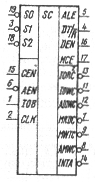

Микросхема К1810ВГ88 [61] является однокристальным устройством, предназначенным для согласования локального интерфейса МП К1810ВМ86/ВМ88, работающего в максимальном режиме, с системной магистралью типа И41. Системный контроллер (рис. 7.5) содержит дешифратор состояния, управляющую логику, генератор командных сигналов и генератор сигналов управления. Работа БИС синхронизируется тактовой последовательностью CLK, которая используется для синхронизации МП (рис. 7.6).

Дешифратор состояния фиксирует генерируемые МП сигналы состояния — (Status) и декодирует их для определения типа выполняемого цикла. Фиксация очередного состояния осуществляется по срезу сигнала V V , формируемого внутренней логикой дешифратора.

Декодированные в соответствии с табл. 6.16 сигналы состояния используются для генерации ряда командных стробов:

Чтение памяти

Запись в память

![]() Запись

в память с упреждением

Запись

в память с упреждением

Чтение портов

Запись в порты

Запись в порты с упреждением

Подтверждение прерывания

В зависимости от числа и способа формирования команд различают два основных режима работы контроллера: режим системной шины и режим шины ВВ, программируемые с помощью управляющего вывода IOВ (Input/Output Bus).

В режиме системной шины (IOВ = 0) все семь стробов возможны. Однако их генерация разрешается только при активном сигнале (Address Enable), который обычно формирует внешняя логика шинного арбитража. Управляющий сигнал может рассматриваться как сигнал разрешения доступа к шине, обеспечивающий возможность параллельной работы на одной магистрали нескольких активных устройств. При = 1 не ……… состояние изменяется.

В режиме шины ВВ

(IOВ = 1)

раэрешаетея

генерация только

четырех команд:

,

,

и

.

При этом их формирование уже не зависит

от состояния сигнала

,

т. е. функция арбитража в данном

режиме не поддерживается. Вместе с

командами системный контроллер генерирует

ряд сигналов, управляющих формирователем

шины данных и буферными регистрами шины

адреса:

ALE Строб фиксации адреса

DEN Разрешение работы драйвера шины данных

Прием/передача данных

![]() Разрешение

работы главного модуля или разрешение

работы драйвера шины ВВ

Разрешение

работы главного модуля или разрешение

работы драйвера шины ВВ

Строб ALE (Address Latch Enable) разрешает фиксацию адреса в буферных регистрах МС (ALE = 1). Сигнал DEN (Data Enable) определяет временной интервал подключения локальной шины МП к внешней шине (DEN = 1), а сигнал (Data Transmission/Receipt) управляет направлением передачи данных от МП ( = 1) или к МП ( = 0). Обычно эти сигналы используются для управления работой двунаправленного формирователя шины данных. Вывод имеет две функции, которые соответствуют двум режимам работы контроллера.

В режиме системной магистрали (IOВ = 0) генерируется сигнал МСЕ (Master Slave Enable), который действует только в цикле подтверждения прерывания. Он информирует о работе ведущего контроллера прерываний и может быть использован при организации каскадного расширения в том случае, когда ведущий контроллер находится на локальной шине МП, а подчиненные—на системной шине. (Более подробно об этом см. § 7.6.)

В режиме шины ВВ

(IOВ = 1) вывод выполняет

функцию

![]() (Peripheral Data Enable). Сигнал

разрешает передачу данных с или на шину

ВВ, служащую шиной ПУ. Временные параметры

сигнала такие же, как у управляющего

сигнала DEN. Еще один входной

управляющий сигнал CEN

(Command Enable)

служит для перевода командных линий,

DEN,

PDEN

в неактивное

(Peripheral Data Enable). Сигнал

разрешает передачу данных с или на шину

ВВ, служащую шиной ПУ. Временные параметры

сигнала такие же, как у управляющего

сигнала DEN. Еще один входной

управляющий сигнал CEN

(Command Enable)

служит для перевода командных линий,

DEN,

PDEN

в неактивное третье

состояние (CEN = 0).

Микросхема К1810ВГ88 выполнена по биполярной технологии и упакована в 20-выводный кристаллодержатель 2140Ю.20 с вертикальным расположением выводов (рис. 7.7). Для работы БИС требуется один источник питания +5 В, ток потребления ICC ≤ 230 мА. Нагрузочная способность командных линий: IOL = 32мА СL = 300 пФ, линий управления: IOL = 16 мА, СL = 80 пФ.

Рис. 7.7. Условное графическое обозначение контроллера К1810ВГ88