- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

7.2. Генератор тактовых импульсов гф84

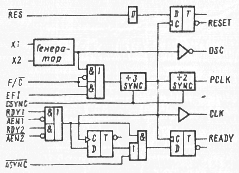

Микросхема К1810ГФ84 [61] является однокристальным ГТИ, специально спроектированным для МП К1810ВМ86. В состав микросхемы (рис. 7.3) входит стабилизируемый кварцем генератор, делитель на 3, а также логика синхронизации сигналов готовности и сброса.

Рис. 7.3. Схема генератора тактовых импульсов К1810ГФ84

Встроенный в БИС генератор рассчитан для работы с внешним кварцевым резонатором, который подключается к входу X1 и выходу Х2. Частота кварцевого резонатора должна быть в 3 раза больше, чем требуемая МП частота CLK. Для достижения наиболее стабильной работы входных цепей генератора рекомендуется точки Х1 и Х2 подключить к общей шине через резисторы сопротивлением 510 Ом. Полезно также последовательно с кварцевым резонатором подключить конденсатор небольшой емкости (около 15 пФ). Выход генератора подключается непосредственно к выводу OSC, так что внешние средства при необходимости могут воспользоваться основной тактовой частотой ГТИ.

Основная системная частота CLK получается путем деления частоты OSC на 3. Длительность импульсов на выходе CLK составляет 1/3 периода, что соответствует требованиям, предъявляемым МП. Еще один выходной синхросигнал PCLK представляет собой меандровую последовательность импульсов с частотой, равной половине частоты CLK. В случае стандартного значения частоты CLK 5 МГц, частота PCLK составляет 2,5 МГц. Этот синхросигнал предназначен для формирования основной тактовой последовательности CCLK для ПУ. Установочный вход CSYNC позволяет синхронизировать CLK и PCLK, например, с другим ГТИ.

Микросхема

предусматривает возможность работы от

внешнего генератора импульсов

OSC, которые подаются на вход EFI.

Выбор между внутренним и внешним

генератором OSC реализуется

с помощью управляющего входа

![]() .

При

= 0 выбирается внутренний генератор, в

противном случае—внешний.

.

При

= 0 выбирается внутренний генератор, в

противном случае—внешний.

Логика формирования сигнала сброса RESET включает триггер Шмитта и синхронизирующий D-триггер, срабатывающий по срезу CLK. Применение на входе RES пороговой схемы позволяет формировать сигнал сброса при нажатии клавиши RESET с помощью простой RC-цепочки подобно тому, как это сделано на рис. 2.17 при использовании БИС КР580ГФ24. Полученный на выходе RESET сигнал сброса соответствует требованиям, накладываемым на него МП К1810ВМ86 (см. § 6.6).

Логика формирования

сигнала готовности READY

предусматривает синхронизацию входного

сигнала готовности RDY1

или RDY2. Выбор входа

осуществляется управляющими сигналами

![]() и

и

![]() .

Симметричность пары RDY,

.

Симметричность пары RDY,

![]() допускает использование в качестве

входа готовности инверсную линию

,

тогда как прямая линия RDY

может служить управляющей.

допускает использование в качестве

входа готовности инверсную линию

,

тогда как прямая линия RDY

может служить управляющей.

Различают два типа

входных сигналов готовности: асинхронный

и синхронный, в соответствии с которыми

предусматриваются и два типа синхронизации.

Выбор типа синхронизации осуществляется

по уровню напряжения на линии

![]() .

При

= 0 реализуется двухступенчатая

логика синхронизации асинхронного

сигнала готовности, в противном

случае—одноступенчатая логика

синхронизации синхронного сигнала

готовности.

.

При

= 0 реализуется двухступенчатая

логика синхронизации асинхронного

сигнала готовности, в противном

случае—одноступенчатая логика

синхронизации синхронного сигнала

готовности.

В случае двухступенчатой синхронизации ( = 0) переход входного сигнала готовности из 0 в 1 будет синхронизироваться сначала по фронту, а затем по срезу CLK. Переход входного сигнала из 1 в 0 будет всегда синхронизироваться только по срезу CLK. Такая схема синхронизации ориентирована на использование с асинхронными системными каналами с неготовым по умолчанию сигналом ответа .

При одноступенчатой синхронизации ( = 1) входной сигнал готовности тактируется только срезом CLK. Этот способ применим в системах, которые гарантируют синхронность формирования сигнала подтверждения обмена или готовности.

Вход имеет встроенный резистор, подключенный к шине питания. Поэтому допускается вход оставлять свободным, что соответствует ситуации ASYNC = 1.

Микросхема К1810ГФ84 упакована в 18-выводный корпус типа 2104.18. Условное обозначение и распределение сигналов по выводам приведено на рис. 7.4.

Рис. 7.4. Условное графическое обозначение

генератора тактовых импульсов К1810ГФ84

Рис. 7.5. Схема системного контроллера К1810ВГ88 |

Рис. 7.6. Временные диаграммы работы системного контроллера К1810ВГ88 |