- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

6.3. Организация памяти вм86

В МП ВМ86 существует два уровня представления памяти. На нижнем физическом уровне память организована в виде монолитного 1M-байтового блока 1М8, каждый байт которого может быть адресован отдельно. Такое пространство и его адрес называют линейными. В МП ВМ86 линейный адрес эквивалентен физическому, т. е. тому, который присутствует на адресной шине.

Слова в линейной памяти занимают два любых соседних байта. В байте с младшим адресом хранится младшая часть слова. Его адрес служит адресом всего слова и может быть как четным, так и нечетным. Двойные слова размещаются как два соседних слова. Младшее слово располагается по младшему адресу, его адрес служит адресом двойного слова.

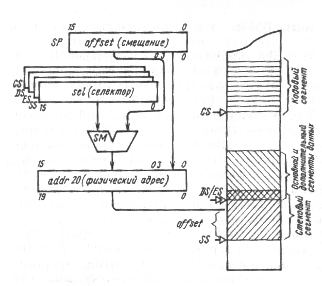

Для адресации блока в 1 Мбайт необходим 20-разрядный линейный адрес addr20. Однако программист оперирует не этими физическими адресами, а так называемыми логическими адресами. Каждый логический адрес—это пара sel: offset, состоящая из 16-разрядного селектора сегмента sel и 16-разрядного смещения внутри сегмента offset.

Множество логических адресов образует сегментированное адресное пространство логической памяти, состоящей из ряда изолированных друг от друга частей—сегментов. Селектор может рассматриваться как указатель сегмента. Всего возможно 216 логических сегментов. Каждый сегмент хранит функционально законченную часть объектного кода или отдельный набор данных к нему. Отдельный сегмент должен быть отведен для стека той или иной программы. В общем случае сегментированная память отображает модульную организацию программ, что может быть использовано для поддержки модульного программирования. Размер логического сегмента не фиксирован и зависит от его конкретного функционального назначения.

Второй компонент логического адреса—смещение—определяет расстояние от начала сегмента до объекта, расположенного внутри него. Разрядность данной компоненты определяет максимально возможный размер сегмента 64К байт. В целом объем логического пространства адресов составляет 4 Гбайт (Г = 230).

Возникает задача отображения логических сегментов в линейную физическую память. Селектор сегмента однозначно связан с базовым линейным адресом сегмента, определяющим его расположение в линейном пространстве:

base20 = 16 • sel

Линейный адрес объекта формируется из логического как сумма базы сегмента и смещения объекта в нем:

addr20 = base20 + offset = 16 • sel + offset

Один и тот же линейный адрес представляется множеством логических адресов.

В командах, как правило, используется неявный способ задания селектора, в качестве которого всегда выступает содержимое одного из четырех сегментных регистров. Вторая компонента логического адреса offset может быть определена различными традиционными способами.

Сегментные регистры CS—ES выделяют в памяти объемом 1 Мбайт четыре сегмента до 64К байт каждый. Сегменты выравнены по границе 16 байт (граница параграфа) и могут частично или полностью перекрываться друг с другом, как показано на рис. 6.3. Эти сегменты в отличие от остальных будем называть открытыми для доступа, вкладывая в это понятие тот смысл, что их селекторы хранятся в сегментных регистрах и, следовательно, доступ к ним открыт.

Рис. 6.3. Схема преобразования адресов

Неявный способ задания сегментного регистра обусловливает функциональную специализацию сегментов. В зависимости от используемого сегментного регистра различают кодовый сегмент, стековый сегмент, а также основной и дополнительный сегменты данных.

Регистр CS служит для указания кодового сегмента, который хранит объектный код. Содержимое CS используется для определения базы сегмента всякий раз, когда выполняется выборка объектного кода. При этом смещением в сегменте выступает значение программного счетчика IP.

При обращении к стеку (offset = SP) селектор извлекается из регистра SS. Поэтому указываемый им сегмент называется стековым и служит для организации системного стека.

Данные обычно располагаются в основном сегменте данных, база которого хранится в DS. Смещение offset в сегменте определяется одним из традиционных способов формирования исполнительного адреса.

В правилах адресации данных существует три исключения. Так, если при обращении к данным используется один из способов базовой адресации по ВР, то в качестве указателя сегмента служит SS. Этот вариант адресации эффективен при передаче параметров через текущий кадр системного стека. Указателем кадра является адресный регистр ВР.

При обработке строк регистр DS служит указателем сегмента исходной строки, смещение в сегменте извлекается из индексного регистра SI. При этом результирующая строка размещается в дополнительном сегменте данных, указателем которого служит ES. Смещение строки-результата определяется по содержимому DI. Одновременное применение двух сегментов позволяет реализовать эффективную передачу данных между сегментами.

Эти используемые по умолчанию правила выбора сегментных регистров приведены в табл. 6.1. В ряде случаев существует возможность замены сегментного регистра, которая реализуется явным указанием сегментного регистра с помощью специального байта-префикса, предшествующего команде. Однако эти возможности ограничены. С помощью префикса можно изменить только сегмент данных, за исключением обращения к строке-результату. Выборка команды, обращение к стеку и размещение результирующей строки всегда выполняется с помощью CS, SS и ES соответственно.

Таблица 6.1

Вид обращения к памяти |

Селектор по умолчанию |

Возможные варианты |

Смещение offset |

Выборка команды Обращение к стеку Обращение к переменной кроме нижеуказанных Обращение к переменной по базе ВР Обращение к исходной строке Обращение к результирующей строке |

CS SS DS

SS DS ES |

CS, ES, SS

CS, ES, DS CS, ES, SS |

Исполнительный адрес

Исполнительный адрес SI DI |

Сегментирование памяти позволяет оформлять позиционно независимые и динамически перемещаемые программные модули, которые сами не должны изменять содержимое сегментных регистров, т. е. все смещения и переходы в программе должны выполняться относительно неизвестных, но фиксированных значений сегментных регистров.