- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

Глава 5.

ОРГАНИЗАЦИЯ ОДНОПЛАТНЫХ

МИКРОКОНТРОЛЛЕРОВ НА БАЗЕ КР580ВМ80

5 .1. Одноплатный микроконтроллер мМс1204

Микроконтроллеры—наиболее массовый класс микроЭВМ, встраиваемых в различные системы управления реального времени. Они отличаются достаточными для хранения рабочих программ и данных емкостями ПЗУ и ОЗУ соответственно, развитой системой ВВ, малыми габаритными размерами и мощностью потребления. Для построения МК могут быть использованы различные наборы микропроцессорных БИС. Лучше всего для этой цели подходят n-канальные БИС серии КР580, которые были положены в основу семейства одноплатных МК мМС1200.

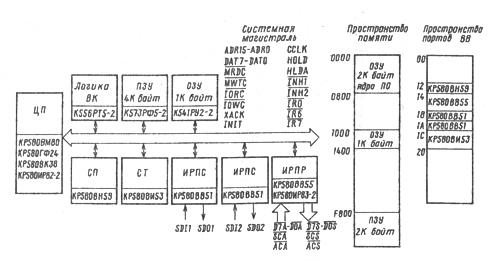

Базовой моделью семейства является МК мMC1204 [52, 53], который представляет собой законченную одноплатную МС общего назначения с магистрально-модульной архитектурой открытого типа (рис. 5.1). Основой МС служит шина типа И41. На плате отсутствуют какие-либо средства для реализации специальных функций, ориентированных на конкретные применения. Специфичность и разнородность таких средств привели бы к перегрузке платы и ее неэффективному использованию. Поэтому основное внимание было уделено интегрированию действительно универсального базового набора программно-аппаратных средств, обладающего функциональной завершенностью и обеспечивающего применение МК в качестве ядра информационных систем.

Рис. 5.1. Схема одноплатного микроконтроллера мМС1204

В состав МК (см. рис. 5.1) входят: 8-разрядный ЦП, ПЗУ, ОЗУ, два последовательных интерфейса типа ИРПС и параллельный интерфейс типа ИРПР. Системный таймер (СТ) совместно с 8-уровневой системой прерываний (СП) обеспечивает поддержку режима реального времени [49], который характерен для многих применений МК. Внутрисистемная магистраль организует многоплатные расширения МК с помощью специальных и системных модулей, таких как модуль аналогового ВВ или системная память соответственно.

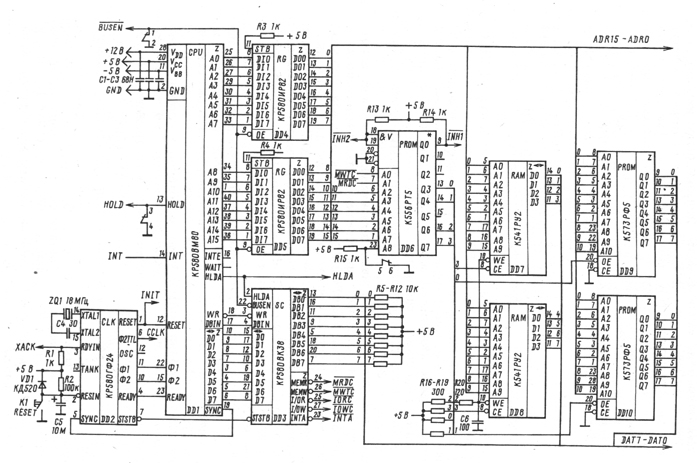

Схема ЦП и памяти МК приведена на рис. 5.2. При построении ЦП на базе МП КР580ВМ80 была использована типовая схема (см. рис. 3.7), в состав которой кроме МП входит ГТИ КР580ГФ24 и системный контроллер КР580ВК38.

Рис. 5.2. Схема центрального процессора и памяти микроонтроллера мМС1204

В МК используется активная по умолчанию линия подтверждения обмена ХАСК, что гарантирует компактность как одноплатного ядра, так и многоплатного его расширения (см. § 2.6). Дополнительная буферизация шины адреса увеличила ее нагрузочную способность до I0L = 32 мА, СL = 300 пФ. Нагрузочная способность шины данных: I0L = 10 мА, CL = 100 пФ. Дополнительные задержки в шинах адреса и данных составляют 35 и 30 нс соответственно.

Память МК должна включать как постоянную для хранения программ и констант, так и оперативную для хранения переменных. Понятно, что емкость ПЗУ должна быть намного больше емкости ОЗУ, конкретные значения которых зависят от области применения МК и многих других факторов. Опыт показывает, что большое число современных управляющих программ занимают область около 4К байт и более. По этой причине на плате МК следует предусмотреть одно или два места для установки микросхем УСППЗУ типа К573РФ2/РФ4/РФ5/РФ6 [36]. Также могут быть использованы любые другие ПЗУ емкостью (2—32)К байт, совместимые по разводке, например, с УСППЗУ 27128 или 27256 фирмы Intel. Применение двух кристаллов К573РФ2/РФ5 данного семейства обеспечивает минимальную емкость ПЗУ 4К байт. Две 32К-байтовые микросхемы покрывают все адресное пространство МК.

Схема МК на рис. 5.2 имеет два места для установки УСППЗУ К573РФ2/РФ5 или ППЗУ КР556РТ7. При включении напряжения питания или нажатии клавиши RESET управление передается на ячейку памяти с нулевым адресом. Поэтому одна микросхема занимает первые 2К байт адресного пространства МК, другая, размещенная в старшей части пространства, —область 0F800H—0FFFFH. По усмотрению пользователя это УСППЗУ может быть перемещено в любую другую область.

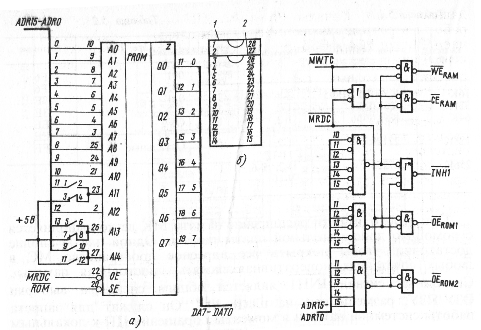

Другой подход состоит в использовании универсальной панельки (рис. 5.3), допускающей применение любой микросхемы с цоколевкой семейства К573РФ2/РФ4/РФ5/РФ6. Каждый тип микросхем устанавливается в панельку одним из двух возможных способов (табл. 5.1). В зависимости от типа УСППЗУ ставятся перемычки, обеспечивающие правильное подключение микросхемы. На рис. 5.3, а приведена схема подключения БИС К573РФ2/РФ5, которая должна быть вставлена в панельку вторым способом.

Таблица 5.1

Емкость, байт |

Тип УСППЗУ |

Перемычки |

Способ установки |

16К |

К573РФ2/РФ5 |

3-4, 7-8 |

2 |

32К |

К573РФ4 |

1-2, 7-8 |

2 |

64К |

К573РФ6 |

1-2, 7-8, 11-12 |

1 |

128К |

27128 |

1-2, 5-6, 11-12 |

1 |

256К |

27256 |

1, 2, 5-6, 9-10 |

1 |

Рис. 5.3. Универсальная панелька: а—схема подключения; б—установка микросхемы памяти (1, 2—способы установки) |

Рис. 5.4. Схема подключения приборов памяти

|

Оперативная

память МК может быть небольшой. В системе

на рис. 5.2 это ОЗУ 1К байт, которое

реализуется на двух микросхемах

статического типа К541РУ2 [36] с организацией

1К4.

Базовый адрес ОЗУ 1000Н. Лучше всего для

этой цели подходят микросхемы с байтовой

организацией, например 2К-байтовая

микросхема К537РУ8/РУ9 [36]. Наряду с линиями

выбора кристалла

![]() и разрешения записи

и разрешения записи

![]() они имеют отдельную линию разрешения

считывания

,

которая подключается непосредственно

к командной линии

.

они имеют отдельную линию разрешения

считывания

,

которая подключается непосредственно

к командной линии

.

Для подключения кристаллов ОЗУ и ПЗУ к системной магистрали требуется дополнительная логика, которую удобно формировать на биполярных ППЗУ или ПЛМ [13, 50]. В МК эта логика реализуется с помощью схемы, представленной на рис. 5.4.

При

необходимости расширение памяти МК

легко выполняется с помощью дополнительной

платы памяти. Одной платы вполне

достаточно, чтобы покрыть все адресное

пространство МС в любых сочетаниях

«оперативная память—постоянная память».

Системный сигнал

![]() является общим сигналом выборки ОЗУ/ПЗУ,

размещенных на плате МК. Он служит для

запрета работы системной памяти в

моменты обращения ЦП к локальным

ресурсам. Сигнал

формируется буфером с открытым

коллектором, что необходимо для его

объединения по схеме «монтажное ИЛИ»

с аналогичными сигналами запрета от

других модулей системы.

является общим сигналом выборки ОЗУ/ПЗУ,

размещенных на плате МК. Он служит для

запрета работы системной памяти в

моменты обращения ЦП к локальным

ресурсам. Сигнал

формируется буфером с открытым

коллектором, что необходимо для его

объединения по схеме «монтажное ИЛИ»

с аналогичными сигналами запрета от

других модулей системы.

Для построения логики выборки кристаллов ПЗУ/ОЗУ используется младшая часть адресного пространства ППЗУ К556РТ5, содержимое которого представлено в табл. 5.2. Оставшаяся часть ППЗУ может быть запрограммирована для другого распределения областей ОЗУ и ПЗУ в пространстве памяти МК. Применение программируемой пользователем логики позволило сократить число корпусов на плате и стандартизировать монтажную схему независимо от распределения физической памяти в адресном пространстве микроЭВМ.

Таблица 5.2

Адрес ПЗУ |

Состояние |

001 |

F6 |

005 |

F6 |

011 |

7E |

012 |

3E |

OF9 |

EE |

OFD |

EE |

Остальное |

FF |

Следует учитывать, что при использовании ППЗУ в моменты его переключения возможно появление на выходах микросхемы кратковременных ложных выбросов. Особую опасность эти выбросы представляют только для линии ОЗУ. Для их сглаживания рекомендуется включать дополнительную RC-цепочку.

Размещенную

на плате МК память можно отключить, если

активизировать линию

![]() .

При этом становится безусловно пассивной

линия

и открывается доступ к внешней системной

памяти. Управление линией

осуществляется внешними средствами.

Сигнал

может быть полезен при запретe доступа

в местную память со стороны внешних

активных модулей. Для этого достаточно

выполнить соединение

= BUSEN.

.

При этом становится безусловно пассивной

линия

и открывается доступ к внешней системной

памяти. Управление линией

осуществляется внешними средствами.

Сигнал

может быть полезен при запретe доступа

в местную память со стороны внешних

активных модулей. Для этого достаточно

выполнить соединение

= BUSEN.