- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

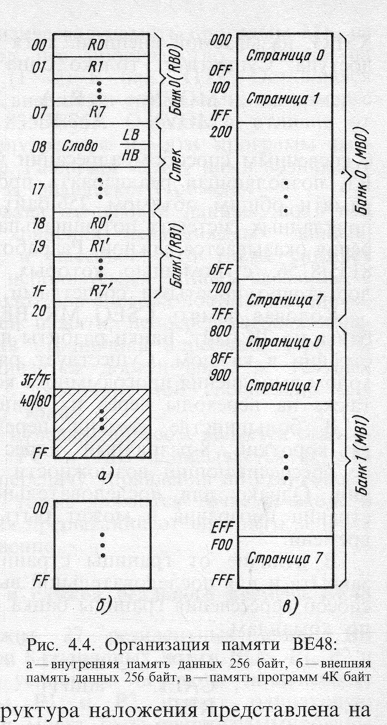

4.4. Организация памяти ве48

Пространство внутренней памяти данных DSEG содержит 256 байт, адресуемых косвенно через два адресных регистра R0, R1 выбранного в данный момент регистрового банка. В архитектуре отсутствует прямой способ адресации памяти, что привело к коротким однобайтовым форматам команд пересылки и обработки, за исключением команд с непосредственными данными.

Физическая оперативная память однокристальных МК, как правило, не покрывает всего пространства внутренней памяти данных из-за нехватки площади кристалла. Так, в приборах ВЕ48 только первые 64 байта покрыты физическим ОЗУ. С усовершенствованием интегральной технологии ожидается увеличение объемов внутреннего физического ОЗУ МК и его постепенное приближение к потенциальному барьеру 256 байт. Например, в однокристальном МК ВЕ49, имеющем такую же базовую архитектуру, что и ВЕ48, объем физического ОЗУ на кристалле увеличен до 128 байт, а в 8050 все пространство в 256 байт покрыто физическим ОЗУ.

Особенностью архитектуры ВЕ48 является совмещение обоих банков рабочих регистров и системного стека с пространством внутренней памяти данных, что дает возможность рассматривать хранящиеся в них объекты с двух сторон. Структура наложения представлена на рис. 4.4. Слова в памяти данных располагаются в двух соседних байтах. В байте с младшим адресом хранится младшая часть слова, его адрес является адресом всего слова. Такая форма хранения слов соответствует типовой и подобна используемой в ВМ80.

Рис. 4.4. Организация памяти BE48:

а—внутренняя память данных 256 байт;

б—внешняя память данных 256 байт; в—память программ 4 К байт

Возможен единственный способ адресации внутренней памяти данных—косвенный регистровый по R0 или R1. Однако часть ячеек все же оказывается доступной с помощью регистрового способа адресации, который может интерпретироваться как короткий прямой.

Совмещение системного стека и банков рабочих регистров с пространством внутренней памяти данных уменьшает и без того небольшой объем физического ОЗУ, свободного для хранения переменных. Этот недостаток частично компенсируется возможностью расширения ОЗУ внешними средствами. Архитектура ВЕ48 предусматривает второй тип пространства памяти данных XSEG, называемой внешней, хотя и с ограниченными ресурсами доступа. Существует только одна команда

MOVX @Ri, A ;XSEG (Ri)A

MOVX A, @Ri ;AXSEG (Ri)

с косвенным способом адресации через адресные регистры R0 и R1, позволяющая реализовать простой обмен с этой областью памяти общим объемом 256 байт. Тем не менее в некоторых прикладных системах потенциальная возможность такого расширения оказывается важной. Разработаны специальные микросхемы 8155/8156, с помощью которых можно получить расширение достаточно простыми средствами.

Кодовая память CSEG MK BE48 содержит два независимых банка по 2К байт. Банки разбиты на 256-байтовые страницы, по 8 страниц в каждом. Существует ряд ограничений на управление ходом выполнения программного кода внутри страниц и банков, а также на переходы через их границы.

В большинстве команд передачи управления используется короткий 8-разрядный адрес внутри текущей страницы, не обеспечивающий возможности перехода через границу страниц. Однако для последовательной выборки команд граница страниц прозрачна и может быть пересечена в любой момент времени.

В отличие от границы страниц граница банков полностью закрыта и для последовательной выборки. Поэтому единственный способ пересечения границы банка состоит в передаче управления по командам

JMP addr11

CALL addr11

RET

RETR

В первых двух командах используется прямой 11-разрядный адрес внутри банка, который загружается в младшие разряды PC. Состояние старшего разряда программного счетчика определяется по флажку выбора банка MB, управляемого отдельными командами:

SEL MB0

SEL МВ1

В командах возврата полный 12-разрядный адрес, включающий разряд адресации банка, выбирается из стека системы. Несмотря на то, что программирование в пространстве программного кода, организованном таким образом, затруднено, результат может оказаться намного эффективнее, чем при работе в обычной однородной среде линейного типа.

Подобно памяти данных физическая память программ МК не покрывает все отводимое под нее пространство. Обычно на кристалле МК располагается (1—2) К байт ПЗУ. Оставшаяся часть может быть реализована внешними средствами, например с помощью специальной БИС 8355/8755. Однако, в отличие от памяти данных, внешняя и внутренняя памяти программ рассматриваются как единое целое. Различия между ними возникают только на уровне структуры и физического обмена.

Память программ изолирована от памяти данных, но в ней предусмотрена возможность хранения неизменяемых данных, например постоянных таблиц и массивов, что также снижает жесткие ограничения на объем используемых данных, связанные с малым объемом ОЗУ. Существуют два способа доступа к данным, расположенным в управляющей памяти: непосредственная адресация и косвенная регистровая страничная адресация через А. В последнем случае обеспечивается доступ либо к текущей странице, либо к странице 3, резервируемой специально для хранения констант различного типа.

Ячейка памяти программ с нулевым адресом является стартовой. При сбросе системы в PC и MB записывается 0, что обеспечивает автоматическую передачу управления по стартовому адресу МК. Адреса 003 и 007 также являются точками входа в память программ обслуживания прерываний от внешнего запроса и таймера/счетчика соответственно.