- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

3.6. Программируемый контроллер прерываний вн59

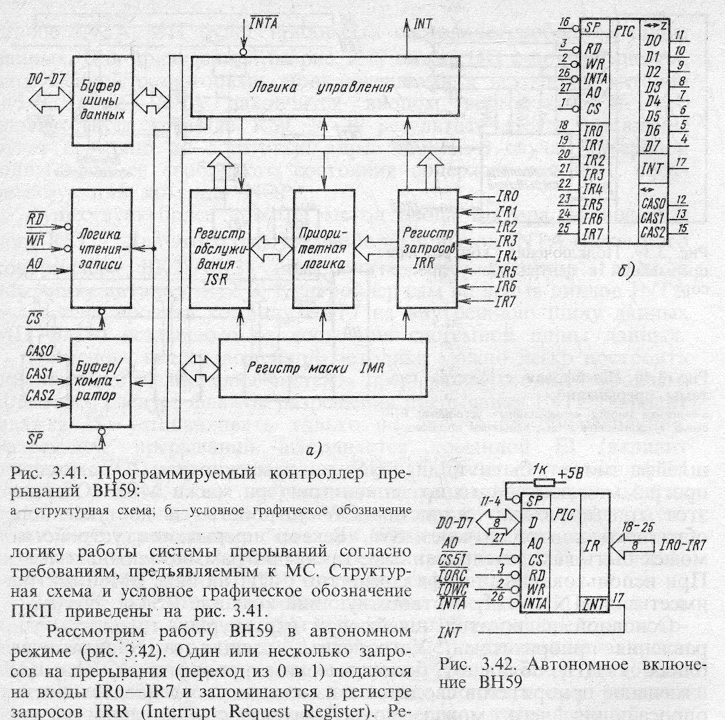

Система векторных прерываний ВМ80/ВМ85А может быть построена различными способами. Наиболее эффективно она реализуется с помощью специальной БИС типа КР580ВН59 (ВН59), называемой программируемым контроллером прерываний (ПКП). Микросхема выполняется по n-МОП-технологии и размещается в 28-выводном корпусе с вертикальным расположением выводов. Она совместима с ТТЛ-схемами. Для работы БИС требуется единственный источник питания +5 В.

На основе ПКП ВН59 формируется 8-уровневая приоритетная система векторных прерываний для МП типов ВМ80/ВМ85А. Несколько контроллеров ВН59 могут соединяться каскадно для расширения числа уровней прерывания до 64. Прибор обеспечивает работу в нескольких режимах, позволяя оптимизировать логику работы системы прерываний согласно требованиям, предъявляемым к МС. Структурная схема и условное графическое обозначение ПКП приведены на рис. 3.41.

Рис. 3.41. Программируемый контроллер прерываний ВН59:

а—структурная схема; б—условное графическое обозначение

Рассмотрим работу ВН59 в автономном режиме (рис. 3.42). Один или несколько запросов на прерывания (переход из 0 в 1) подаются на входы IR0—IR7 и запоминаются в регистре запросов IRR (Interrupt Request Register). Регистр обслуживания ISR (In Service Register) содержит все запросы, которые в данное время находятся в стадии обработки. Регистр маски IMR (Interrupt Mask Register) используется для маскирования отдельных уровней. Запрет некоторого уровня соответствует единице в соответствующем разряде IMR.

Рис. 3.42. Автономное включение ВН59

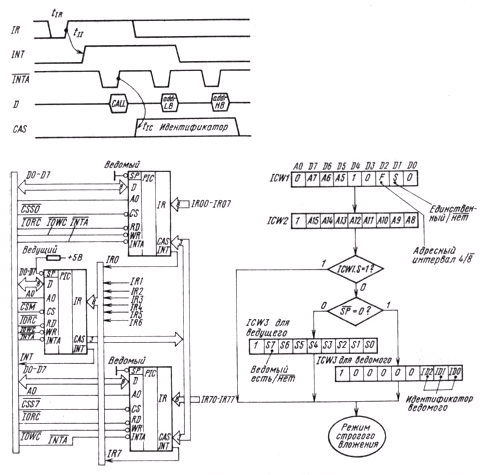

Приоритетная логика выбирает разрешенный запрос на прерывание с наивысшим приоритетом из числа поступивших и сравнивает его с текущим приоритетом запросов, находящихся на обслуживании. При превышении последнего ПКП генерирует сигнал INT (рис. 3.43). Микропроцессор подтверждает прием запроса INT генерацией строба , под воздействием которого запрос с высшим приоритетом из IRR фиксируется в соответствующем разряде ISR. Принятый к обслуживанию IRR-бит сбрасывается и прием нового запроса разрешается. Одновременно с этим ПКП генерирует код команды CALL (0CDH), который принимается МП. В ответ ВМ80/ВМ85А инициирует еще два следующих друг за другом INTA-цикла. Во время этих циклов ПКП передает в МП полный адрес программы обслуживания прерывания, принятого к обработке: сначала младший, а затем старший байт адреса. Установленный в ISR бит остается в состоянии 1 до окончания процедуры обслуживания. В конце процедуры в ПКП должна быть передана специальная команда окончания прерывания EOI, которая сбрасывает соответствующий ISR-бит.

Рис. 3.43. Временные диаграммы работы ВН59

Рис. 3.44. Каскадное включение ВН59 |

Рис. 3.45. Последовательность инициализации ВН59 |

До тех пор, пока некоторый ISR-бит установлен, все запросы с равным или меньшим приоритетом игнорируются. В то же время запросы с более высоким приоритетом приводят к генерации сигнала INT, инициируя вложенные прерывания МП.

Каскадное

соединение нескольких БИС типа ВН59

(рис.

3.44) позволяет

довести число приоритетных уровней до

64. В данном

случае одна БИС действует как ведущая

(![]() = 1), а другие как ведомые (

= 0).

= 1), а другие как ведомые (

= 0).

В каскадном режиме генерация кода команды CALL возлагается на ведущую БИС, а генерация адреса подпрограммы обслуживания—на ведомую. Для этого каждой ведомой БИС присваивается идентификационный код, соответствующий номеру линии запроса на прерывание ведущей БИС, к которой она подключена. Вместо генерации адреса ведущая БИС посылает по трехразрядной шине CAS номер уровня, принятого к обслуживанию, на второй и третий стробы . Этот номер сравнивается компараторами ведомых БИС с присвоенными им идентификаторами, в результате выбирается один из них. Выбранная БИС завершает команду CALL, отвечая на второй и третий стробы генерацией одного из восьми возможных адресов.

Отличительной чертой БИС типа ВН59 является ее программируемость. Программирование осуществляется двумя типами управляющих слов: командами инициализации ICW (Initialization Command Word) и управления OCW (Operation Command Word). Три команды инициализации ICW1—ICW3 загружаются перед началом работы и служат для установки БИС в исходное состояние. Команды управления OCW1—OCW3 могут быть переданы в ПКП в любое время после окончания инициализации. Они предназначены для оперативного управления работой контроллера. При каскадном включении каждая БИС программируется независимо от других.

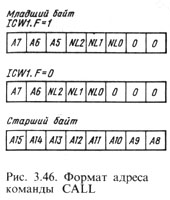

При А0 = 0 и D4 = 1 входной байт интерпретируется как ICW1. При этом очищаются IRR, IMR и осуществляется последовательность действий, приведенная на рис. 3.45. Генерируемые ПКП восемь адресов в команде CALL (по адресу на каждый уровень) равно удалены друг от друга с интервалом либо 4, либо 8 байт, образуя в памяти МС таблицу входов в процедуры обслуживания прерываний размером 32 или 64 байт соответственно. Два первых обязательных слова ICW1 и ICW2 определяют базовый адрес таблицы входов. Адресный интервал таблицы программируется специальным битом F слова ICW1 (ICW1.F). При F = 1 интервал равен 4, в противном случае—8. Адреса команды CALL формируются по схеме

addr = base + k∙NL, k = 4 или 8

и имеют формат, приведенный на рис. 3.46. Здесь через NL обозначен уровень запроса, принятого к обслуживанию. Программируемость базы таблицы входов base предполагает ее размещение в любом месте памяти МС с точностью до границы в 32 или 64 байт. При k = 8 и base = 0 таблица совпадает с системой входов по командам RST n, n = 0—7, микропроцессора ВМ80. При k = 4 и base = 4 обеспечивается совместимость со второй половиной таблицы входов по командам RST n, n = 4—7.5 микропроцессора ВМ85А. Кроме того, поддерживается перемещаемость таблицы входов, что может быть полезно в ряде практических случаев.

Рис. 3.46. Формат адреса команды CALL

В составе ICW1 находится также бит S (Single), определяющий в каком режиме работает система прерываний: автономном (S = 1) или каскадном (S = 0). При работе в автономном режиме процедура инициализации завершается. В каскадном режиме в ПКП должна быть передана еще одна команда ICW3. Формат ICW3 ведущей БИС ( = 1) отличается от формата ICW3 ведомого ( = 0). В первом случае ICW3 сообщает контроллеру о множестве тех уровней, которые задействованы под каскадирование. Эти уровни выделяются установкой в 1 соответствующих разрядов ICW3. Во втором случае ICW3 используется для сообщения ведомой БИС идентификационного номера. Идентификатор должен соответствовать номеру уровня ведущей БИС, к которой подключена ведомая.

После инициализации микросхема готова к работе в режиме строго упорядоченных приоритетов. В данном режиме приоритеты уровней IR0—IR7 располагаются в порядке от 0 (высший) для IR0 до 7 (низший) для IR7. Дальнейшее управление работой схемы осуществляется с помощью OCW1—OCW3, форматы которых приведены на рис. 3.47.

Рис. 3.47. Форматы OCW1—OCW3

Для установки регистра маски IMR применяется слово OCW1. С его помощью каждый уровень может быть замаскирован в произвольный момент времени независимо от других. При установке 1 в некотором разряде IMR запрещается прием прерываний по соответствующему уровню. Регистр маски воздействует и на IRR, и на ISR.

По окончании очередной процедуры обслуживания в контроллер должна быть передана команда EOI, которая сбрасывает ISR-бит с высшим приоритетом. Для этой цели используется OCW2 с кодом R = 0, SL = 0, ЕOI = 1. При работе в каскадном режиме команда EOI выдается дважды: для ведущего и ведомого приборов.

В более общем случае OCW2 служит для установки в 0 произвольных разрядов ISR и циклического сдвига приоритетов с присвоением максимального значения любому из восьми возможных уровней. Если операция установки в 0 кодируется установкой в 1 бита OCW2.EOI, то операция циклического сдвига—бита OCW2.R (Rotate). В зависимости от состояния флажка SL (Special Level) возможны две ситуации: операция установки в 0 и (или) циклического сдвига относится к уровню с высшим в данный момент приоритетом из числа находящихся в обслуживании (SL = 0); одна и (или) обе операции относятся к явно указываемому в OCW2 уровню (SL = 1). В последнем случае номер уровня кодируется в трехразрядном поле L2—L0 (Level). Различные комбинации этих функций и соответствующие им коды приведены на рис. 3.47. На их основе можно построить достаточно мощные и гибкие системы прерываний с разнообразными характеристиками.

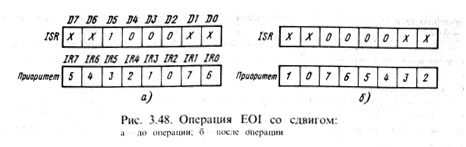

Применение только команды EOI обеспечивает работу в режиме строго упорядоченных приоритетов, когда все запросы имеют фиксированные и строго упорядоченные приоритеты. Для обслуживания запросов с равными приоритетами должна быть использована команда EOI с циклическим сдвигом. При использовании команды сдвига одновременно со сбросом ISR-бита, имеющего высший текущий приоритет, реализуется циклический сдвиг приоритетов с присвоением низшего только что обслуженному уровню. На рис. 3.48 приведен пример циклического сдвига после обработки пятого уровня с приоритетом 3. Следует отметить, что циклический сдвиг не нарушает последовательности вложенных друг в друга прерываний, что обеспечивает правильный возврат из обслуживающих их подпрограмм.

Рис. 3.48. Операция EOI со сдвигом:

а—до операции; б—после операции

В рассмотренных случаях в качестве сбрасываемого в регистре ISR-бита и (или) уровня с низшим приоритетом после циклического сдвига выступал уровень с высшим приоритетом из числа обслуживаемых в данное время, который однозначно определяется состоянием ISR и текущим распределением приоритетов. Прямая адресация уровня обеспечивает: сброс конкретного ISR-бита и, следовательно, завершение процедуры обслуживания соответствующего уровня; циклическое изменение приоритетов с явным указанием нижнего уровня системы приоритетов; сброс адресуемого ISR-бита и присвоение ему низшего приоритета за счет их циклического сдвига. Эти операции позволяют построить системы прерываний с разнообразными (в том числе динамически изменяемыми) структурами приоритетов.

В рассмотренной системе приоритетов находящийся на обслуживании уровень подавляет обработку уровней с меньшим приоритетом даже несмотря на его временное маскирование. Обработку прерываний более низкого уровня можно разрешить сбросом соответствующего ISR-бита, однако этот процесс необратим. Еще одна возможность состоит в установке с помощью OCW3 режима специального маскирования (см. рис. 3.47). В данном режиме каждый бит в регистре ISR запрещает только собственный уровень, но разрешает все остальные. Во время процедуры инициализации режим специального маскирования автоматически аннулируется.

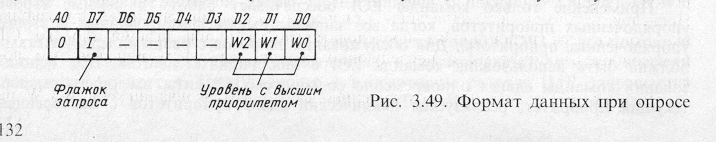

Кроме управления режимом специального маскирования в функции OCW3 входит управление режимом поллинга и выбор регистра IRR или ISR для чтения его содержимого с помощью программ. Режим поллинга (опроса) предполагает ввод информации об источнике прерывания программным методом. Режим инициируется выдачей в ПКП слова OCW3 с установленным битом Р (Polling). Контроллер ВН59 интерпретирует следующий цикл чтения при А0 = 0 как подтверждение прерывания и выдает на шину данных информацию о требующем обслуживания уровне с высшим приоритетом в формате, представленном на рис. 3.49. Если к моменту опроса запросов нет, то возвращается слово с флажком запроса I = 0 в противном случае I = 1, а в поле W2—W0 содержится код уровня с высшим приоритетом. В остальном работа ВН59 аналогична предыдущему случаю. Режим поллинга применяется в случаях, когда существует единая программа обслуживания для нескольких запросов, а также для расширения числа уровней (сверх 64).

Рис. 3.49. Формат данных при опросе

Следует отметить, что ведущие и ведомые контроллеры программируются независимо друг от друга. Поэтому они могут работать в различных режимах, благодаря чему расширяются возможности создания эффективных систем обработки прерываний.

Входящие в состав ВН59 регистры IMR, IRR и ISR доступны для чтения. Регистр маски IMR может быть прочитан в любой момент при А0 = 1 по команде , регистры IRR и ISR при А0 = 0. В каждый момент времени непосредственно доступен только один из регистров. Выбор регистра осуществляется словом OCW3 с помощью ERIS и RIS в соответствии с таблицей на рис. 3.47. После выбора содержимое регистра может считываться произвольное число раз до выбора другого. При приеме ICW1 устанавливается режим чтения содержимого IRR.