- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

3.2. Периферийные бис

Адаптеры и контроллеры периферийных устройств. Под ПУ понимается любое устройство, обменивающееся информацией с МС. Роль физической среды обмена выполняют порты ВВ. Примерами ПУ могут служить клавиатура, индикаторы, счетчики/таймеры, преобразователи информации, исполнительные устройства, цифровые датчики и т. д. Некоторые из этих устройств или их определенные части могут встраиваться в подсистему ВВ и размещаться непосредственно за портами.

Периферийные устройства, встроенные в МС, могут либо представлять законченные автономные средства, например системный таймер или клавишный регистр, либо образовывать дополнительные средства связи с устройствами, расположенными вне МС. В качестве примеров внешних ПУ можно привести дисплеи на электронно-лучевых трубках (ЭЛТ), внешние запоминающие устройства, каналы передачи информации, измерительные приборы и т. д. Связь с устройствами подобного рода осуществляется встроенными в МС промежуточными преобразователями, которые совместно с относящимися к ним портами ВВ получили название периферийных адаптеров и контроллеров. В некоторых наиболее сложных случаях им присвоен статус периферийного сопроцессора.

Унификация интерфейсов внешних ПУ или периферийных интерфейсов привела к созданию ряда стандартных адаптеров и контроллеров. В их функции кроме ВВ входит: формирование периферийного интерфейса; физическое управление внешними ПУ в соответствии с командами ЦП; перенос протокола обмена с ЦП на более высокий уровень интеллектуальности; электрическое согласование сигналов.

Передача функции физического управления ПУ его периферийному адаптеру или контроллеру освобождает ЦП от трудоемких обязанностей низкоуровневого управления устройствами. Функции ЦП сводятся к общему управлению контроллеров ПУ с помощью высокоуровневых команд и слов состояния, что упрощает ПО, уменьшает загрузку ЦП и повышает общую производительность МС [7].

Благодаря успехам электронной промышленности во второй половине 70-х гг. удалось разработать множество однокристальных периферийных адаптеров и контроллеров, а также ряд вспомогательных схем к ним, которые называются периферийными БИС. Приведем далеко не полный набор таких БИС для МС на базе МП ВМ80/ВМ85А:

К589ИР12 Многорежимный буферный регистр

КР580ВВ51/ВВ51А Программируемый связной адаптер

КР580ВИ53, 8254 Программируемый интервальный таймер

КР580ВВ55/ВВ55А Программируемый периферийный адаптер

КР580ВТ57 Контроллер прямого доступа к памяти

КР580ВН59, К1810ВН59А Программируемый контроллер прерываний

КР580ВГ71/ВГ72, К1818ВГ93 Контроллер накопителя на гибких магнитных дисках

8273 Контроллер линии передачи данных

КР580ВГ75 Контроллер ЭЛТ

КР580ВВ79 Контроллер клавиатуры и ЭЛТ

КР580ВК91А, КР580ВА93 Приемопередатчики шины IЕЕЕ-488

8292 Контроллер шины IEEE-488

8041 Универсальный периферийный интерфейс

К1810ВМ89 Сопроцессор ВВ

Этим приборы не только упрощают разработку ПО и повышают производительность МС, но и облегчают проектирование аппаратуры. Заменяя большие объемы аппаратных средств, которые в противном случае пришлось бы разрабатывать на основе малой логики, они повышают компактность и надежность систем. Если первые контроллеры (КР580ВВ51/ВИ53/ВВ55/ВТ57/ВН59) были ориентированы на решение общих прикладных задач, то последующие либо их улучшали (КР580ВВ51А/ВВ55А, К1810ВН59А), либо выполняли более узкие функции (КР580ВГ72/ВГ75/ВВ79/ВК91А и др.).

В любом случае эти устройства решали узкоспециальные задачи, такие как организация параллельного или последовательного интерфейса, распределение интервалов времени или управления ЭЛТ. Однако несмотря на большое число контроллеров и их повышенную гибкость остается еще много нерешенных проблем управления ПУ. Для их решения вводятся универсальные ПУ сопряжения типа 8041 фирмы Intel [59], которые представляют собой однокристальные микроЭВМ с системным интерфейсом подчиненного типа (см. § 4.9). Еще большую общность предоставляют сопроцессоры ВВ [58], например К1810ВМ89.

Стандартная шина для периферийных БИС. Периферийные БИС серии КР580 удовлетворяют электрическим и логическим спецификациям на микропроцессорную шину Microbus фирмы National Semiconductor (США)—унифицированную 8-разрядную шину, объединяющую в функционально законченный модуль отдельные компоненты, размещенные в непосредственной близости друг от друга. В 1978 г. она была признана стандартным интерфейсом периферийных БИС (стандарт Р696-3 IEEE), обеспечивающим совместимость уже существующих микропроцессорных кристаллов с вновь разработанными [42].

Основная задача проектирования систем на базе МП и микропроцессорных БИС состоит в выборе внутрисистемной магистрали и сопряжении с ней приборов. Функциональные требования, накладываемые на внутрисистемную магистраль, рассмотрены в § 1.3. Они были сформулированы исходя из возможностей физических интерфейсов МП и ЦП на их основе. Другие требования предъявляются к интерфейсам периферийных БИС, призванным расширить функциональные возможности МС на аппаратном уровне. Попытка унифицировать эти требования привела к разработке ряда стандартных внутренних интерфейсов периферийных БИС, в числе которых шина Microbus. В случае простейших МС, состоящих из нескольких кристаллов, она может интерпретироваться как системная.

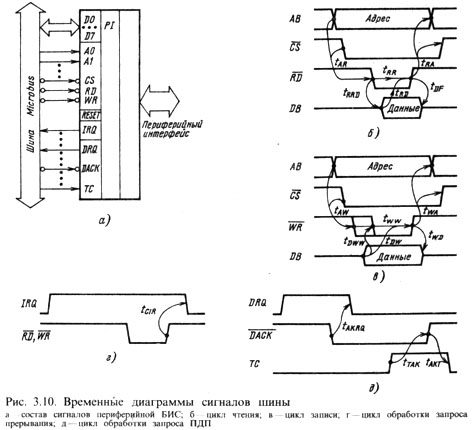

Двунаправленная трехстабильная шина данных D7—D0 (Data Bus) используется для ВВ данных, информации о состоянии и управляющих слов, организованных в 8-разрядные наборы (рис. 3.10). В простейших случаях эти линии могут быть однонаправленными.

Рис. 3.10. Временные диаграммы сигналов шины

а—состав сигналов периферийных БИС; б—цикл чтения; в—цикл записи;

г—цикл обработки запроса прерывания; д—цикл обработки запроса ПДП

Наличие

напряжения низкого уровня на линии

выбора кристалла

![]() (Chip

Select)

показывает,

что производится обращение к данному

прибору. Сигнал

должен действовать в сочетании с другими

сигналами, такими как строб чтения

или записи

.

Так, при напряжении низкого уровня на

входной линии

RD (Read)

разрешает прибору выдачу информации

на шину D7—D0

при условии, что он выбран (

= 0). Необходимо, чтобы на срезе строба

на линиях шины D7—D0

находились действительные данные. В

случае невыполнения условия

= 0 передатчики шины данных прибора

должны находиться в высокоомном

состоянии. Аналогично низкий уровень

напряжения на входном контакте

(Write)

в совокупности с низким уровнем на входе

дает возможность БИС принять данные из

шины

D7—D0.

Для приборов первого поколения информация

на шине данных D7—D0

должна быть истинной во время действия

сигнала записи

.

БИС второго поколения требуют ее

истинности только на срезе сигнала

записи.

(Chip

Select)

показывает,

что производится обращение к данному

прибору. Сигнал

должен действовать в сочетании с другими

сигналами, такими как строб чтения

или записи

.

Так, при напряжении низкого уровня на

входной линии

RD (Read)

разрешает прибору выдачу информации

на шину D7—D0

при условии, что он выбран (

= 0). Необходимо, чтобы на срезе строба

на линиях шины D7—D0

находились действительные данные. В

случае невыполнения условия

= 0 передатчики шины данных прибора

должны находиться в высокоомном

состоянии. Аналогично низкий уровень

напряжения на входном контакте

(Write)

в совокупности с низким уровнем на входе

дает возможность БИС принять данные из

шины

D7—D0.

Для приборов первого поколения информация

на шине данных D7—D0

должна быть истинной во время действия

сигнала записи

.

БИС второго поколения требуют ее

истинности только на срезе сигнала

записи.

Во многих МС предполагается использование раздельных стробов чтения-записи при обращении к памяти— , и к портам BB— , (изолированный ВВ). В тех случаях, когда БИС содержит и память, и порты ВВ, должны быть предусмотрены обе пары стробов чтения-записи.

Сигналы адресной шины А15—А0 применяются для адресации внутренних регистров БИС сопряжения. Сигналы адреса, поступающие на интерфейс, выбирают один из его внутренних регистров или ячеек памяти и в сочетании с входными сигналами , или определяют тип выполняемого обмена: ВВ данных, ввод управляющей информации или вывод состояния БИС.

Выходной сигнал готовности к обмену READY предназначен для реализации асинхронного обмена по шине Microbus. Стробы и будут сняты только после появления активного уровня на линии READY, что гарантирует успешный обмен данными с медленно действующими интерфейсными БИС. В приборах с быстрым доступом ответный сигнал READY может отсутствовать.

Сигнал

сброса

![]() (допускается вариант прямого сигнала

RESET)

выдается МП при включении источника

питания или нажатии кнопки сброса. При

получении данного сигнала интерфейсная

БИС устанавливается в исходное состояние,

при этом шина данных БИС должна быть

отключена от системной шины Microbus.

(допускается вариант прямого сигнала

RESET)

выдается МП при включении источника

питания или нажатии кнопки сброса. При

получении данного сигнала интерфейсная

БИС устанавливается в исходное состояние,

при этом шина данных БИС должна быть

отключена от системной шины Microbus.

Перекрестные устройства часто выдают в систему запросы на прерывание IRQ0, IRQ1,…, которые служат признаками программно не предсказуемых событий. Сигнал прерывания IRQ, после того как он выработан асинхронно по отношению к другим сигналам шины, должен оставаться в активном состоянии до тех пор, пока не будет обработан. Он снимается только по срезу соответствующего строба или .

Для

МС с ПДП в шине Microbus

предусмотрены один обычный DRQ

(Direct

Request)

и два специальных сигнала:

![]() (Direct

Acknowledge)

и ТС (Terminal

Count).

Каждый ПДП-канал формирует свой

собственный сигнал запроса DRQ0,

DRQ1,…,

на который МС реагирует выдачей

специального сигнала подтверждения

(квитанции)

.

Этот сигнал должен быть эквивалентным

сигналу выборки кристалла и иметь такие

же временные характеристики. При этом

в канале ПДП одновременно выполняются

операции чтения и записи. Еще один

специальный сигнал ТС выдается

контроллером ПДП-каналу как указание

о том, что настоящий цикл обмена является

последним циклом для текущего блока

данных.

(Direct

Acknowledge)

и ТС (Terminal

Count).

Каждый ПДП-канал формирует свой

собственный сигнал запроса DRQ0,

DRQ1,…,

на который МС реагирует выдачей

специального сигнала подтверждения

(квитанции)

.

Этот сигнал должен быть эквивалентным

сигналу выборки кристалла и иметь такие

же временные характеристики. При этом

в канале ПДП одновременно выполняются

операции чтения и записи. Еще один

специальный сигнал ТС выдается

контроллером ПДП-каналу как указание

о том, что настоящий цикл обмена является

последним циклом для текущего блока

данных.

Микросистемы, построенные с расчетом на универсальную 8-разрядную шину Microbus, обеспечиваются средствами прямого сопряжения с большинством выпускаемых сегодня периферийных БИС, ориентированных на стандарт шины Microbus. Благодаря этому возможна дальнейшая модификация МС, что очень важно для сложных МПК.

Вариантами, альтернативными интерфейсу Microbus, являются двухшинные интерфейсы внутриплатного уровня. Сюда прежде всего следует отнести двухшинную магистраль ВМ85А, обеспечивающую прямое подключение периферийных БИС и МП ВМ85А. Вторым широко распространенным в отечественной практике стандартом на внутрисистемную магистраль периферийных БИС является МПИ-шина (аналог Q-bus). Стандарт предназначен для МПК БИС серий К1801, К1809, К581, К588 и др.

Приведенная

на рис.

2.17 схема

5-кристального ЦП не обеспечивает МС

полным набором сигналов шины Microbus.

Отсутствуют такие важные для системы

линии, как

![]() ,

,

![]() ,…—линии

выбора кристалла, IRQ0,

IRQ1,…—линии

запросов на прерывание, а также набор

сигналов ПДП.

,…—линии

выбора кристалла, IRQ0,

IRQ1,…—линии

запросов на прерывание, а также набор

сигналов ПДП.

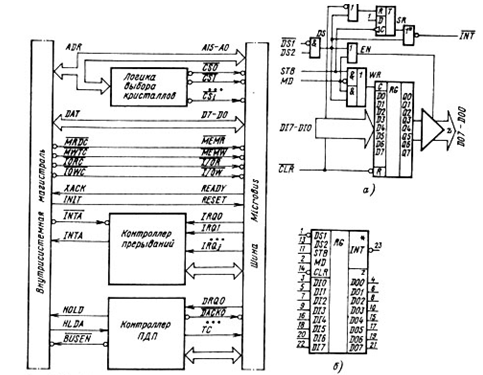

Сигналы обычно формируются из комбинации старших разрядов адресной шины ADR15—ADR0 логикой выбора кристалла, которая представляет собой комбинационный дешифратор и легко реализуется с помощью ПЗУ, ПЛМ [13, 50] или логических схем малой степени интеграции. Для получения оставшихся сигналов шины Microbus необходимо в МС ввести контроллер обработки прерываний и контроллер ПДП (рис. 3.11), реализуемые с помощью специальных БИС типов КР580ВН59 и КР580ВТ57 соответственно [1].

Рис. 3.11. Схема контроллера шины Microbus |

Рис. 3.12. Многорежимный буферный регистр ИР12: а—структурная схема; б—условное графическое обозначение |