- •Глава 1.

- •1 .1. Понятия организации и архитектуры

- •1.2. Архитектура типовой микросистемы

- •1.3. Структура типовой микросистемы

- •1.4. Регистры микропроцессора

- •1.5. Адресация данных

- •Глава 2.

- •2 .1. Вводные замечания

- •2.2. Архитектура вм80

- •2.3. Система команд вм80

- •2.4. Структурная схема вм80

- •2.5. Базовый комплект бис серии кр580

- •2.6. Центральный процессор на базе бис серии кр580

- •2.7. Организация вм85а

- •Глава 3.

- •3.1. Организация программно-управляемого обмена

- •3.2. Периферийные бис

- •3.3. Средства параллельного ввода-вывода

- •3.4. Средства последовательного ввода-вывода

- •3.5. Система прерываний

- •3.6. Программируемый контроллер прерываний вн59

- •3.7. Средства счета времени

- •Глава 4.

- •4 .1. Вводные замечания

- •4.2. Базовая организация ве48

- •4.3. Набор регистров ве48

- •4.4. Организация памяти ве48

- •4.5. Система ввода-вывода и служба реального времени ве48

- •4.6. Система команд ве48

- •4.7. Физический интерфейс ве48

- •4.8. Расширение внутренних ресурсов ве48

- •4.9. Универсальный периферийный адаптер

- •4.10. Базовая организация ве51

- •4.11. Периферийные средства ве51

- •4.12. Система команд ве51

- •4.13. Функциональное описание ве51

- •Глава 5.

- •5 .1. Одноплатный микроконтроллер мМс1204

- •5.2. Средства ввода-вывода и поддержки режима реального времени

- •5.3. Программирование системы ввода-вывода

- •5.4. Программирование средств поддержки режима реального времени

- •Глава 6.

- •6 .1. Вводные замечания

- •6.2. Организация регистров вм86

- •6.3. Организация памяти вм86

- •6.4. Формат команд вм86

- •6.5. Система команд вм86

- •6.6. Структурная схема вм86

- •6.7. Структурные отличия вм88

- •Глава 7.

- •7 .1. Принцип построения

- •7.2. Генератор тактовых импульсов гф84

- •7.3. Системный контроллер вг88

- •7.4. Центральный процессор на базе бис серии к1810

- •7.5. Программируемый контроллер прерываний вн59а

- •7.6. Одноплатный микроконтроллер мМс1212

- •Глава 1. Организация микросистем ……………………………………………………………………………………..

- •Глава 2. Микропроцессоры кр580вм80/к1821вм85а ………………………………………………………………

- •Глава 3. Подсистема ввода-вывода ………………………………………………………………………………………

- •Глава 4. Организация однокристальных микроконтроллеров ……………………………………………………..

- •Глава 5. Организация одноплатных микроконтроллеров на базе кр580вм80 ………………………………

- •Глава 6. Микропроцессор к1810вм86 …………………………………………………………………………………

- •Глава 7. Организация одноплатных микроконтроллеров на базе к1810вм86 ………………………………

Глава 3.

П ОДСИСТЕМА ВВОДА-ВЫВОДА

3.1. Организация программно-управляемого обмена

Пространство ввода-вывода. Подсистема ВВ—один из трех компонентов МС, ответственный за связь с периферийными устройствами (ПУ), а в некоторых случаях и за организацию самих ПУ [З].

С точки зрения программиста, работающего на командном уровне, систему ВВ можно представить в виде пространства ВВ IOSEG и ряда команд ВВ, имеющих к нему доступ [11]. Пространство IOSEG обычно организовано в виде набора n-разрядных ячеек—портов, каждый из которых может быть адресован независимо от других. Типичная разрядность порта для большинства МС равна восьми. В некоторых системах допускается объединение двух и более элементарных портов в многобайтовые, доступ к которым реализуется как к единому целому. Так, в МС на базе МП К1810ВМ86 допускаются и 8-, и 16-разрядные порты.

Подобно пространству памяти пространство ВВ, как правило, линейно упорядочено. Каждому элементарному порту поставлен в соответствие его адрес. Множество адресов занимает целочисленный диапазон от 0 до 2P – 1. Правила организации и адресации многобайтовых портов могут соответствовать аналогичным правилам размещения и адресации многобайтовых объектов в памяти МС.

В качестве примера приведем систему ВВ для МС на базе МП ВМ80. Пространство IOSEG такой системы организовано в виде 256 8-разрядных портов ВВ с линейно упорядоченными адресами от 0 до 28 – 1. В распоряжение пользователя предоставляются две команды ВВ, содержащиеся в системе команд:

IN port ;Aport

OUT port ;portA

Архитектура ВМ85А позволяет расширить данное пространство ВВ. К нему добавляется изолированный одноразрядный порт ввода SID и изолированный одноразрядный порт вывода SOD, доступ к которым осуществляется с помощью команд

RIM ;A7SID

SIM ;SODA7

Здесь А7—старший разряд аккумулятора А (см. § 2.7). Далее рассматриваются другие организации подсистемы ВВ.

Программно-управляемый обмен. Между МС и ПУ происходит обмен информацией двух типов: служебной и собственно данных. Служебная информация от МС инициирует действия, связанные с обменом данных, и передается с помощью управляющих слов CW (Control Word). Служебные сообщения от ПУ, информирующие систему о его текущем состоянии, называются словами состояния SW (Status Word). В отличие от них данные передаются с помощью слов данных DW (Data Word) [3, 10].

Объем служебной информации, которой обмениваются ПУ и МС, а также ее интерпретация зависят от типа ПУ. Для наиболее простых устройств, таких как прямо управляемые клавишные матрицы или светодиодные линейки, служебная информация не нужна. В других случаях, например при взаимодействии с накопителем на гибких магнитных дисках, управляющая информация и данные о состоянии ПУ могут иметь значительный объем. В любом случае для связи с ПУ отводится ряд портов ВВ, через которые и проходит вся информация: сигналы управления, слова состояния или непосредственно данные. С точки зрения программиста множество портов ВВ образует пространство доступа к ПУ.

Отметим, что размер пространства доступа в общем случае не зависит от объема информации, которой обмениваются ПУ и МС. Распространена практика последовательной передачи массива информации через один и тот же порт. Это связано не только с экономией пространства IOSEG, но и с минимизацией ширины физического интерфейса ПУ, а также с его стандартизацией. Вместе с тем существует некоторая договоренность или правила обмена информацией между конкретным ПУ и МС, называемые протоколом обмена. Совокупность этих правил—основа для составления драйвера ПУ, представляющего набор подпрограмм, организующих взаимодействие с ним.

В тех случаях, когда процедуры обмена информацией с ПУ инициируются и выполняются непосредственно программой, реализуемой ЦП, говорят о программно-управляемом обмене. Программно-управляемый обмен не является единственным типом обмена. Но судя по аппаратным затратам, это наиболее эффективный тип обмена, поэтому он находит самое широкое применение в разнообразных МС.

Прямой ввод-вывод. В наиболее простом виде процедура ввода или вывода выполняется независимо от состояния ПУ. Такой вид обмена назван прямым или безусловным. Процедуры прямого ВВ в чистом виде возможны только при управлении всегда готовыми к обмену простейшими ПУ. К тому же они являются составными элементами более сложных процедур программно-управляемого обмена, к числу которых относится условный ВВ.

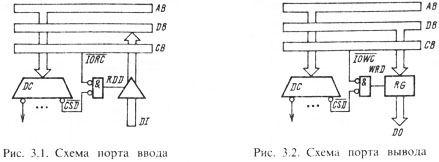

Простейшая процедура ввода информации из подсистемы ВВ связана с чтением отдельного порта пространства IOSEG. С этой целью физические линии подсистемы ВВ упаковываются в байтовые и многобайтовые наборы, состояние каждого из которых может быть передано на шину данных МС во время цикла чтения порта ВВ. Физическое управление вводом состояния конкретного набора лучше всего осуществлять с помощью шинного формирователя с тремя состояниями (рис. 3.1), открываемого стробом при условии его выбора. Выбор или адресация формирователей возлагается на специальную декодирующую схему, называемую логикой выборки кристаллов, которая, в свою очередь, управляется сигналами шины адреса и при необходимости шины управления, ответственными за кодирование размера передаваемых данных: байта, слова, двойного слова.

Рис. 3.1. Схема порта ввода |

Рис. 3.2. Схема порта вывода |

Запись

данных в порт соответствует их выводу

в подсистему ВВ. В простейшем варианте

порта вывода (рис.

3.2) данные

фиксируются в регистре по стробу

или

![]() при условии его выбора. Роль адресации

регистра выполняет логика выборки

кристаллов. При использовании строба

данные могут фиксироваться его низким

уровнем напряжения, при стробе

они должны восприниматься только по

его фронту.

при условии его выбора. Роль адресации

регистра выполняет логика выборки

кристаллов. При использовании строба

данные могут фиксироваться его низким

уровнем напряжения, при стробе

они должны восприниматься только по

его фронту.

Примерами процедур прямого ввода служат следующие подрограммы:

IXHL: PUSH PSW

IN CSD ;Ввод данных из порта CSD

MOV M, A ;Запись данных по адресу HL

POP PSW

RET

IAC: MOV A, C ;Пересылка адреса порта

STA IAC + 5 ;Модификация команды IN 0

IN 0 ;Ввод данных

RET

Процедуры для прямого вывода аналогичны:

OXHL: PUSH PSW

MOV A, M ;Чтение данных по адресу HL

OUT CSD ;Вывод данных

POP PSW

RET

OAC: PUSH PSW

MOV A, C ;Пересылка адреса порта

STA OAC + 7 ;Модификация команды OUT 0

POP PSW ;Восстановление данных

OUT 0 ;Вывод данных

RET

Быстродействия шинных формирователей и регистровых схем обычно достаточно, чтобы поддержать обмен с максимальной для ЦП скоростью (синхронный режим работы системной магистрали). Поэтому подтверждение обмена сводится к как можно более быстрому возврату сигнала подтверждения XACK, образуемому стробами , или по схеме

XACK = IORC∙CSD IOWC∙CSD …

В системах с инверсным сигналом ХАСК частные сигналы подтверждения обмена формируются буферами с открытым коллектором и объединяются по принципу «монтажное ИЛИ». В малых МС с активной по умолчанию линией подтверждения ХАСК не требуется логика подтверждения (см. рис. 3.1, 3.2). Это может быть использовано для упрощения подсистемы ВВ.

Отметим, что в отличие от памяти данные, выводимые и вводимые через порты с одним и тем же адресом, в общем случае никак не связаны между собой. Вместе с тем прямое соединение выходных DO и входных DI линий портов ВВ дает возможность чтения выведенных ранее данных, что может быть полезным в ряде практических случаев, например при тестировании порта вывода или восстановлении его текущего состояния. Однако ввод внешних данных через такой порт невозможен.

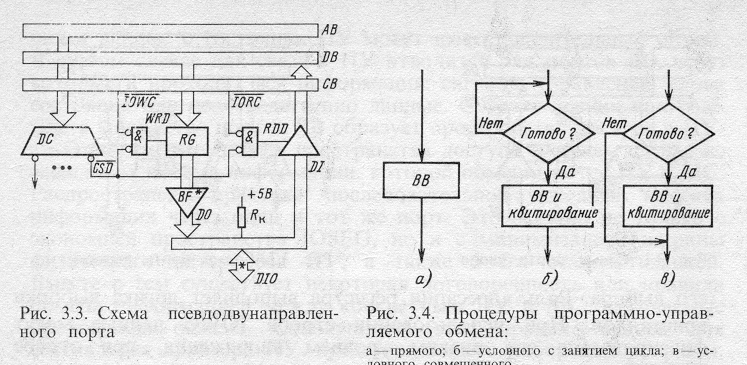

Для поддержки двустороннего ВВ очень широко применяется псевдодвунаправленный порт (рис. 3.3). В данной схеме к выходам DO подключены буферы с открытым коллектором, допускающие объединение с линиями ввода внешних данных по схеме «монтажное ИЛИ». При этом нагрузочные резисторы могут быть встроены в порт. Установка на шине порта вывода напряжения высокого уровня обеспечивает ввод внешних данных без каких-либо искажений. При необходимости некоторые линии ввода могут быть выборочно замаскированы установлением на соответствующих им линиях DO напряжения низкого уровня. Допускается в качестве входных линий использовать лишь часть порта, тогда как оставшаяся часть может выполнять роль выходной шины. В целом схема, приведенная на рис. 3.3, достаточно универсальна, что объясняет ее широкое распространение, например, в однокристальных микроЭВМ.

Рис. 3.3. Схема псевдодвунаправленного порта |

Рис. 3.4. Процедуры программно-управляемого обмена: а—прямого; б—условного с занятием цикла; в—условного совмещенного |

Условный ввод-вывод. Способность ПУ к скоростному ВВ данных не безгранична и, как правило, во много раз ниже скорости работы ЦП. Поэтому прежде чем приступить к чтению новых данных из порта ввода, необходимо удостовериться, что ПУ готово предоставить или уже предоставило эти данные. Иначе операция сведется к вводу недействительных или старых данных. Аналогичная ситуация складывается и при выводе данных, когда требуется проверка готовности ПУ к приему новых данных. В противном случае неразрешенный вывод со стороны ЦП может привести к потере нового или предыдущего элемента данных.

Типичное решение проблемы синхронизации обмена состоит в сопровождении операции условного ВВ специальным сигналом готовности RDY (Ready), генерируемым ПУ. Сигнал вводится в МС в составе слова состояния SW и служит для информирования ЦП о готовности ПУ принять или передать новые данные.

Наряду с прямым (рис. 3.4, а) существуют два типа условного ВВ: с занятием цикла (рис. 3.4, б) и совмещенный (рис. 3.4, в). В первом случае МС зависает на цикле ожидания готовности, тратя на это все машинное время. Во втором случае, если ПУ не готово к обмену, ЦП возвращается к основной задаче без выполнения операции ВВ. Однако он может снова проверить готовность ПУ к обмену и при удачном исходе выполнить ее.

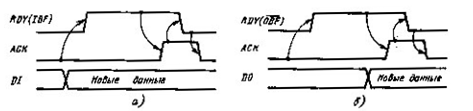

После завершения операции ВВ сигнал готовности RDY должен быть снят и выставлен заново только при новой готовности к обмену. С этой целью ПУ следует проинформировать об окончании операции, для чего используется включенный в одно из управляющих слов CW сигнал подтверждения АСК (Acknowledgement). Протокол обмена служебной информацией такого типа (рис. 3.5) называется квитированием. Он обеспечивает надежную асинхронную передачу данных со скоростями, определяемыми ПУ.

Рис. 3.5. Временные диаграммы условного обмена:

а—ввод; б—вывод

Приведем пример процедуры условного ВВ с занятием цикла и программно-управляемым квитированием (см. рис. 3.4, б):

PUSH PSW

WAIT1: IN CSSC ;Ввод слова состояния

ANI RDY ;Выделение сигнала RDY

JZ WAIT1 ;Если RDY = 0, то ждать

POP PSW

;Процедура прямого ВВ

PUSH PSW

MVI А, АСК ;Вывод сигнала

OUT CSSC ;подтверждения АСК

WAIT2: IN CSSC ;Выделение сигнала RDY

JNZ WAIT2 ;Если RDY = 1, то ждать

MVI A, NACK ;Сброс сигнала

OUT CSSC ;подтверждения АСК

POP PSW

RET

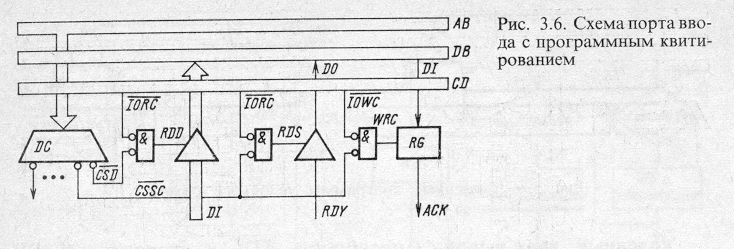

В сравнении с прямым условный ВВ с программным квитированием связан с увеличением аппаратных затрат (рис. 3.6). Однако это наиболее типичный вид обмена с ПУ. Он распространен в системах, где эффективность не связана с ожиданиями. При этом вариант совмещенного условного обмена обеспечивает оперативное отслеживание внешних событий и своевременную реакцию на их возникновение.

Рис. 3.6. Схема порта ввода с программным квитированием

Признаком окончания операции может служить само обращение к порту данных. Это упрощает как схему порта, так и процедуру обмена, освобождая пользователя от работы с управляющим словом.

Очень часто на входе порта ввода (рис. 3.7, а) предусматривается регистр-защелка, фиксирующий входные данные по стробу STB (Strobe), генерируемому ПУ. Устанавливает флажок готовности IBF (Input Buffer Full), инициируя операцию ввода (рис. 3.7, б). Флажок сбрасывается автоматически при чтении содержимого порта ввода. Необходимо обратить внимание на логику формирования флажка готовности, который переключается только после завершения операции зашелкивания во входной регистр или считывания из него данных. Что произойдет, если это условие не будет выполнено?

Рис. 3.7. Порт условного ввода: а—структурная схема; б—временные диаграммы |

Рис. 3.8. Порт условного вывода: а—структурная схема; б—временные диаграммы |

Введение

логики формирования флажка готовности

в состав входного порта освободило ПУ

от необходимости прямого управления

им, придало процедуре обращения к порту

с обеих сторон

симметричный вид. Применение этой

методики к выходному порту приводит к

схеме на рис.

3.8, а, в

которой роль флажка готовности выполняет

флажок

![]() (Output

Buffer

Full),

сигналом окончания операции вывода и

установки флажка

OBF служит

сигнал АСК, генерируемый ПУ. Процедуры

условного ВВ упростились. Например, для

условного ВВ с занятием цикла имеем

(Output

Buffer

Full),

сигналом окончания операции вывода и

установки флажка

OBF служит

сигнал АСК, генерируемый ПУ. Процедуры

условного ВВ упростились. Например, для

условного ВВ с занятием цикла имеем

IA: IN CSS ;Ввод слова состояния

ANI IBF ;Выделение флажка IBF

JZ IA ;Если IBF = 0, то ждать

IN CSD ;Иначе—ввод данных

RET

ОА: PUSH PSW

WAIT: IN CSS ;Ввод слова состояния

ANI NOBF ;Выделение флажка

JZ WAIT ;Если = 0, то ждать

POP PSW

OUT CSD ;Иначе—вывод данных

RET

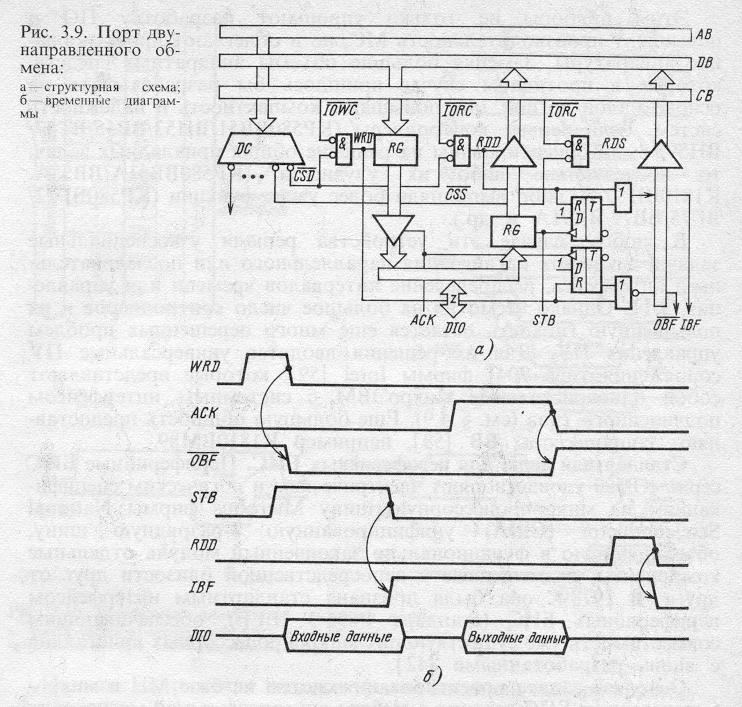

При необходимости на выходе порта вывода может быть предусмотрен трехстабильный буфер, открываемый сигналом АСК. Это важно, например, при организации двунаправленного порта (рис. 3.9). Состояние входного и выходного регистров порта отображается флажками готовности IBF и OBF соответственно. Одновременная активизация линий АСК и STB реализует выходной порт с обратной связью.

Рис. 3.9. Порт двунаправленного обмена:

а—структурная схема; б—временные диаграммы

Рассмотренные выше порты являются простейшими схемными элементами, на основе которых реализуется связь с ПУ. Они образуют первый, наиболее близкий к МС уровень аппаратных средств подсистемы ВВ. В ряде случаев этот уровень единственный.