- •Предисловие

- •I. Электронные ключи

- •Глава 1. Электронный ключ на биполярном транзисторе

- •1.1. Статические свойства ключа

- •1.1.1. Режим отсечки

- •1.1.2. Режим насыщения

- •1.2. Динамические свойства ключа

- •1.2.1. Время задержки

- •1.2.2. Время положительного фронта

- •1.2.3. Накопление носителей

- •1.2.4. Время рассасывания

- •1.2.5. Время среза

- •Глава 2. Повышение быстродействия ключей на биполярных транзисторах

- •2.1. Переключатели тока на биполярных транзисторах

- •Глава 3. Ключи на полевых транзисторах

- •Часть вторая исследование ключа на транзисторе

- •1. Цель работы

- •2. Описание лабораторной установки

- •3. Методические указания

- •4. Предварительное расчётное задание

- •5. Рабочее задание

- •5.1. Исследовать ключевую схему на биполярном транзисторе

- •II. Простейшие комбинационные

- •Интегральные микросхемы

- •Часть первая

- •Логические интегральные схемы

- •Глава 1. Основные параметры логических схем

- •1.1. Транзисторно-транзисторная логика

- •1.2. Эмиттерно-связанная логика

- •Часть вторая исследование интегральных логических элементов

- •1. Цель работы

- •2. Описание лабораторной установки

- •3. Методические указания

- •4. Предварительное расчётное задание

- •5. Рабочее задание

- •5.1. Исследование ключевых схем на интегральных логических элементах (илэ) (по выбору преподавателя).

- •6. Контрольные вопросы

- •Глава 1. Триггеры на интегральных микросхемах

- •1.1. Общие сведения и классификация

- •1.2. Триггеры rs-типа

- •1.3. Триггеры d-типа

- •1.4. Триггеры, управляемые перепадом синхроимпульса

- •1.5. Триггеры т-типа

- •Глава 2. Регистры

- •Глава 3. Счётчики импульсов

- •Часть вторая исследование схемы универсального регистра

- •1. Цель работы

- •2. Описание лабораторной установки

- •3. Предварительное расчётное задание

- •4. Рабочее задание

- •5. Контрольные вопросы

- •3. Предварительное расчётное задание

- •4. Рабочее задание

- •5. Контрольные вопросы

- •Регистра интегральные счётчики в программной среде ewb

- •IV. Генераторы прямоугольных импульсов

- •Глава 1. Общие сведения о работе генераторов

- •1.1. Мультивибратор на биполярных транзисторах

- •Мультивибратора

- •1.2. Интегральный аналог дискретного mb

- •Примером такой практической реализации являются выпускаемые интегральные мв на микросхемах 119гг1,2 серий 119 (1гф192а - 1гф192в, к1гф192) и 218 (2гф181, к2гф181).

- •1.3. Мультивибраторы на илэ

- •1.3.1. Мультивибраторы симметричного вида

- •1.3.2. Мультивибраторы несимметричного вида

- •1.4. Мультивибратор на операционном усилителе

- •1.5. Ждущие мультивибраторы

- •1.6. Таймеры

- •Часть вторая исследование схем мультивибраторов

- •1. Цель работы

- •2. Описание лабораторной установки

- •3. Предварительное расчётное задание

- •4. Рабочее задание

- •Мультивибраторы в программной среде ewb

- •Глава 1. Укоротители импульсов на илэ

- •Глава 2. Расширители импульсов на илэ

- •2. Описание лабораторной установки

- •3. Предварительное расчётное задание

- •4. Рабочее задание

- •5. Контрольные вопросы

- •VI. Генераторы линейно изменяющегося

- •Глава 1. Разновидности генераторов линейно изменяющегося сигнала

- •1.1. Глин с токостабилизирующим элементом

- •1.2. Глин с компенсирующей эдс

- •1.3. Глин на операционном усилителе

- •1.4. Автогенератор с компаратором

- •Часть вторая исследование параметров схем глиНов

- •1. Цель работы

- •2. Описание лабораторной установки

- •3. Предварительное расчётное задание

- •4. Рабочее задание

- •Часть третья генераторы линейно изменяющегося напряжения в программной среде ewb

- •Библиографический список

5. Контрольные вопросы

1. Нарисовать временные диаграммы и пояснить работу асинхронного суммирующего и вычитающего счётчиков.

3. Пояснить работу синхронного счётчика с последовательным переносом.

4. Как определить, каким перепадом, положительным (фронтом) или отрицательным (срезом) входного сигнала, тактируются триггеры счётчика?

5. Пояснить влияние обратных связей с схемах счетчиков.

6. От чего зависит максимальная частота счета в счётчиках. Каким образом можно увеличить быстродействие счетчика?

7. Пояснить способы организации работы счётчика с произвольным коэффициентом счёта КСЧ.

8. Пояснить работу реверсивного счётчика и способы организации переноса в многоразрядных счётчиках.

9. Пояснить работу делителя частоты, управляемого кодом.

10. Какая особенность построения схемы счётчика на отдельных триггерах и БИС-счётчика?

11. Пояснить преимущества схемы счетчика на БИС по сравнению с счетчиком, собранных на отдельных триггерах.

Часть третья

ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ В ПРОГРАММНОЙ СРЕДЕ EWB

Т риггерные

схемы в программной среде EWB

представлены в библиотеке тремя типами

триггеров RS,

JK

и D,

показанных на рис. 3.32. Назначение выводов

следующее. Для всех схем выводы Q

– прямой,

риггерные

схемы в программной среде EWB

представлены в библиотеке тремя типами

триггеров RS,

JK

и D,

показанных на рис. 3.32. Назначение выводов

следующее. Для всех схем выводы Q

– прямой,

![]() – инверсный, информационными являются

входы R,

S,

J,

K

и D.

Для JK

и D

триггеров входы R

и S

являются входами предварительной

(асинхронной) установки и сброса. Тактовые

входы (входы синхронизации) обозначены

значком ”>”. Кружочком обозначена

инверсия соответствующих входных

сигналов, то есть активный уровень этих

сигналов – низкий. Кружочек рядом с

тактовым входом означает, что переключение

триггера происходит не по переднему

фронту тактового импульса, а по его

срезу, то есть по заднему фронту (срезу),

рис. 3.32.

– инверсный, информационными являются

входы R,

S,

J,

K

и D.

Для JK

и D

триггеров входы R

и S

являются входами предварительной

(асинхронной) установки и сброса. Тактовые

входы (входы синхронизации) обозначены

значком ”>”. Кружочком обозначена

инверсия соответствующих входных

сигналов, то есть активный уровень этих

сигналов – низкий. Кружочек рядом с

тактовым входом означает, что переключение

триггера происходит не по переднему

фронту тактового импульса, а по его

срезу, то есть по заднему фронту (срезу),

рис. 3.32.

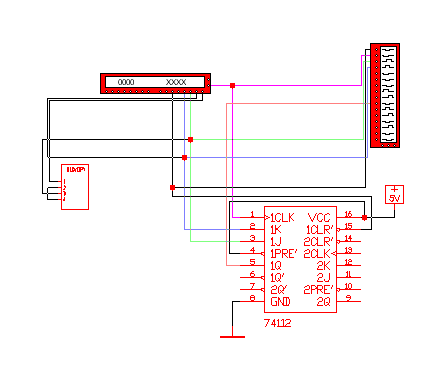

1. В окне программной среды EWB загрузить файл «Trigger1» для изучения ИМС 74112 (155ТВ9), включённой в библиотеку элементов. Для JK – триггера 74112 используется испытательная схема, приведённая на рис. 3.33.

На этой схеме для задания входных сигналов триггера используется генератор слов, а для анализа выходных сигналов – логический анализатор из меню контрольно-измерительных приборов программы. Обозначения используемых выводов микросхемы следующие – 1CLK – тактовый вход, 1K и 1J – информационные входы, 1PRE’ – асинхронная предустановка триггера в единичное состояние (активный уровень низкий), 1CLR’- асинхронный сброс триггера (активный уровень низкий), 1Q, 1Q’ – прямой и инверсный выходы триггера, VCC – питание, GND – заземление.

Изучение триггера начинается с изучения его таблицы ис-

Рис. 3.33. Испытательная схема

для JK-триггера

тинности, вызываемой нажатием клавиши помощи F1, табл. 3.8.

Таблица 3.8

|

|

CLK |

J |

K |

Q |

|

0 |

1 |

X |

X |

X |

1 |

0 |

1 |

0 |

X |

X |

X |

0 |

1 |

0 |

0 |

X |

X |

X |

1 |

1 |

1 |

1 |

NEG |

0 |

0 |

Hold |

|

1 |

1 |

NEG |

1 |

0 |

1 |

0 |

1 |

1 |

NEG |

0 |

1 |

|

1 |

1 |

1 |

NEG |

1 |

1 |

Toggle |

|

1 |

1 |

0 |

X |

X |

Hold |

|

В этой таблице приняты следующие обозначения: X – логическая переменная может принимать любое значение, Hold – сохранение предшествующего состояния, Toggle – инверсия предшествующего состояния, NEG – запись информации происходит по отрицательному перепаду тактового сигнала.

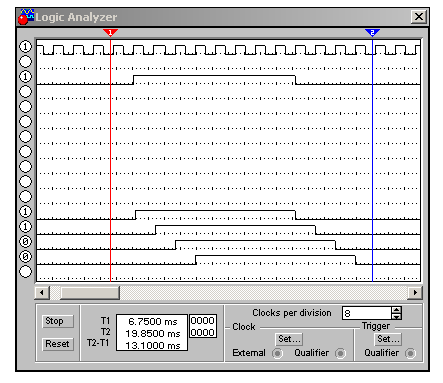

Затем с помощью логического анализатора наблюдаются временные диаграммы работы JK–триггера.

В качестве примера приведем временные диаграммы работы в счётном режиме, рис. 3.34.

М ежду

вертикальными визирами сверху вниз

наблюдаются сигналы: CLR

=1; CLK;

J

= 1; K

= 1; Q.

Видно, что по каждому

ежду

вертикальными визирами сверху вниз

наблюдаются сигналы: CLR

=1; CLK;

J

= 1; K

= 1; Q.

Видно, что по каждому

отрицательному перепаду тактового сигнала триггер инвертирует предшествующее состояние.

2. Далее в том же порядке исследуется интегральный D–триггер типа 74175 (155ТМ8). Для этого следует загрузить файл

«Trigger2», схема включения которого приведена на рис. 3.35.

Обозначения выводов микросхемы аналогичны вышеприведенным за исключением одного 1D – информационный вход.

Таблица истинности вызывается нажатием клавиши помощи F1 и имеет следующий вид, табл. 3.9.

B

Таблица 3.9

CLK

D

Q

Q

0

X

X

0

1

1

POS

1

1

0

1

POS

0

0

1

1

0

X

Hold

![]()

В качестве самостоятельного задания

предлагается собрать схему простейшего

RS–триггера

с прямыми или инверсными входами и

получить таблицу истинности.

качестве самостоятельного задания

предлагается собрать схему простейшего

RS–триггера

с прямыми или инверсными входами и

получить таблицу истинности.

ИНТЕГРАЛЬНЫЕ РЕГИСТРЫ В ПРОГРАММНОЙ СРЕДЕ EWB

1 .

В окне программной среды EWB

загрузить файл «Reg1»

для изучения четырёхразрядного регистра

памяти 74173 (К155ИР15), который является

библиотечным компонентом и может служить

примером устройства хранения с тремя

выходными состояниями. На рис. 3.37 показана

интегральная микросхема 74173.

.

В окне программной среды EWB

загрузить файл «Reg1»

для изучения четырёхразрядного регистра

памяти 74173 (К155ИР15), который является

библиотечным компонентом и может служить

примером устройства хранения с тремя

выходными состояниями. На рис. 3.37 показана

интегральная микросхема 74173.

На этом рисунке выводы 1D, 2D, 3D, 4D – входы регистра с логическими элементами разрешения записи путём подачи логического 0 на входы M, N. Выходы Q1, Q2, Q3, Q4 выполнены с третьим высокоомным Z – состоянием (при сигнале 1 на выводах G1’, G2’). Запись информации в регистр производится по положительному перепаду тактового импульса на входе CLK, если на входы M, N подано напряжение низкого уровня. Сигнал очистки регистра CLR имеет высокий активный уровень. Дальнейшее изучение работы регистра проводится по нижеприведенной таблице состояний, табл. 3.10. Высокоомное состояние позволяет организовать работу нескольких регистров памяти на общую шину – электрически выходы всех регистров объединены, но в каждый момент времени на шину работает только один из них. Выбор работающего регистра определяют сигналы на входах G1’и G2’. При этом данные из других регистров в общую шину не проходят, выходы регистра не влияют на работу других аналогичных выходов, присоединенных к проводникам общей шины.

Таблица 3.10

CLEAR |

CLK |

G'1 |

G'2 |

D |

Q |

1 |

Х |

Х |

Х |

Х |

0 |

0 |

0 |

0 |

0 |

0 |

Q0 |

0 |

POS |

1 |

X |

X |

Q0 |

0 |

POS |

0 |

0 |

0 |

Q0 |

0 |

POS |

0 |

0 |

0 |

0 |

0 |

POS |

0 |

0 |

1 |

1 |

На рис. 3.38 в качестве примера приведена схема двух интегральных регистров 74173, работающих на общую шину.

На верхний регистр подаётся изменяющаяся двоичная информация с генератора слов, а на нижний регистр постоянное двоичное слово 1000. В соответствии с управляющими сигналами на входах M, N, G1’, G2’ регистров на общую шину передаётся информация то с верхнего регистра, то с нижнего.

Семисегментные и светодиодные индикаторы позволяют наглядно изучить работу устройства.

2. В окне программной среды EWB загрузить файл «Reg3» для изучения второго класса регистров - регистров сдвига на примере библиотечного регистра 74195 (К155ИР12). Это быстродействующий регистр для выполнения операций сдвига, счёта, накопления и взаимного параллельно-последовательного преобразования двоичных слов. На рис. 3.39 показано обозначение регистров сдвига ИМС 74195 на принципиальных и функциональных электрических схемах.

Е сли

на вход SH/LD’

подано напряжение низкого уровня, то

все четыре триггера регистра запускаются

одним положительным перепадом тактового

сигнала на входе CLK.

При этом данные от параллельных входов

A,

B,

C,

D

передаются на соответствующие выходы

QA,

QB,

QC,

QD.

Фактически в этом случае регистр работает

в режиме приёма данных (как параллельный

регистр). Если на вход SH/LD’

подано напряжение высокого уровня, то

через входы первого триггера J

и K’

в регистр вводятся последовательные

данные. Вход J

имеет высокий активный уровень, вход

K’

– низкий; если их соединить, то получается

простой D

– вход. Введённые данные сдвигаются в

направлении от QA

к QB,

QC,

а затем к QD

после каждого положительного перепада

на тактовом входе CLK.

Таблица состояний ИМС приведена ниже,

табл. 3.11.

сли

на вход SH/LD’

подано напряжение низкого уровня, то

все четыре триггера регистра запускаются

одним положительным перепадом тактового

сигнала на входе CLK.

При этом данные от параллельных входов

A,

B,

C,

D

передаются на соответствующие выходы

QA,

QB,

QC,

QD.

Фактически в этом случае регистр работает

в режиме приёма данных (как параллельный

регистр). Если на вход SH/LD’

подано напряжение высокого уровня, то

через входы первого триггера J

и K’

в регистр вводятся последовательные

данные. Вход J

имеет высокий активный уровень, вход

K’

– низкий; если их соединить, то получается

простой D

– вход. Введённые данные сдвигаются в

направлении от QA

к QB,

QC,

а затем к QD

после каждого положительного перепада

на тактовом входе CLK.

Таблица состояний ИМС приведена ниже,

табл. 3.11.

Таблица 3.11

CLEAR |

LOAD' |

CLK |

J K' |

A B C D |

QA |

QB |

QC |

QD |

Q'D |

0 |

X |

X |

X..X |

X X X X |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

POS |

X X |

a b c d |

a |

b |

c |

d |

d' |

1 |

1 |

0 |

X X |

X X X X |

QA0 |

QB0 |

QC0 |

QD0 |

Q'D0 |

1 |

|

POS |

0 1 |

X X X X |

QA0 |

QA0 |

QBn |

QCn |

Q'Cn |

1 |

1 |

POS |

0 0 |

X X X X |

0 |

QAn |

QBn |

QCn |

Q'Cn |

1 |

1 |

POS |

1 1 |

X X X X |

1 |

QAn |

QBn |

QCn |

Q'Cn |

1 |

1 |

POS |

1 0 |

X X X X |

Q'An |

QAn |

QBn |

QCn |

Q'Cn |

В этой таблице QA0, QB0, QC0, QD0 и QАn, QBn, QCn, QDn – значения выходных сигналов регистра до и сразу после положительного перепада сигнала CLK соответственно. Включение ИМС 74195 в режиме приёма данных исследуется в схеме, приведенной на рис. 3.40. В этой схеме генератор слов задаёт последовательность двоичных слов, каждое из которых записывается в регистр по положительному перепаду тактового сигнала и появляется на выходе регистра.

3 .

В окне программной среды EWB

загрузить файл «Reg4»,

где ИМС 74195 включена по схеме сдвигового

регистра (см. рис. 3.41). Здесь для ввода

последовательной информации используются

входы первого триггера регистра, при

этом состояние входа A

является безразличным. Сдвиг входной

информации регистрируется логическим

анализатором. Если входы J

и K

первого триггера не объединять, возможны

дополнительные режимы работы схемы,

связанные с изменением выходного сигнала

первого триггера (см. табл. 3.11).

.

В окне программной среды EWB

загрузить файл «Reg4»,

где ИМС 74195 включена по схеме сдвигового

регистра (см. рис. 3.41). Здесь для ввода

последовательной информации используются

входы первого триггера регистра, при

этом состояние входа A

является безразличным. Сдвиг входной

информации регистрируется логическим

анализатором. Если входы J

и K

первого триггера не объединять, возможны

дополнительные режимы работы схемы,

связанные с изменением выходного сигнала

первого триггера (см. табл. 3.11).

Работа сдвигового регистра хорошо иллюстрируется временными диаграммами, полученными с помощью логического анализатора и приведёнными ниже (см. рис. 3.42).

Между двумя вертикальными визирами логического анализатора сверху вниз регистрируются следующие сигналы: тактовые сигналы, которые определяют значение времени задержки при сдвиге информации; входная информация произвольного вида на объединённых входах регистра сдвига ( J и K ); выходные сигналы регистра ( QA, QB, QC, QD ), которые представляют собой сигналы

с прямых выходов каждого из четырёх триггеров в составе регистра. Видно, что временной сдвиг входной информации происходит по положительному перепаду

тактового

сигнала. Отметим, что для ИМС серии 74195

возможны следующие режимы сдвига: 1 –

сдвиг и установка по первому каскаду (

JK

= 11 ); 2 – сдвиг и сброс по первому каскаду

( JK

= 00 ); 3 – сдвиг и переключение первого

каскада ( JK

= 10 ); 4 – сдвиг и хранение в первом каскаде

(JK

= 01).

тактового

сигнала. Отметим, что для ИМС серии 74195

возможны следующие режимы сдвига: 1 –

сдвиг и установка по первому каскаду (

JK

= 11 ); 2 – сдвиг и сброс по первому каскаду

( JK

= 00 ); 3 – сдвиг и переключение первого

каскада ( JK

= 10 ); 4 – сдвиг и хранение в первом каскаде

(JK

= 01).

4. В качестве самостоятельного задания студентам предлагается разработать схему четырехфазного распределителя тактовых импульсов на основе сдвигового регистра 74195 и простейших логических элементов 2И-НЕ и 4ИЛИ-НЕ. Использовать индикаторные элементы, подключаемые к выходам разработанной схемы. Наблюдать визуально работу распределителя при частоте входных сигналов (1 - 2)Гц. Выделить в разработанном устройстве узлы, выходные сигналы которых представляют собой распределенные единичные уровни напряжения.

Рис. 3.42. Работа сдвигового