- •1.1. Понятие архитектуры компьютеров

- •1.2. Архитектура аппаратных средств

- •1.3. Архитектура неймановского компьютера

- •1.4. Архитектура постнеймановських компьютеров

- •2.1. Архитектура системной платы

- •2.1.1. Синхронизация

- •2.1.2. Чипсет

- •2.2. Система шин

- •2.2.1. Особенности организации работы шины

- •3.1. Общие характеристики микропроцессоров и эволюция развития

- •3.2. Программная модель

- •3.2.1. Программная модель 16-разрядных микропроцессоров

- •3.3. Организация защищенного режима

- •33.1. Основные понятия защищенного режима

- •4.1. Логическая организация памяти

- •4.1.1. Распределение адресного пространства памяти

- •4.1.2. Расширенная память

- •4.1.3. Отображаемая (дополнительная) память (Expanded Memory)

- •4.1.4. Системная или "теневая" память (Shadow ram)

- •4.2. Физическая организация памяти

- •Системная поддержка lpt-порта

- •7.1. Организация прерываний

- •8.2. Программируемый контроллер прерываний

2.1.2. Чипсет

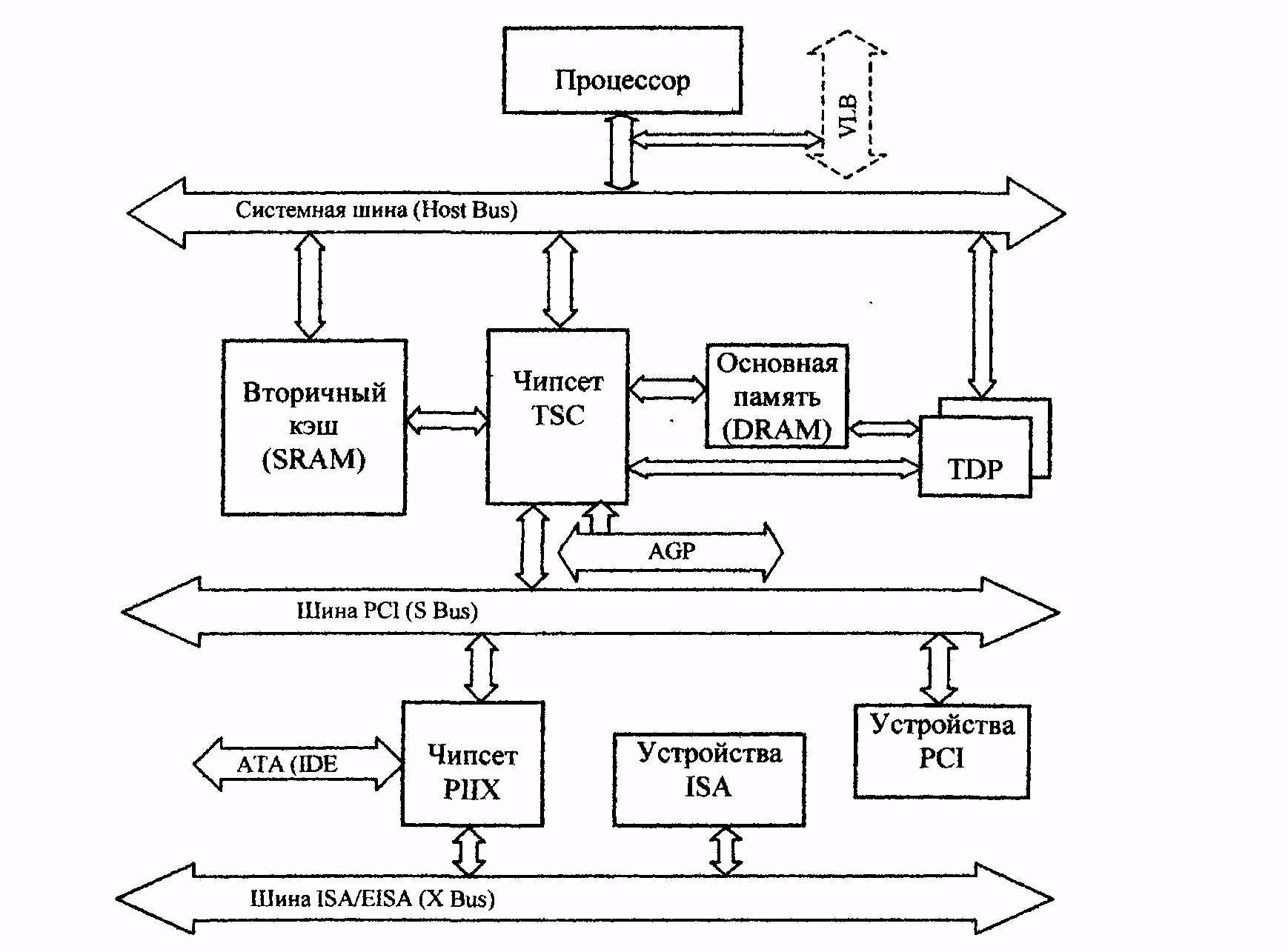

Чипсет задает архитектуру системной платы и является связующим звеном между ее компонентами (рис. 2.1).

Центральную роль в архитектуре играет процессор. К его локальной шине (Host Bus) подключаются модули вторичного кэша. Основная динамическая память имеет собственную мультиплексированную шину адреса и шину данных, обычно изолированную от локальной шины процессора. На этом «этаже» архитектуры чипсет решает следующие задачи:

Обслуживание управляющих и конфигурационных сигналов процессора.

- Мультиплексирование адреса и формирование управляющих сигналов динамической памяти, связь шины данных памяти с локальной шиной.

- Формирование управляющих сигналов вторичного кэша, сравнение его тегов текущим адресом обращения на локальной шине.

Рисунок 2.1 - Архитектура системной платы

- Обеспечение когерентности (согласованности) данных в обоих уровнях кэш-памяти и основной памяти при обращении как со стороны процессора (процессоров), так и от контроллеров шины РС1.

- Связь мультиплексированной шины адреса и данных шины РС1 с локальной шиной процессора и шиной динамической памяти.

- Формирование управляющих сигналов шины PCI, арбитраж контроллеров шины.

Приведенная структура реализуется на трех микросхемах чипсета Intel82430FX - системном контроллере (TSC 82437FX) и двух корпусах коммутаторов данных (TDP 82371FB).

Следующий (вниз) этаж архитектуры - устройства, подключенные к шине PCI. Эта шина является центральной в современных системных платах, и все интерфейсные адаптеры, а также системные средства ввода/вывода в конечном счете общаются с ядром системы (процессором и памятью) через шину PCI. Кроме плат расширения, устанавливаемых в слоты шины PCI, ее абонентом является и мост PIIX - практически неотъемлемая часть современных плат.

PIIX (PCI ШЕ ISA aXcelerator) представляет собой многофункциональное устройство, на которое возлагаются следующие функции:

- Организация моста между шинами PCI и ISA/EISA с согласованием частот синхронизации этих шин.

Реализация высокопроизводительного, обычно двухканального интерфейса накопителей внешней памяти ATA (IDE).

- Реализация стандартных системных средств ввода/вывода - двух контроллеров прерываний (PIC), двух контроллеров прямого доступа к памяти (DMA), трехканального системного таймера, канала управления динамиком, логики немаскируемого прерывания.

- Коммутация линий запросов прерывания и каналов прямого доступа к памяти шин PCI и ISA.

Поддержка режимов энергосбережения - обработка SMM, программирование событий управления потреблением, управление частотой процессора, переключение режимов.

- Реализация моста с внутренней шиной X-Bus, используемой для подключения микросхем контроллера клавиатуры, BIOS, CMOS RTC, контроллеров гибких дисков и интерфейсных портов (СОМ и LPT). Перечисленные контроллеры (кроме микросхемы BIOS) могут быть реализованы внутри микросхемы чипсета).

- Реализация контроллера USB.