Организация ЭВМ / shpor

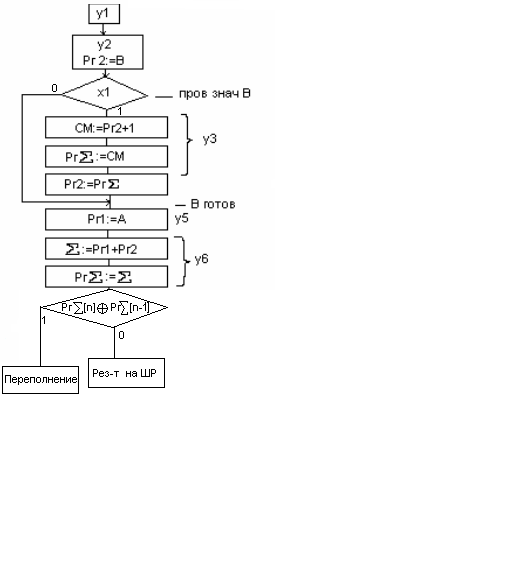

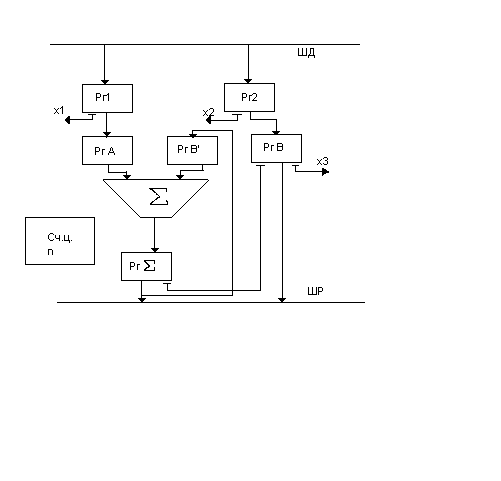

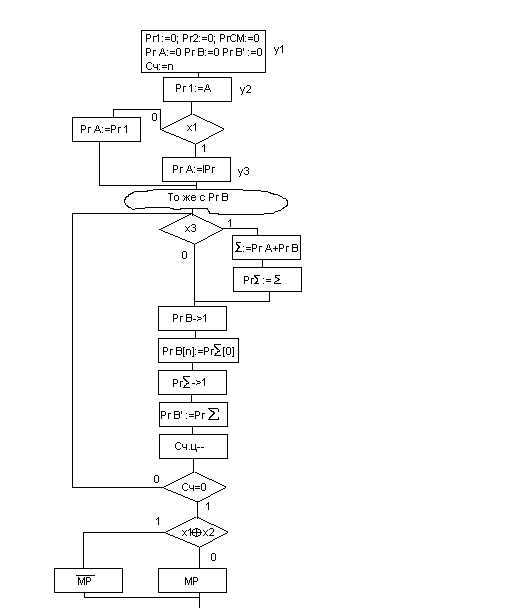

.DOC2.АЛУ для сложения чисел с фиксир (,)

Р

г1:=0

г1:=0

Рг2:=0

Рг∑:=0

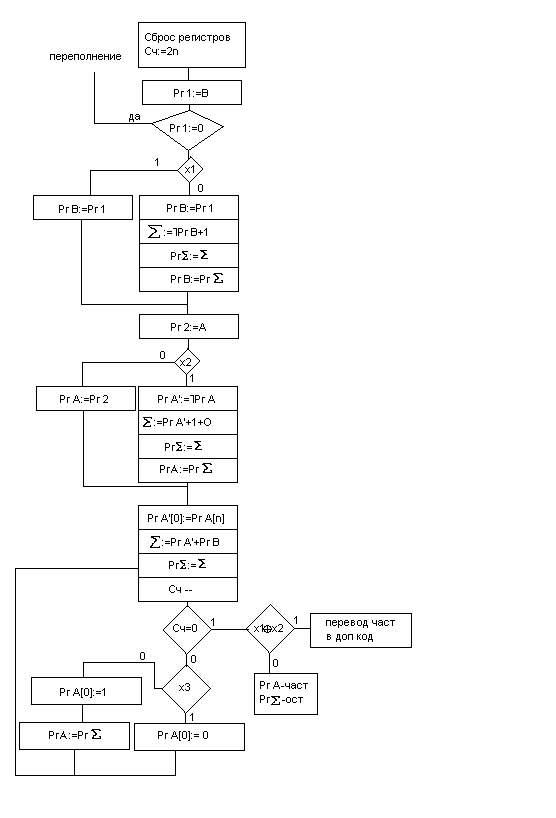

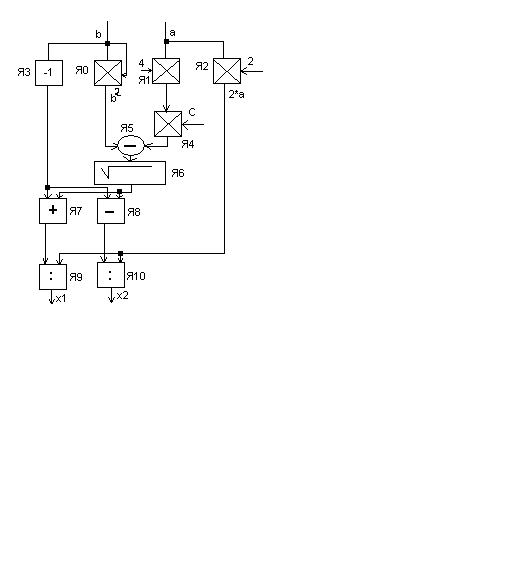

3.АЛУ для * чисел с фикс(,)_методы ускор *.

4.АЛУ для деления чисел с фиксир(,)

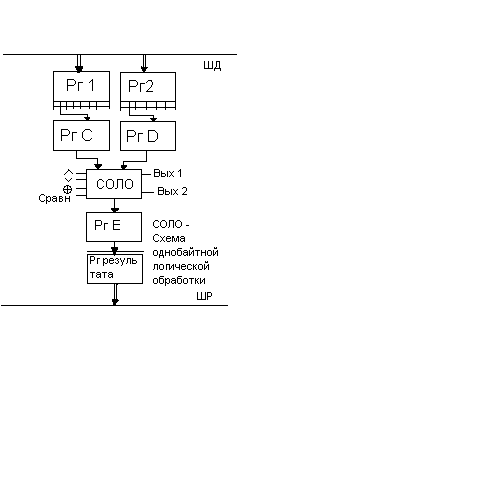

5.Устройтсво для выполнения лог.опер.Особеннсти арифм

с плавающей (,)

6.Многофункциональное АЛУ

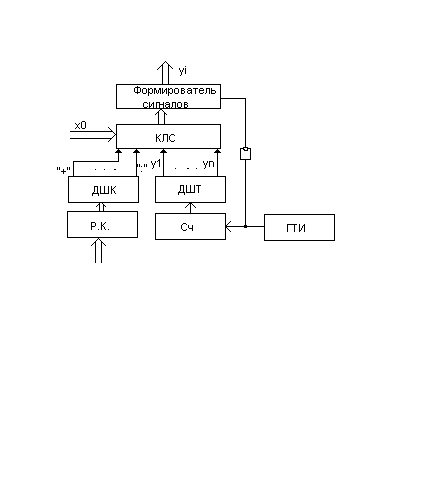

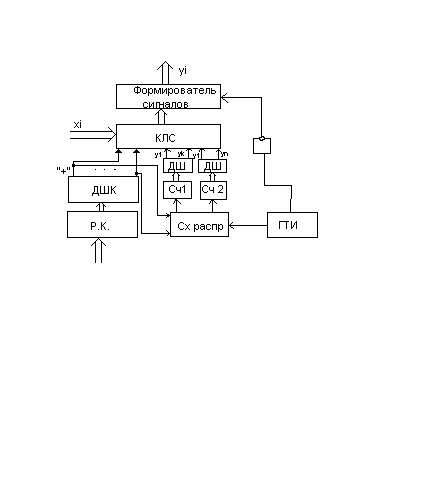

7.Управляющие автоматы с жесткой логикой

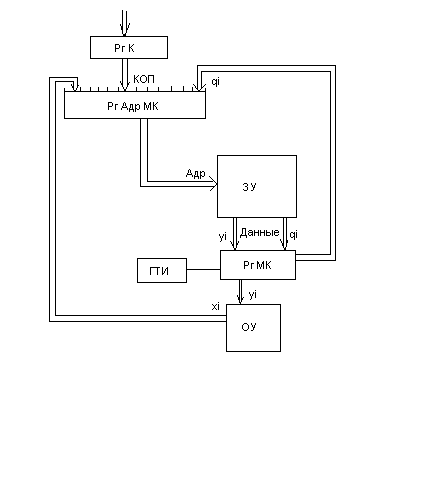

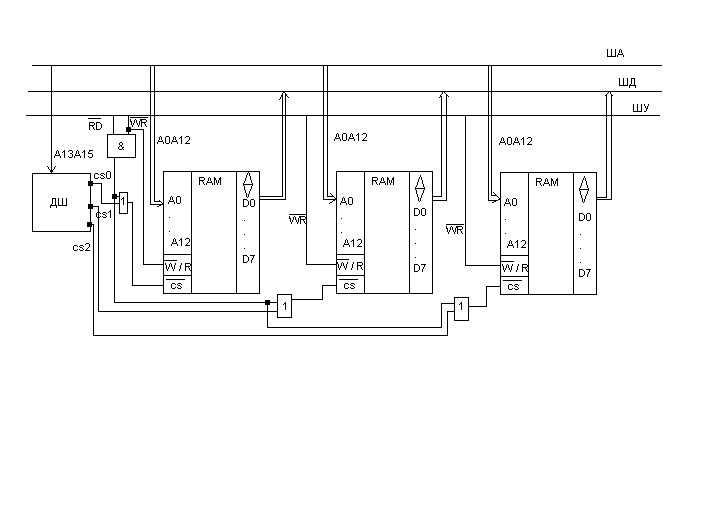

8.Управл автоматы с МПУ

9.Требования к кодам команди способы кодирования.

|

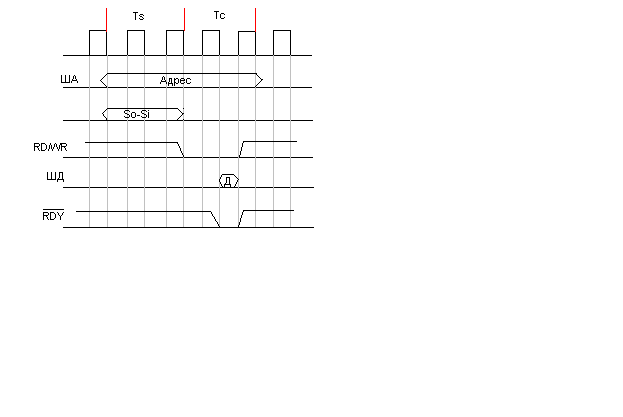

y1 |

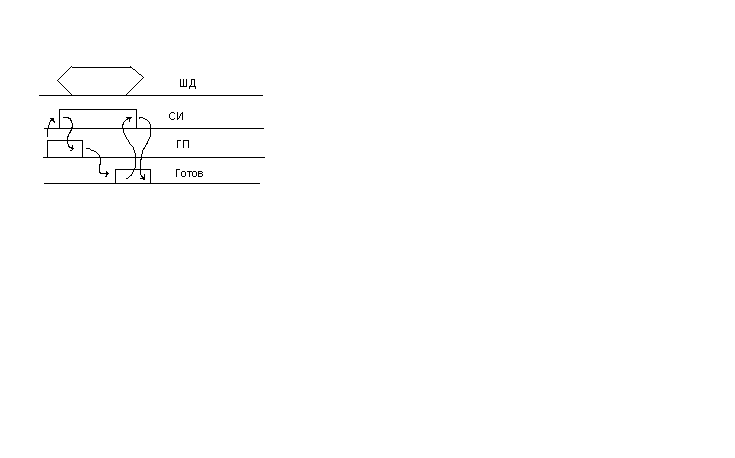

y2 |

… |

. |

yn |

К

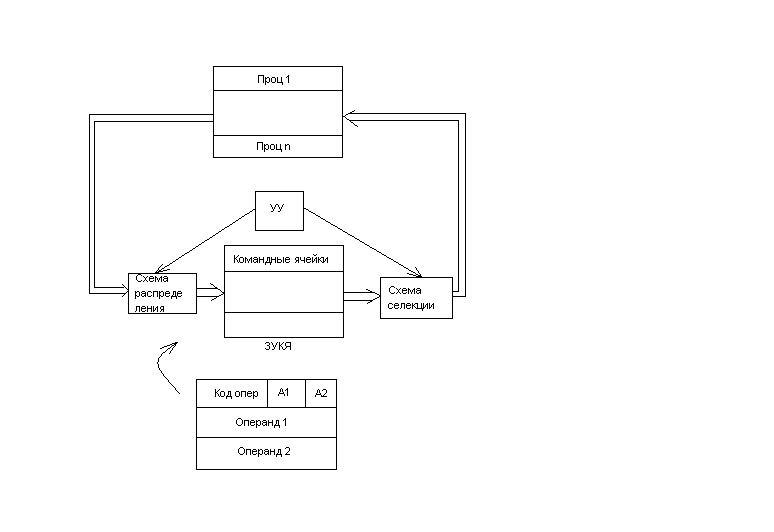

К

|

y1…………yn |

|

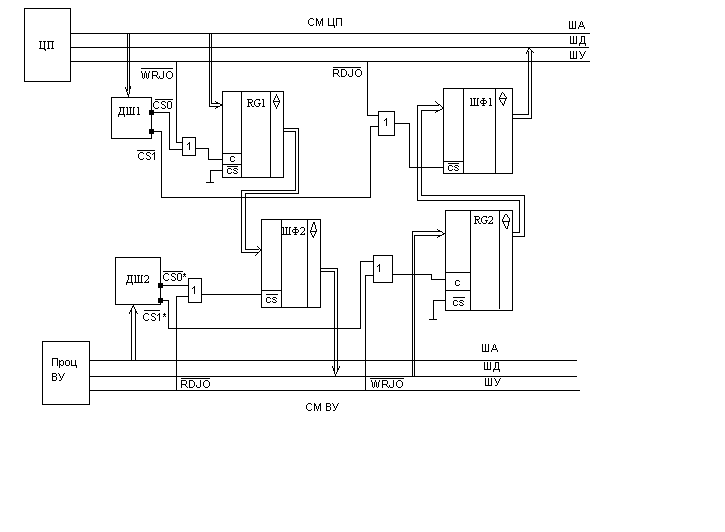

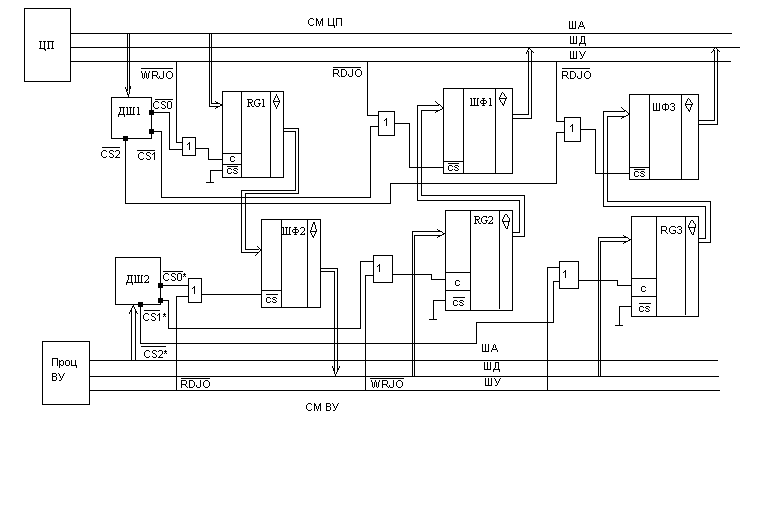

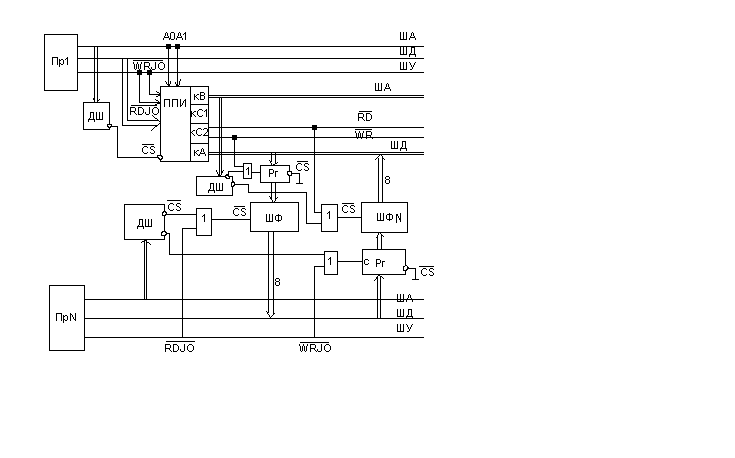

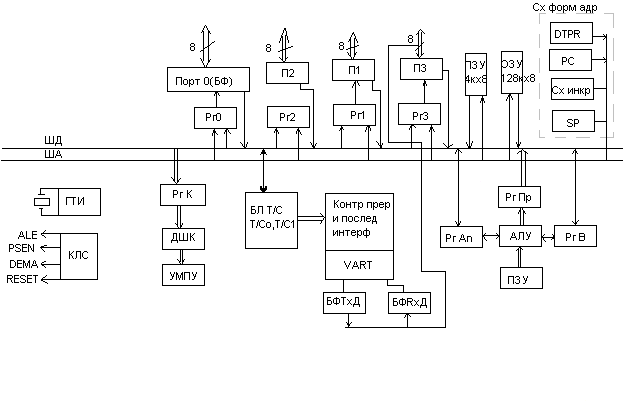

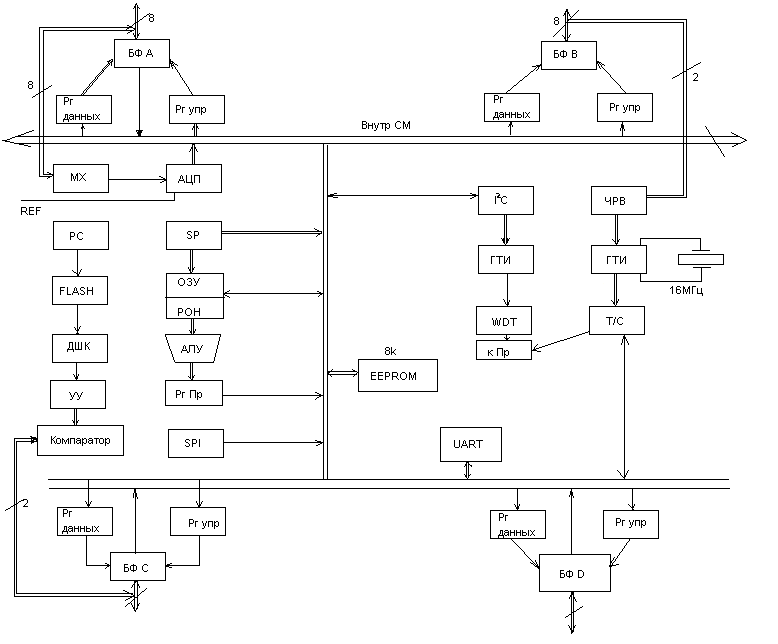

11.Шинные формирователи и рег-ры. Орг СМ 580 серии

|

CS |

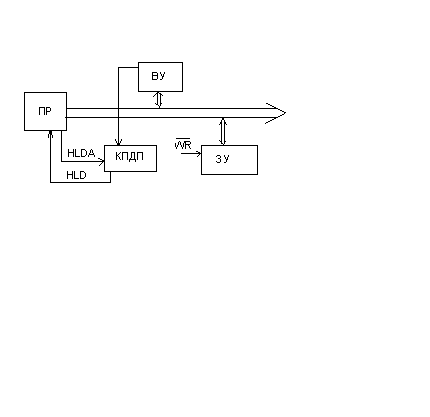

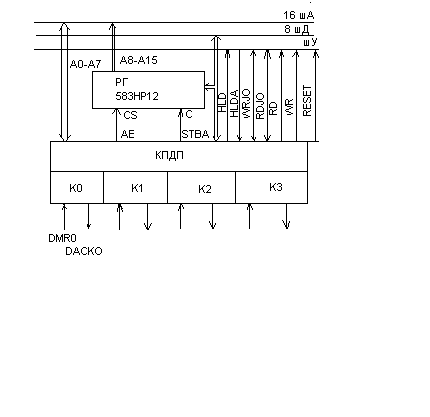

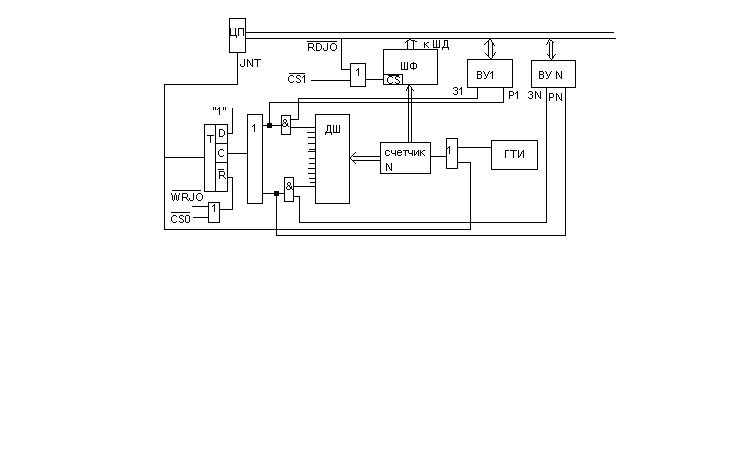

T |

Направл |

|

1 |

Х |

Х |

|

0 |

0 |

A->B |

|

0 |

1 |

B->A |

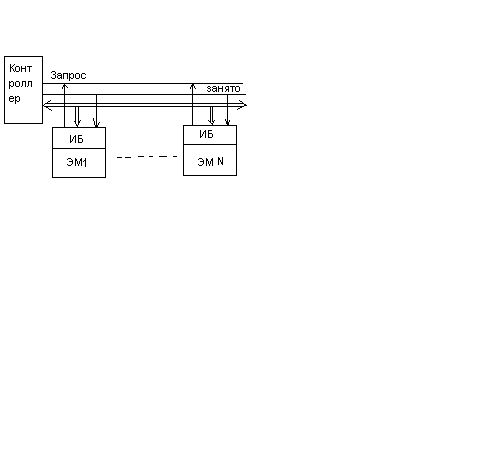

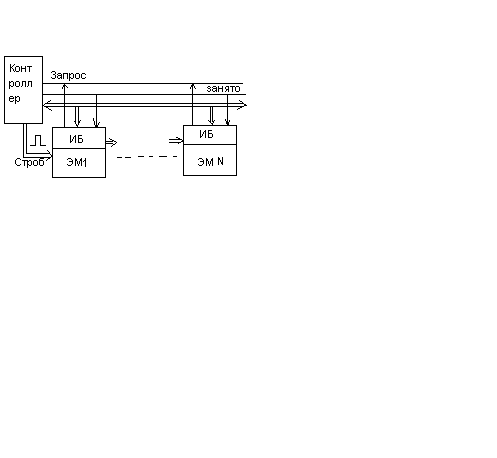

Организация СМ процессора

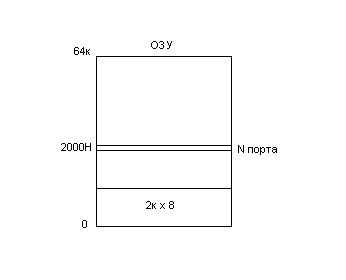

12.Организация модулей ПЗУ

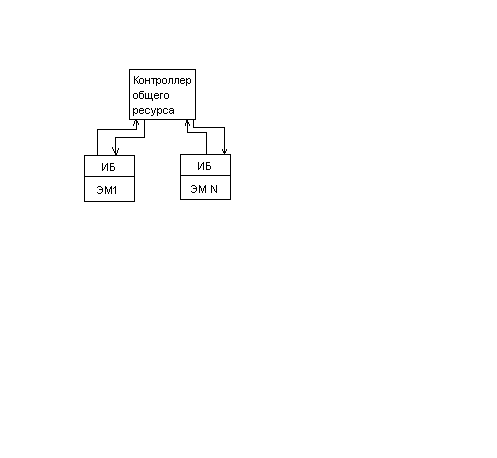

13.Организация модулей статического ОЗУ.

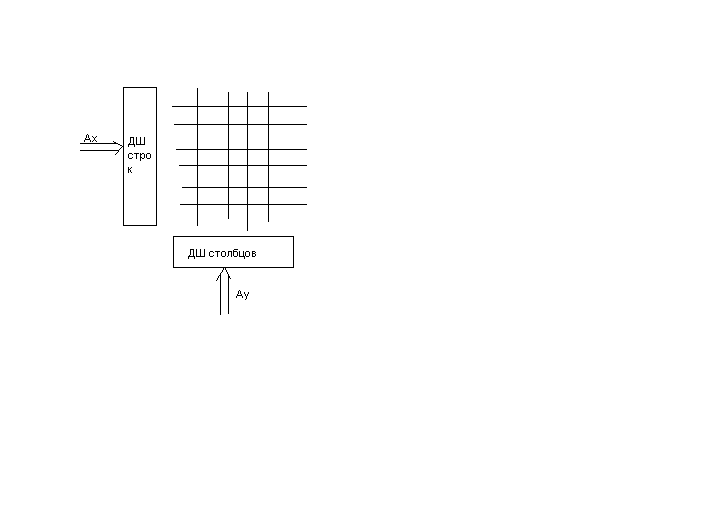

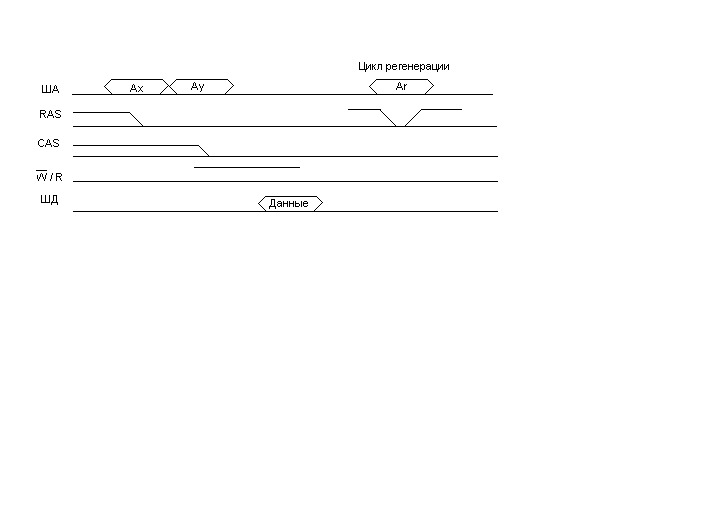

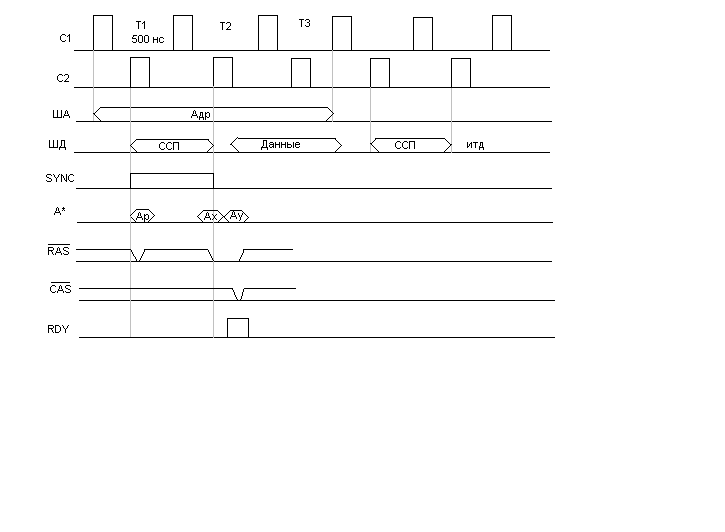

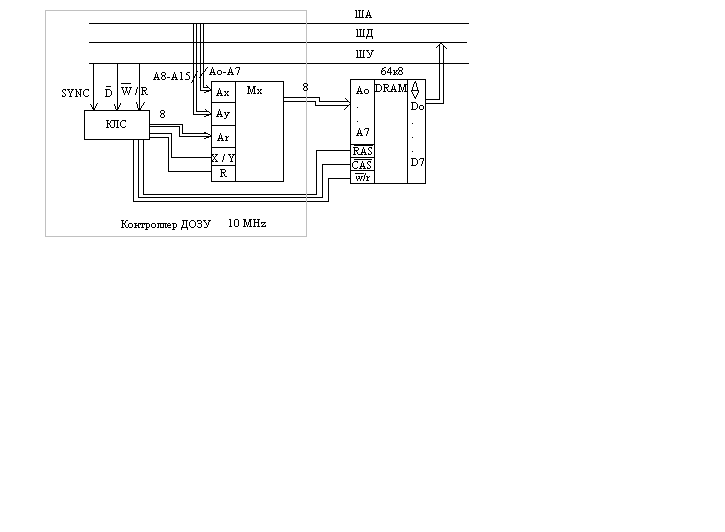

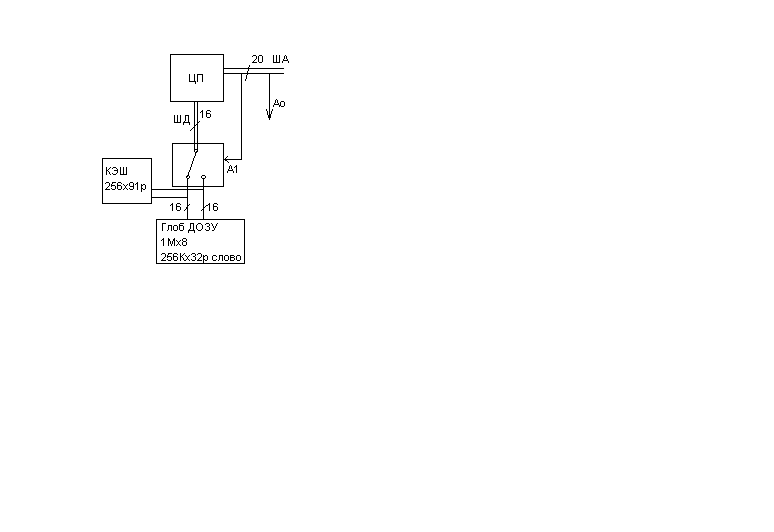

14.Организация динамических модулей ДОЗУ

15.Покдл модулей ДОЗУ к СМ(прозр рег).Способы регенерации

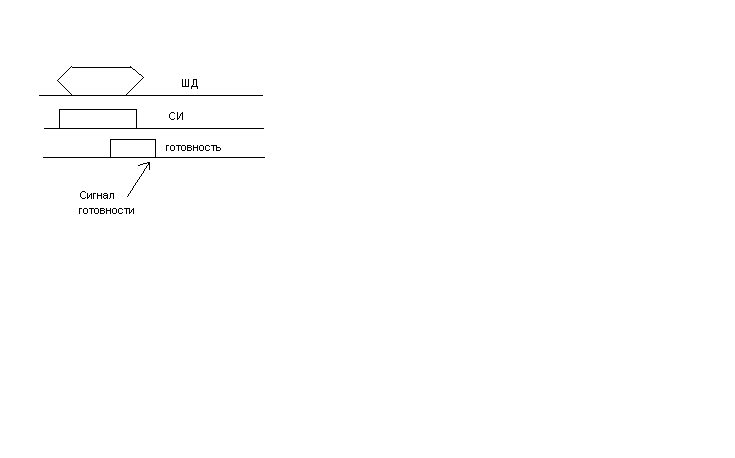

16.Синхр способ продкл ВУ к СМ

17.Асинхр способ продкл ВУ к СМ

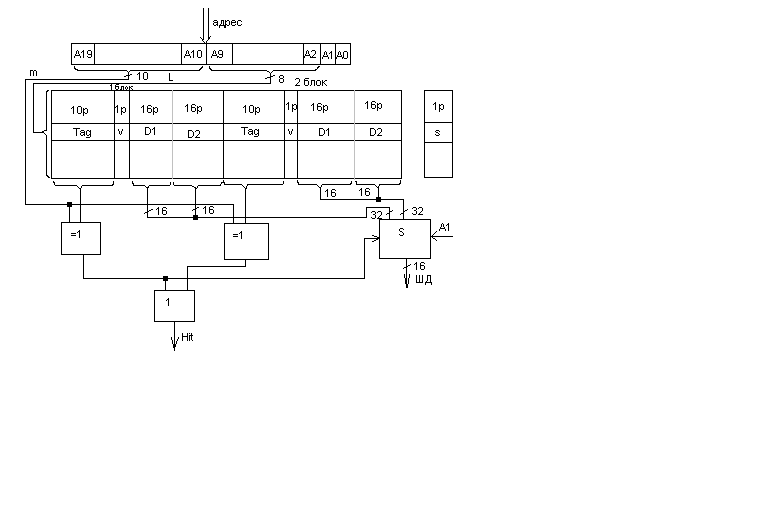

18.Организация КЭШ памяти.

|

|

Копия в КЭШ |

Инф |

|

|

В КЭШ |

В гл ДОЗУ |

||

|

Чтение |

Есть Нет |

Чтение Запись+след слово |

- Чтение |

|

Запись |

Есть Нет |

-(обновл) - |

Запись Запись |

19.Организация виртуальной памяти.

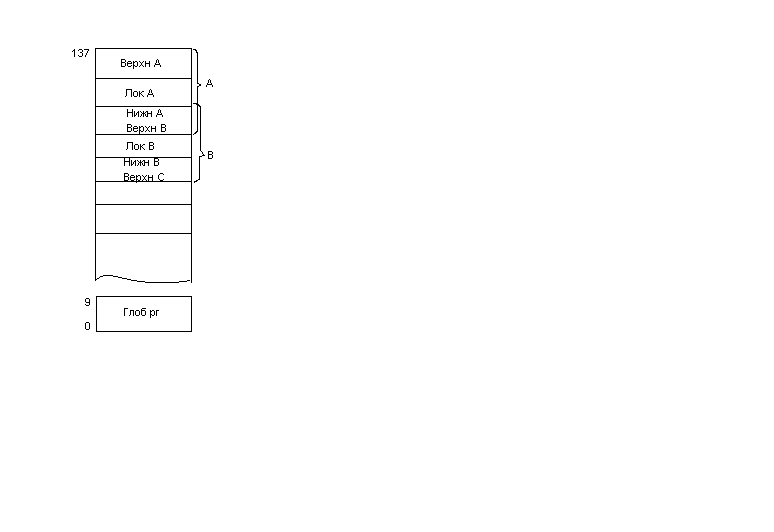

20.Общие полож.RISC-проц.Берклинская арх.

|

Верхние регистры |

|

Локальные регистры |

|

Нижние регистры |

|

Глобальные регистры |

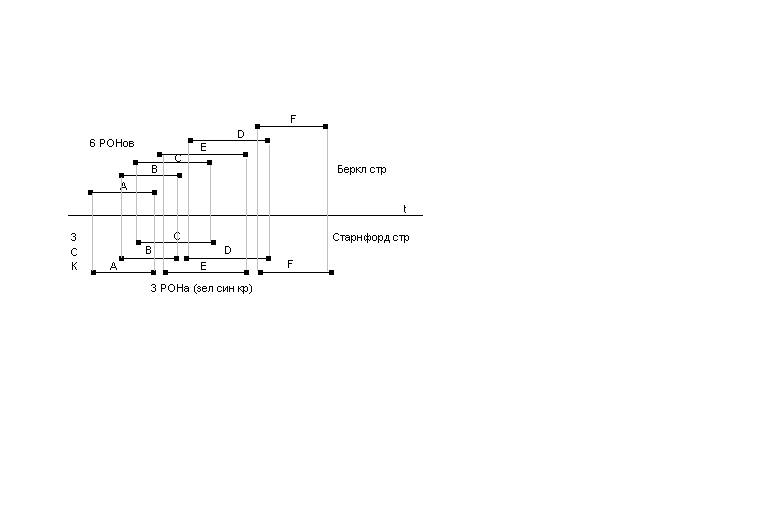

21.Старнфордсая структура

22.Машины упр потоками данных(DF-машины)

![]()

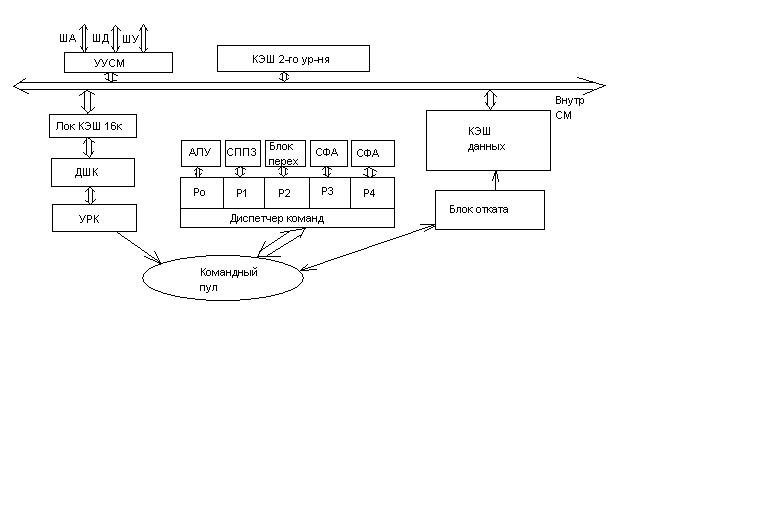

23.Pentium

24.Pentium II,Pentium Pro

25.Pentuim VI

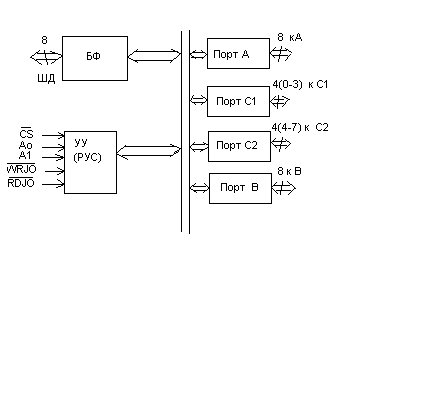

26.ППИ

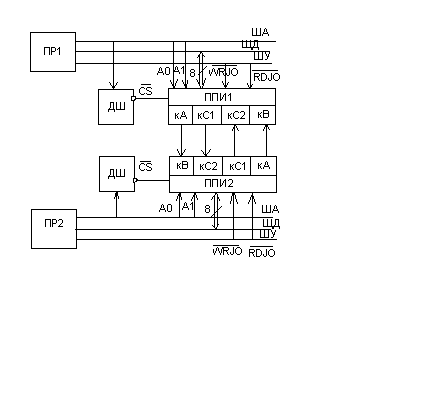

27.М/О ч/з ППИ.

28.УСАПП

29.Контролер ПДП.

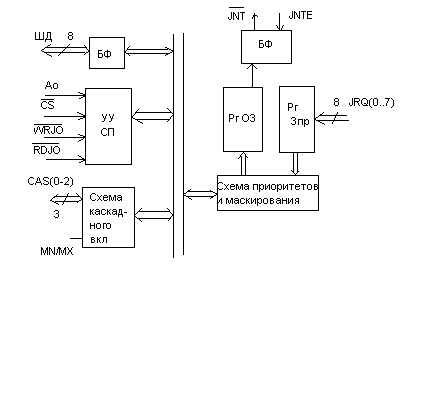

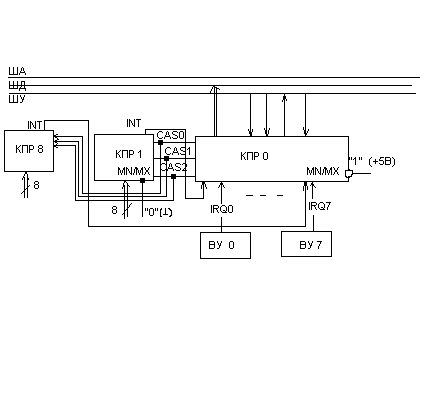

30.Прогр контр прерываний.

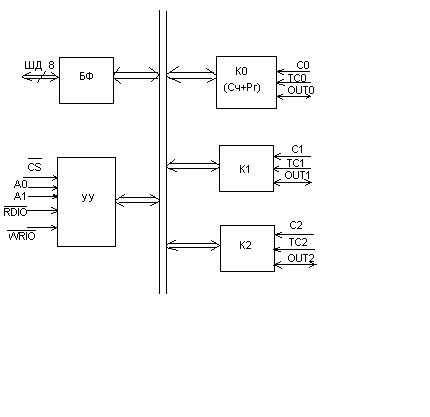

31.Таймер

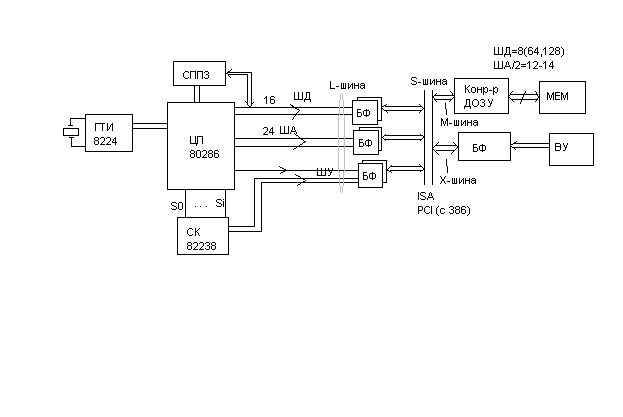

32.Орг ЭВМ типа IBM PC AT

33,Однокристальн ЭВМ

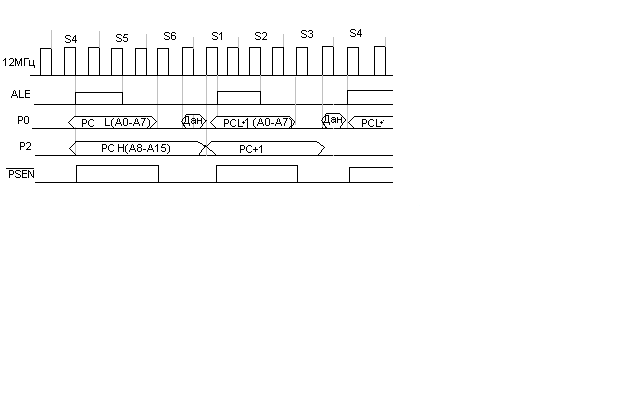

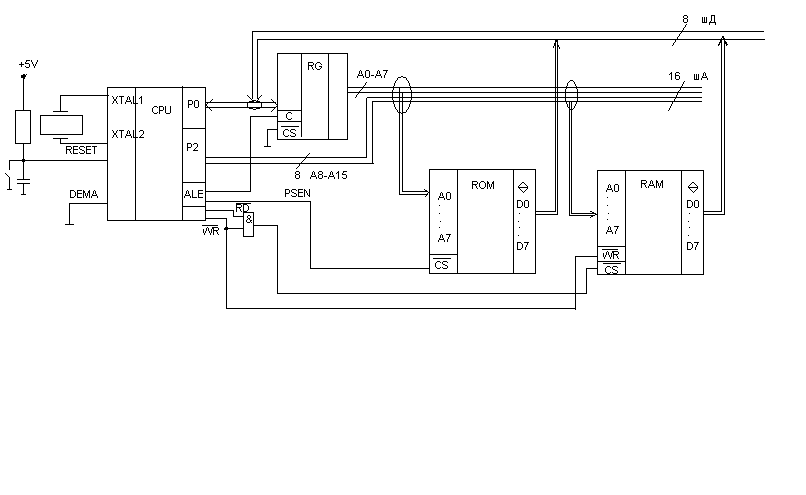

34.Протокол обмена подкл ОЗУ/ПЗУ MCS-51

Обращение к внешней памяти данных

Обращение к внешней памяти прогр.

35.ATmega 32

36.Классификация ОЭВМ по табл

|

Фир-ма |

Тип |

Раз-рез. |

fт, МГц |

Кол-во 8р.|| п.вв-выв |

P потр. мВт |

|

Hita-chi |

H8/30 48F |

16 |

16 |

78 pin |

112 (20 мА) |

|

HD 64F 13052 |

16 |

18 |

70 pin |

120 |

|

|

HD64 F7055 |

32 |

40 |

149 pin |

240 |

|

|

Si-mens

|

SAKC 16316 F25F |

16 |

25 |

77 |

500 |

|

C167 |

16 |

20 |

111 |

500 |

|

|

Micro-nas |

CDC 1607F |

16 |

12 |

~100 |

_ |

|

CDC 32076 |

32 |

24 |

~100 |

_ |

|

|

Moto- rolla |

68HC 912D 6128 |

16 |

8 |

68 |

480 |

|

MCS- 555 |

32 |

40 |

20+ спец пор. |

1Вт |

|

Flash |

RAM |

T/C |

АЦП |

Посл. инт-с |

Прим. |

|

128кб |

4к |

6 |

10 (одн- кан) |

SCI |

кор- пуса 128 pin -40°C +85°C

|

|

512к |

8к |

9 |

8кан. ×10р |

SCI, I2C |

|

|

512к |

32к |

34 |

16к. ×10р |

5 UA-RT, 2 SCI |

кор- пуса 176 pin -40°C +85°C

|

|

128к |

1к |

6 |

_ |

UA-RT, SPI |

100 pin -55° +125° |

|

128к |

4к |

10 |

16к. ×10р |

UA-RT, SCI |

144 -55° +125° |

|

256к |

6,5к |

6 |

9кан. ×10р |

UA-RT

|

128 pin -40°C +85°C

|

|

512к |

20к |

6 |

16к. ×10р |

UA-RT

|

|

|

128к |

2к |

9 |

3к× 10 |

2SCI, SPI, I2C |

-40°C +85°C

|

|

448к |

26к |

До 60 |

32к× 10 |

SCI, SPI,2 CAN (лок. сети) |

275 pin |

35.ВС классификация по Флинну

![]()

![]()

![]()

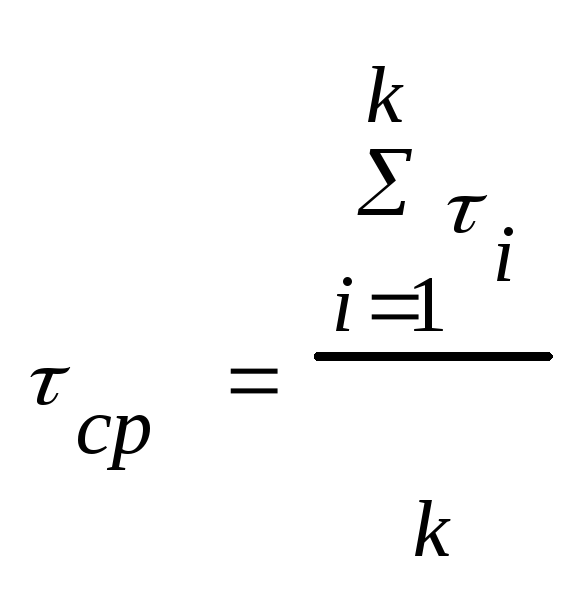

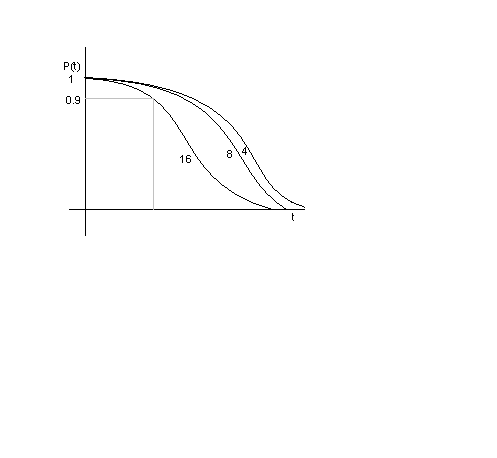

38.Производительность ЭВМ и сетей.

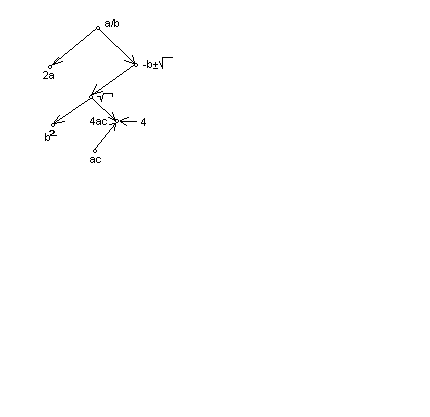

![]() i=1,к:

i=1,к:

![]()

![]()

![]()

![]()

![]()

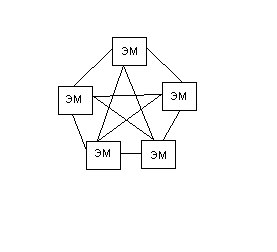

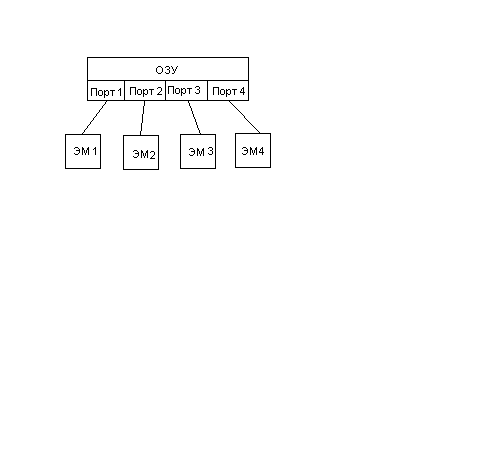

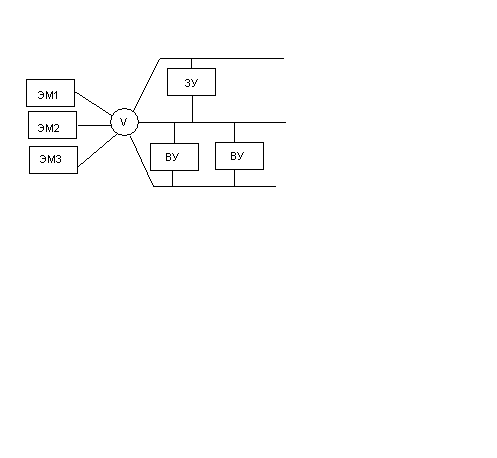

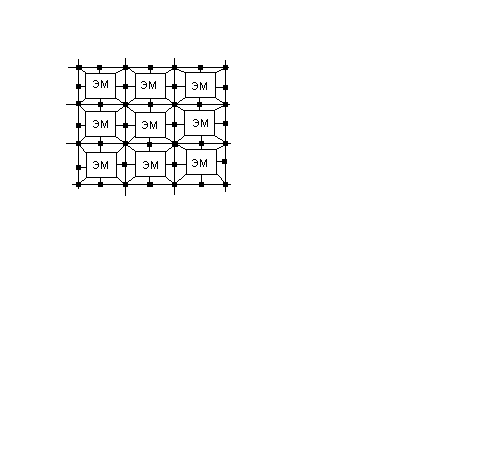

3 8.Типовые

структуры ВС

8.Типовые

структуры ВС

![]()

![]()

![]()

![]()

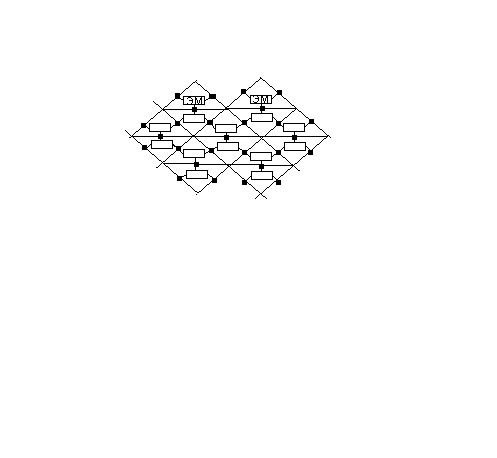

4 0.Архитектура

Сммр,Сvмр,См.

0.Архитектура

Сммр,Сvмр,См.

41.Сm структура.

![]()

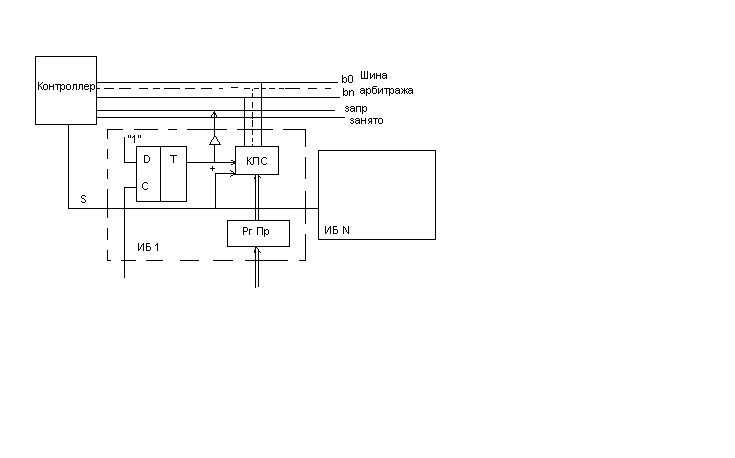

42. Понятие интерфейса. Виды арбитража

43.Арбитраж по последовательному опросу.

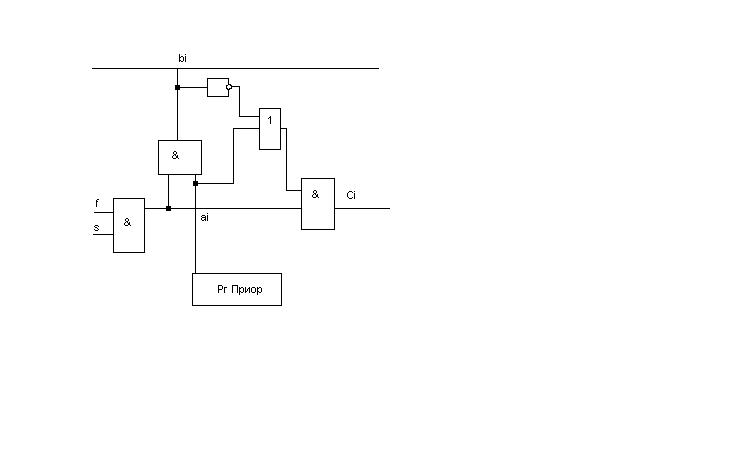

45.Арбитраж по || опросу.

|

ai |

bi |

ci |

|

0 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

нет |

46.Синхронизация информации в интерф.

![]()