Понятие иерархии

Организация передачи информации между уровнями подчиняется единым правилам иерархии: чтобы иерархическая модель памяти правильно функционировала, она должна соответствовать требованиям целостности и непротиворечивости данных.

Уровней разбиения памяти может быть много. Понятие иерархии в основном связывает соседние уровни. Поэтому при оценке иерархических взаимодействий важны уровень выше и уровень ниже, как они между собой взаимодействуют. Для того, чтобы сопоставлять информацию на соседних уровнях, используют отдельные элементы. Минимальным элементом сравнения является блок (обычно число байт, кратное степени 2). Размер блока меньше, чем выше уровень иерархии. Уровни отличаются быстродействием, стоимостью, размером.

Обмен блоками информации происходит постоянно: чтение с нижнего на более высокий уровень, запись с верхнего на нижний, замещение блоков и т. п.

Существует количественная оценка, характеризующая:

1) долю промахов и попаданий (в %). Если доля попаданий < 50 %, то это свидетельствует о неэффективном функционировании памяти. Доля попаданий зависит от величины блока и размера памяти.

2) Время обращения к блоку определяется задержкой от адресации до нахождения 1-го элемента блока.

3) Время пересылки – время обращения + время пересылки. Здесь серьезное влияние оказывает интерфейс, связывающий 2 соседних уровня иерархии.

При организации всего процесса работы решаются следующие задачи:

где блок размещается на уровне памяти (куда его поместить)?

поиск блока (адресация);

какой блок может быть замещен?

что происходит в момент записи блока при движении от верхнего уровня иерархии к нижнему?

Организация оперативной памяти

П![]() о

своей природе это память с произвольным

доступом. Каждый элемент имеет свой

конкретный адрес и может быть индивидуально

и независимо изменен.

о

своей природе это память с произвольным

доступом. Каждый элемент имеет свой

конкретный адрес и может быть индивидуально

и независимо изменен.

Используемые компоненты:

электронные элементы статической памяти;

динамической памяти.

Такие компоненты имеют адресные входы, входы данных, управления и выходы данных:

Addr – шина, которая имеет некоторую разрядность;

Din, out – разрядность блока памяти – зависимости от того, как близка память к ПМ;

U – тактирование записи в ячейку памяти и выборки.

Фазы:

Адресация;

Управляющие сигналы;

Обращение (доступ);

Восстановление перед новым циклом (пауза между циклами).

Реально 4 фазы – это слишком много, поэтому стараются их совместить (управляющие сигналы сформировать вместе с адресом). Это вопрос конвейеризации.

23.04.01

Энергонезависимая память

ROM – (Read Only Memory). Самая простая микросхема – масочная ПЗУ. Структура: матрица, дешифратор, выходной буфер. Плотность упаковки выше, чем у статических ячеек памяти.

Др. тип – однократно программируемые. В качестве программируемого элемента – коммутационный элемент, который можно программировать (из-за его проводящих свойств).

В качестве пережигаемых перемычек стали использовать полевые транзисторы.

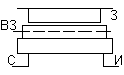

Потенциал затвора влияет на проводимость канала. Т. о., двойной затвор (ВЗ – внутренний затвор).

Заряд на внутреннем затворе меняет свойства канала (если заряд на внутреннем затворе есть, то транзистор управляется, если нет => транзистор не управляется основным затвором). Программирование происходит при приложении некоторого напряжения между С, И и З (стоком, истоком и затвором), которое должно быть больше, чем рабочее, чтобы заряды проникли через затвор.

Эти заряды на встроенном затворе с течением времени рассасываются (срок сохранности заряда небольшой). Возможно ультрафиолетовое стирание.

Память с электрическим стиранием и перепрограммированием. Технология флэш-памяти.

Запись положительным напряжением - "+" (+20,+30 В), а стирание "-" напряжением (-20,-30 В). В настоящее время программируют от внешнего источника 5 В.

На основе таких микросхем разработана новая технология – флэш-память. Чтобы программировать и стирать ее требуется программатор. К микросхеме добавляется внешний интерфейс, т. е. несколько регистров (адрес, состояние, управление), УУ, которое автономно управляет стиранием и программированием. Т. о., получается флэш-память.

Суть: структура состоит из нескольких блоков, секторов памяти. УУ обеспечивает следующие режимы:

считывание информации из блока;

стирание инф. из отдельных блоков (квазистирание 1 слова).

Блоки переупорядочиваются, что позволяет параллельно 1 блок читать, а другой записывать.

Существует язык команд флэш-памяти. Его команды:

идентификации устройства (идентификация производителя + информация, которая может быть перепрограммирована);

команды стирания;

команды записи.

Алгоритмы стирания и записи сознательно усложнены, чтобы не было случайной записи или стирания. Требуется выполнить несколько циклов записи и чтения.

Некоторые схемы флэш-памяти имеют буферную область, имеется сектор, в котором записана программа, с которой в дальнейшем можно будет загрузиться. Алгоритм перезаписи в буферную зону усложнен.

Видеосистема

Состав: - монитор, периферийные устройства; - видеоконтроллер; - ПО.

Графический конвейер.

Видеосистема требует больших вычислительных затрат. ГК используется для формализации описания "вывод изображения на устройство отображения". Различается:

текстовая информация; - 2-хмерное изображение; - 3-хмерное изображение.

Этапы формирования изображения:

обработка графических примитивов – пересчет их относительных (абсолютных координат) к точке наблюдения и к сцене. Пересчет должен происходить с частотой смены кадров;

расчет цветовых элементов примитивов в зависимости от метода и используемой модели освещенности;

на основе рассчитанных примитивов отсечение невидимых частей объектов;

растеризация – раскраска в формате устройства отображения.

Используются различные приемы, позволяющие ускорить эти этапы. 1 из них – использование текстур, наборов текстур. Текстура – объект, который может использоваться в качестве раскраски. Они могут быть 2-d и 3-d и позволяют быстро наложить на объект образ.

Средства создания и отображения изображения.

Здесь единство аппаратного и ПО. Существуют стандарты на формирование изображений, которые находят свое применение в виде стандартных правил.

С истемыOpenGL

и

DirectX

используются

визуализации игровых ситуаций и

разработаны на основе других стандартов.

истемыOpenGL

и

DirectX

используются

визуализации игровых ситуаций и

разработаны на основе других стандартов.

28.04.01

Аппаратно-программные средства для OpenGL.

Стадии создания и вывода изображения:

G – создание структуры прикладных данных;

T – создание графических образов, упорядочение графических, прикладных данных;

X – преобразование графических объектов, привязка их к реальным координатам (относительно наблюдателя);

R – растеризация объектов сцены, отображение их всех на экране в нужном ракурсе, удаление невидимых объектов;

D – отображение, вывод изображения на экран с частотой регенерации изображения (24 к/сек).

1![]() – прикладная генерация объектов –

генерация всех примитивов;

– прикладная генерация объектов –

генерация всех примитивов;

2 – прикладной обход – создание объектов;

3 – дисплейный список – уже существующие примитивы;

6 - вычисление;

4 – сборка примитивов;

8 – пиксельные операции на основе примитивов (верх. – вычисляются объекты, ниж. - собираются);

9 – память текстур;

5 – растеризация (связана с наложением текстур);

7 – операции с фрагментами изображения. Этот блок позволяет совмещать объекты, размещенные в разных местах;

10 – буфер кадра – работает с дисплеем.

Эти этапы соответствуют ГК.

При этом аппаратно выполняется только буфер кадра. GTXR-D (прогр.-апп.) – простейшая реализация видеоконтроллера.

Если есть аппаратные средства (ускоритель), выполняющие операции 5,9,7 (см. выше) => это выполняет аппаратура. Современные ускорители выполняют D и R. Развитие техники постепенно расширяет границы аппаратной реализации. Реализацию X и T аппаратно выполняют специализированные графические системы.

Система прерываний

Служит для инициации различных процессов. Прерывания формируются системными устройствами, самим процессором, периферийными устройствами (вв./выв.). Инициатор запроса выставляет сигнал-запрос. В системе должно быть устройство – контроллер прерываний, который эти запросы воспринимает. Далее начинает работать механизм приоритетов:

между запросом и текущим состоянием системы;

между самими запросами (связано с текущим состоянием системы).

Бывают различные запросы: по переключению или по уровню. По переключению надо учитывать, что импульс имеет некоторую длительность, линия может использоваться только одним инициатором => каждому источнику требуется свой символ. В случае запроса по уровню линия может использоваться несколькими инициаторами, но это не позволит определить источник запроса (это используется в PCI). Но это экономит число линий запроса прерываний. Сейчас этот способ (по уровню) считается прогрессивным. От контроллера прерываний сигнал идет процессору. Если он "согласен", то переходит к подпрограмме прерывания.

Алгоритм:

сохранение всех параметров текущего процесса, чтобы к нему можно было вернуться по завершению подпрограммы прерывания: рабочие регистры, служебные регистры, регистры управления (в системах с разделением памяти);

п

роцессору

(его системе дешифрации команд) передается

вектор новой подпрограммы прерываний.

Самый простой способ – контроллеру

прерываний генерировать адрес

подпрограммы прерывания, но это

невозможно (все программы в памяти

"перемещаются"). Вектор указывает

на ячейку памяти, где находится адрес

подпрограммы прерывания. ПрерыванияBIOS

– 256 ячеек. Для ускорения процесса

таблица векторов располагается в кэше.

роцессору

(его системе дешифрации команд) передается

вектор новой подпрограммы прерываний.

Самый простой способ – контроллеру

прерываний генерировать адрес

подпрограммы прерывания, но это

невозможно (все программы в памяти

"перемещаются"). Вектор указывает

на ячейку памяти, где находится адрес

подпрограммы прерывания. ПрерыванияBIOS

– 256 ячеек. Для ускорения процесса

таблица векторов располагается в кэше.

После выполнения подпрограммы возвращаются все параметры прерванного процесса. Но здесь происходит проигрыш при восстановлении конвейера.

Среднее время реагирования на инициализацию и выполнение процесса для прерываний меньше, чем при программном опросе.

ПДП

Это доступ без участия процессора между устройствами вв./выв. и памятью, между отдельными блоками памяти.

Центральный процессор и др. устройства должны уметь отключаться при ПДП. Для этого – запрос и ответ. Процесс инициируется по сигналу ПУ. Как только разрешен ПДП, шиной начинает управлять контроллер ПДП. При этом отключается адресация ПУ. При обмене между блоками памяти используется 2 адреса – источник и приемник. Этот процесс инициируется процессором. Запускать обмен может таймер: цикл чтения и цикл записи (2 цикла). Так было раньше почти во всех процессорах. В настоящее время, как такового, контроллера ПДП почти не стало.

В режиме ПДП "степень свободы" больше.