- •Введение

- •1 Основы микропроцессорной техники

- •1.1 Классификация команд и архитектура ЭВМ

- •1.2 Секционный микропроцессор.

- •1.3 Однокристальный микропроцессор.

- •1.4 Микропроцессорный модуль.

- •3.1 Тип кода операции с dst и rsc

- •3.2 Тип кода операции с dst. Группа коман MOV

- •4 Организация стековой памяти

- •5 Команды сдвигов и приращений.

- •5.1 Команды приращений

- •5.2 Команды сдвига

- •6 Арифметико-логические команды

- •6.1 Команды сложения

- •6.2 Команда сложения с учетом переноса

- •6.3 Операция вычитания

- •6.4 Команда вычитания с учетом заема

- •6.5 Команда логической функции ИЛИ

- •6.6 Команда логической функции И

- •6.7 Команда «Исключающая ИЛИ»

- •Внутриразрядная сумма = 0

- •6.8 Команда сравнения — компарации

- •7 Команды ветвления и переходов

- •7.1 Команды ветвления

- •7.2 Команды перехода

- •8.1 Внутрисегментные переходы

- •8.2 Межсегментные переходы

- •10 Цепочные команды

- •11 Другие одиночные команды

- •13.1 Процедура прерываний и команды прерываний

- •Адрес

- •13.2 Режимы работы ПКП

- •13.3 Программирование ПКП

- •14 Параллельный интерфейс

- •15 Последовательный интерфейс

- •15.1 Антология последовательного интерфейса

- •15.3 Описание регистров 8250 и программирование

- •Регистр управления линией

- •Регистр управления модемом

- •15.4 Порядок инициализации 8250

- •16 Программируемый таймер

- •16.7 Временные диаграммы таймера

- •16.8 Программирование таймера

- •Чтение счетчика канала 2

- •16.9 Чтение содержимого счетчиков

- •16.10 Таймер на системной плате IBM PC

- •17 Клавиатурный интерфейс

- •18. Заключение

- •Приложение А

- •Действие

- •Сегментный регистр

- •Действие команды

- •Действие команды

- •Действие команды

- •SAHF — сохранение <AH> в F

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Действие команды

- •Команда – действие команды

- •Команда – действие команды

- •Команда – действие команды

- •Команда – действие команды

- •Команда – действие команды

- •Команда – действие команды

- •Команда – действие команды

Решение.

MOV DX,ОЗFD ;DX := 3FD — адрес порта В ;

IN AL,DX. ; ввести в AL МП из порта В байт данных.

2) Вывод.

а) Ассемблер: OUT DX,AL; комментарий: вывести из регистра AL МП байт данных в порт, адрес которого взять из DX.

б) машинный код состоит только из КОП: КОП = ЕЕ.

Пример применения этой команды можно не приводить, так как по существу он не отличается от примера 1. Таким образом, выбор команд ввода-вывода невелик, но достаточен.

13Обслуживание прерываний. Контроллер прерываний

13.1Процедура прерываний и команды прерываний

Что должен делать микропроцессор, обнаружив на своем входе INT сигнал «1» (смотрите рисунок 3 в главе 2)? Он должен:

во-первых, закончить текущую команду, на которой его «прихватил» запрос: INT = 1;

во-вторых, если флаг IF был равен «1» (разрешение аппаратного прерывания), то вместо сигналов чтения -MEMRD или -IORD микропроцессор вырабатывает сигнал чтения: -INTA.

Что должен прочитать МП этим сигналом с шины данных системной магистрали? По логике событий — КОП следующей команды. Но он вырабатывает не сигнал чтения ячейки ЗУ –MEMRD, а сигнал - INTA. Вместе с тем, МП посредством этого сигнала будет загружать КОП следующей команды, и это должна быть первая команда подпрограммы, которая обслуживает прерывание. Следовательно, источником этой команды должен быть необычный интерфейсный элемент, для которого сигнал –INTA является сигналом чтения (ввода). Вот этим элементом и является контроллер прерываний. Именно он обслуживает аппаратную часть процедуры прерывания. Но прежде, чем рассмотреть контроллер, давайте еще раз вернемся к процедуре прерывания.

МП 8086 поддерживает (как и все другие микропроцессоры) программное и аппаратное прерывание.

Программное прерывание инициируется по команде прерывания. а) Ассемблер: INT n, где n — однобайтовый вектор перехода,

указывается в H-коде.

б) Машинный код — 2 байта: 1-й байт — КОП, 2-й байт — вектор.

КОП = CD. Вектор = 0...FF (0...25510).

Что делает микропроцессор, обнаружив команду INT n?

1)Запрещает дальнейшее аппаратное прерывание: IF = 0 (то есть, выполняет скрытую команду CLI).

2)Загружает последовательно в стек:

69

Stack:=<F> - |

загружает в стек PSW (содержимое регистра флагов); |

Stack:=<CS> - |

загружает в стек содержимое сегментного регистра |

CS; Stack:=<IP> - загружает в стек текущий адрес, то есть адрес следующей команды прерванной программы.

3) Начиная с адреса CS:EA, где CS = 0000, EA = 4×n — считывает 2 слова, (4 байта), первое (младшее) из которых попадает в IP, а второе (старшее) — в CS.

Таким образом, следующая команда будет выбираться, начиная с адреса CS:IP, который установило программное прерывание INT n .

Следовательно, в задачу пользователя входит:

а) знать, в каком сегменте и с какого адреса расположена подпрограмма, которая вызывается прерыванием INT n;

б) загрузить в ячейки памяти в нулевом сегменте, начиная с EA = 4×n, слово адреса и слово сегмента начала подпрограммы.

Пример 1 – пусть подпрограмма должна вызываться прерыванием INT 2F, и эта подпрограмма располагается в ОЗУ, начиная с адреса: CS=1570, IP = 0100.

Ответ:

Вычисляем адрес вектора : EA = 2F×4=BC.

Располагаем адрес начала подпрограммы по адресу вектора:

Адрес |

IP |

|

CS |

||

00BC |

|

00BD |

00BE |

00BF |

|

Данные |

00 |

|

01 |

70 |

15 |

Естественный вопрос: как вернуться из программного прерывания? Команду безадресного перехода RET FAR здесь можно использовать, но к ней необходимо добавлять команду POPF, чтоб восстановить и регистр флагов F, и указатель стека. Такой возврат обеспечивается специальной командой безадресного перехода, которая поглощает в себя эти две команды:

а) Ассемблер: IRET; б) КОП = CF. Действие команды:

IP := <Stack> ;возврат адреса из стека; CS := <Stack> ;возврат сегмента из стека; F := <Stack> ;возврат флагов из стека.

Следовательно, если подпрограмма вызывается программным прерыванием, а не командой CALL, то она должна заканчиваться командой IRET.

Теперь снова вернемся к аппаратному прерыванию. Итак, микропроцессор сигналом чтения -INTA требует у контроллера прерываний КОП следующей команды. По всей видимости, это должна быть команда программного прерывания INT n с кодом операции CD.

70

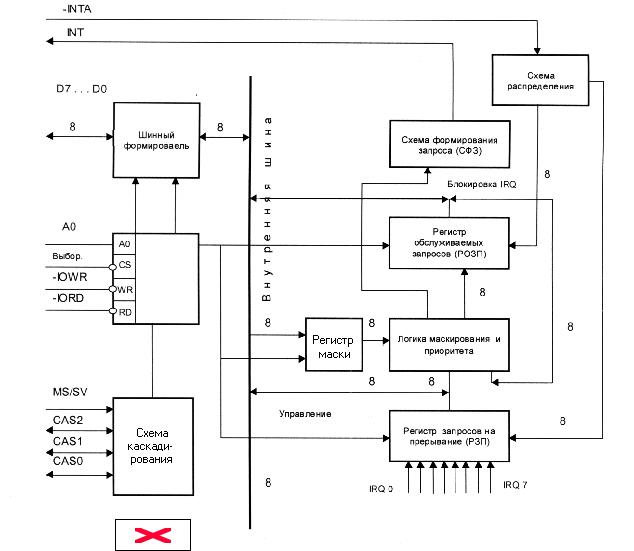

Этот код «зашит» технологически в контроллере прерываний 8259. А вектор n программируется при инициализации контроллера прерываний (ПКП) . Ознакомимся с архитектурой ПКП 8259, приведенной на рисунке 10. При этом опустим разъяснения относительно сигналов системной магистрали, считая, что это уже пройденный этап.

Шинный формирователь осуществляет двунаправленное движение данных:

-при -IORD=0: T=0 и шинный формирователь осуществляет направление справа налево;

-при -IOWR=0: T=1 и шинный формирователь осуществляет

направление слева направо.

Таким образом коммутируется внутренняя шина данных (ВШД) с шиной данных системной магистрали. Но это при условии, что -CS = 0, что приводит к ОЕ = 1; а иначе шинный формирователь вообще отключен от системной шины. Это общий принцип управления встроенным в интерфейсные контроллеры шинным формирователем.

Схема управления записью-чтением осуществляет генерацию необходимых для внутренних элементов ПКП управляющих сигналов.

Теперь по существу функционирования ПКП. Относительно запросов на прерывание IRQi он представляет собой двухступенчатый регистр — систему со шлюзом. Всего реализовано IRQi для 8 запросов. Они неравнозначны: максимальный приоритет у IRQ 0, минимальный - у IRQ 7.

1-ый этап. Сначала передним фронтом (или потенциалом) IRQi устанавливается соответствующий разряд регистра запросов на прерывание (РЗП) — открылись 1-ые ворота шлюза. Сигнал с выхода РЗП этого разряда через это

Рисунок 10 —Архитектура ПКП 8259

71

своеобразное сито — логику маскирования и приоритета — попадает на вход INT МП (INT=1).

2-ой этап. МП первым сигналом чтения -INTA считывает из ПКП на шину данных КОП = CD и одновременно переписывает соответствующий запрос из РЗП в регистр обслуживаемых запросов на прерывание (РОЗП). Соответствующий выход РОЗП, установившись в «1», блокирует прохождение INT через логику маскирования и приоритетов как собственного запроса, так и более низких по приоритету. Резюме: 1-ые ворота закрылись, INT — исчез (INT=0).

3-ий этап. МП, распознав по КОПу, что команда двухбайтовая, вырабатывает еще один сигнал чтения -INTA, который считывает из ПКП на шину данных вектор и одновременно сбрасывает соответствующий разряд РЗП в «0», который вызвал прерывание INT. Итак, первая ступень — в исходное состояние. Можно зафиксировать: аппаратная часть прерывания закончилась, но в результате:

1)флаг IF = 0 , то есть аппаратное прерывание МП заблокировано (запрещено);

2)IRQi , вызвавший прерывание, тоже заблокирован по входу i и по всем остальным, которые ниже по приоритету.

4-ый этап. Разблокировка этой двойной блокировки всегда производится программно в конце подпрограммы, вызванной прерыванием.

Снятие блокировки со входа INT МП производится командой STI (IF = 1 — разрешение аппаратного прерывания).

Сброс соответствующего разряда РОЗП осуществляется записью в

ПКП при А0=0 (рисунок 10), например, кода «20» (20 — код команды сброса того разряда, который последним вызвал прерывание).

2-ые ворота шлюза открылись — процесс прерывания завершен. Пример 2 — Допустим, ПКП выбирается (с помощью дешифратора

адреса) следующими кодами :

OFO (AO=0) и OF1 (AO=1);

Тогда заключительная часть подпрограммы, вызванной прерыванием, будет выглядеть следующим образом:

. . . . . . . . . . . . . . . . . . . . . . . . .

STI |

; разрешение прерываний микропроцессору; |

MOV DX,OOFO ; адрес ПКП для А0=0 в DX; |

|

MOV AL,20 |

; код завершения обработки прерывания ПКП — |

в AL, |

|

OUT DX,AL |

; а оттуда в ПКП. |

IRET |

; возврат в программу. |

На рисунке 10 (архитектура ПКП) имеется элемент, именуемый регистром маски. Маска устанавливается («1»—маскирование IRQi)

72

записью в ПКП при АО=1 соответствующего байта. Маску можно прочитать по тому же адресу, то есть при АО=1.

Пример 3 — составить маску для только что рассмотренного примера 2 таким образом, чтоб разрешить прерывание только по запросам IRQO и IRQ6:

Ответ: Составляем слово маски, «закрывая» все, кроме D6, D0:

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

┌───┬───┬───┬───┬───┬───┬───┬───┐ |

|||||||

Маска: │ 1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 │ |

|

|

└───┴───┴───┴───┴───┴───┴───┴───┘ |

|||||||

|

└───────────┘ |

└───────────┘ |

||||||

Н-код |

= |

|

B |

|

|

E |

|

|

|

Составим фрагмент программы маскирования ПКП с адресами |

|||||||

выборки из примера 2: |

|

|

|

|

|

|||

MOV DX,00F1 |

; адрес ПКП для АО=1 в DX; |

|

||||||

MOV AL,BE |

; маску BE (IRQ 0, IRQ 6 — разрешить) в AL, |

|||||||

OVT DX,AL |

; а затем оттуда в ПКП — в регистр маски. |

|||||||

|

Примечание – В начале работы, в момент подачи питания на ПКП |

|||||||

все IRQ демаскируются, все разряды РЗП и РОЗП сбрасываются в «0» и |

||||||||

устанавливается |

исходный |

приоритет: IRQ |

0 — |

высший, IRQ 7 — |

||||

низший (дно). |

|

|

|

|

|

|

|

|

|

Следующий элемент архитектуры ПКП (рисунок 10) называется: |

|||||||

«Схема каскадирования». Он выполняет функции расширителя числа запросов на прерывание. Дело в том, что если не хватает 8 входов IRQ, то микросхемы можно каскадировать — до 8 штук, и число векторов довести до 8 x 8 = 64.

На практике такое редко встречается, а вот каскад из двух ПКП реализован в IBM PC/АТ. Как это делается — в данном пособии не рассматривается. Это совершенно не принципиальный вопрос, а скорее узкотехнический.

А теперь обратимся к программированию ПКП. Некоторые элементы этого процесса уже были представлены в примерах 2 и 3. Но в целом процесс программирования ПКП достаточно сложен и состоит из трех блоков.

1) блок инициализации (настройка режима и загрузка векторов и шага векторов);

2)блок команд окончания (завершения) прерывания;

3)блок команд обработки по опросу (без сигнала INT).

Чтобы иметь возможность работы с контроллером по минимуму, необходимо знать:

а) как накладывать маску (или прочитать ее); б) как завершать прерывание (частный случай: команда 20 при

А0=0).

73