- •Управляющие эвм, требования к ним по сравнению с пк

- •Датчики угла поворота вала

- •Упрощенный критерий оценки эвм, блок-схема «машины фон-Неймана», сравнение с Гарвардской архитектурой

- •2. Синхронный двигатель (сравнение с асинхронным)

- •Логарифмическая шкала, децибелы

- •2. Полевые транзисторы (field effect transistors - fet)

- •Сигнальные процессоры и плк

- •1. Принцип действия кэШа, многоуровневое кэширование, регистры процессора

- •Функционирование

- •1. Память эвм

- •1. Предвыборка данных, принцип повышения скорости передачи информации для памяти ddr2, ddr3

- •2.Полевые транзисторы с управляющим p-n переходом

- •1. Частотно-регулируемый электропривод переменного токa

- •2. Числовое программное управление (чпу)

- •2. Система пид

- •1. Компьютерные сети в сау (profibus и can)

- •2. Акустическое оформление громкоговорителей (колонки)

- •1. Система scada

- •2. Сквозной акустический такт

- •2. Терморегулирование

- •2. Силовые импульсные цепи

- •1. Основные показатели усилителя

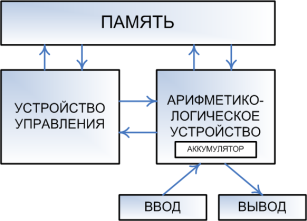

Упрощенный критерий оценки эвм, блок-схема «машины фон-Неймана», сравнение с Гарвардской архитектурой

Количественной оценкой надежности ЭВМ, содержащей элементы, отказ которых приводит к отказу всей машины, могут служить следующие показатели:

- вероятность безотказной работы за определенное время при данных условиях эксплуатации;

- наработка ЭВМ на отказ;

- среднее время восстановления машины и др.

Архитектура

фон Неймана (англ. von

Neumann

architecture) —

широко известный принцип совместного

хранения программ и данных впамяти

компьютера.

Отличительной особенностью архитектуры

фон Неймана является то, что инструкции

и данные хранятся в одной и той же

памяти.

Этапы цикла выполнения:

Архитектура

фон Неймана (англ. von

Neumann

architecture) —

широко известный принцип совместного

хранения программ и данных впамяти

компьютера.

Отличительной особенностью архитектуры

фон Неймана является то, что инструкции

и данные хранятся в одной и той же

памяти.

Этапы цикла выполнения:

Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения;

Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности;

Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её;

Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды;

Снова выполняется п. 1.

Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства). Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм полезной работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода — тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки аппаратного прерывания. Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются: 1. Хранилище инструкций и хранилище данных представляют собой разные физические устройства. 2. Канал инструкций и канал данных также физически разделены. Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

выборку двух операндов,

выбор инструкции и её выполнение,

и, наконец, сохранение результата.

Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера. В Гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не требуется иметь общими. В частности, ширина слова, тайминги, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут хранится в памяти только для чтения, в то время как, для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных (поскольку данные обычно могут подгружатся с внешней или более медленной памяти). Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

Архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете. Отличие от архитектуры фон Неймана

В чистой архитектуре фон Неймана процессор одномоментно может либо читать инструкцию, либо читать/записывать единицу данных из/в памяти. То и другое не может происходить одновременно, поскольку инструкции и данные используют одну и ту же системную шину.

А в компьютере с использованием гарвардской архитектуры процессор может читать инструкции и выполнять доступ к памяти данных в то же самое время, даже без кэш-памяти. Таким образом, компьютер с гарвардской архитектурой может быть быстрее (при определенной сложности схемы), поскольку доставка инструкций и доступ к данным не претендуют на один и тот же канал памяти.

Также машина гарвардской архитектуры имеет различные адресные пространства для команд и данных. Так, нулевой адрес инструкций — это не то же самое, что и нулевой адрес данных. Нулевой адрес инструкций может определятся двадцатичетырехбитным значением, в то время как нулевой адрес данных может выглядеть как восьмибитный байт, который не являются частью этого двадцатичетырехбитного значения.