- •Декомпозиция задачи ввода данных в озу

- •Структуры данных

- •Разработка структуры данных программы для ввода данных в озу

- •Алгоритмизация программы

- •Подходы к алгоритмизации

- •Иерархическая организация алгоритма

- •Алгоритмизация программы для ввода данных в озу

- •1. Модуль "Тестовый контроль озу по шд" (dTstContr)

- •2. Модуль "Тестовый контроль озу по ша" (aTstContr)

- •3. Модуль "Вывод сообщений об ошибках" (ErMesOut)

- •4. Модуль "Ввод режимов" (ModeInput)

- •5. Модуль "Вывод сообщения о типе ввода" (InTpMesOut)

- •6. Модуль "Ввод с клавиатуры" (KbdInput)

- •7. Модуль "Контроль ввода с клавиатуры" (KbdInContr)

- •8. Модуль "Преобразование очередной цифры" (NxtDigTrf)

- •9. Модуль "Формирование информации" (InfoForm)

- •10. Модуль "Формирование массивов отображения" (DispForm)

- •11. Модуль "Вывод числовой информации" (NumInfOut)

- •12. Модуль "Функциональная подготовка" (FuncPrep)

- •3.4.4. Кодирование программы

- •Реализация логических конструкций структурного программирования

- •Кодирование программы для ввода данных в озу

- •3.4.5. Тестирование и отладка программы

- •3.4.6. Занесение программы на рабочий носитель

- •3.4.7. Оформление документации на программу

- •3.5. Проектирование аппаратных средств

- •3.5.1. Схемотехническое проектирование процессора

- •3.5.2. Схемотехническое проектирование памяти

- •Банкирование памяти

- •Организация банков памяти

- •Проектирование запоминающих устройств

- •3.5.3. Схемотехническое проектирование интерфейса

- •Организация ввода/вывода данных

- •3.5.4. Тестирование и настройка аппаратных средств

- •Тестирование статическими сигналами

- •Свободный прогон микропроцессора

- •3.6. Комплексная отладка микропроцессорной системы

- •Заключение

- •Список рекомендуемых источников

Проектирование запоминающих устройств

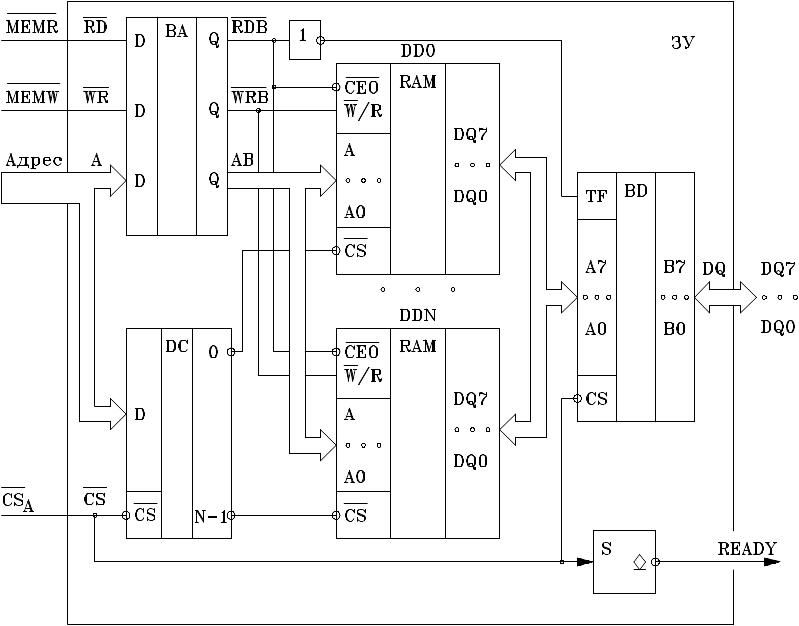

Проектирование ПЗУ и ОЗУ осуществляется на основе ИМС ЗУ с накопителями соответствующего типа. При этом в состав ЗУ в общем случае входят несколько ИМС накопителей. Обобщенная схема ЗУ приведена на рис. 3.51.

Количество N ИМС, необходимых для построения ЗУ, определяется требуемым объемом памяти Vmem в байтах и объемом накопителя V0 в используемой ИМС в соответствии с формулой N = 1 + ent(Vmem 1)/V0.

Рис. 3.51. Обобщенная схема запоминающего устройства

Все

ИМС накопителей (DD1DDN)

объединены по входам адреса, обращения

и выводам данных. При этом входы адреса

через буфер адреса BA подключаются к

младшим линиям входной шины адреса,

входы разрешения выхода

![]() к линии

к линии

![]() ,

а вход записи

,

а вход записи

![]() /R

к линии

/R

к линии

![]() шины

управления МПС. Выводы данных ИМС

накопителей через буфер данных BD

подключаются к шине данных МПС. Буферы

адреса и данных служат для приведения

нагрузки со стороны проектируемого ЗУ

на каждую линию системной шины к

единственному входу.

шины

управления МПС. Выводы данных ИМС

накопителей через буфер данных BD

подключаются к шине данных МПС. Буферы

адреса и данных служат для приведения

нагрузки со стороны проектируемого ЗУ

на каждую линию системной шины к

единственному входу.

Буфер адреса BA является однонаправленным и не требует никакого управления. Он может быть реализован либо на регистрах ИР82, либо на буферах ВА86 в соответствующем включении.

Буфер данных BD является двунаправленным и требует управления выборкой и направлением передачи. При этом буфер данных включается таким образом, чтобы при отсутствии обращений к ЗУ он был подключен к шине данных входами и лишь при выполнении операции чтения разворачивался к ней выходами. Это упрощает согласование ЗУ с шиной при различных переключениях.

Для выбора одной из множества параллельно включенных ИМС накопителей служит адресный дешифратор, декодирующий старшие разряды входной шины адреса. Вход выборки этого дешифратора совместно с входом выборки буфера данных являются входом выборки A ЗУ в целом.

Если быстродействие используемых ИМС накопителей недостаточно для работы в темпе процессора, то в состав ЗУ должен включаться одновибратор S, предназначенный для формирования флага готовности к обмену. Этот одновибратор возбуждается сигналом выборки ЗУ и формирует импульс с нулевым уровнем активности, длительность которого определяется временем выборки адреса ИМС накопителей. Флаг готовности ЗУ должен подключаться к входу READY процессора, что обеспечит введение для МП состояний ожидания на требуемый интервал времени при каждом обращении к ЗУ.

Схема,

приведенная на рис. 3.51, полностью

соответствует схеме ОЗУ. Схема ПЗУ

является частным случаем этой схемы.

Действительно, в ней не будет использоваться

лишь сигнал записи

![]() ,

т. к. операция записи недопустима для

ПЗУ.

,

т. к. операция записи недопустима для

ПЗУ.

При

построении ОЗУ на ИМС К537РУ8, не имеющих

входа разрешения выхода

![]() ,

схема по рис. 3.51 должна быть несколько

изменена. Изменение заключается в том,

что выборка адресного дешифратора DC и

буфера данных BD должна осуществляться

сигналом CS, сформированным по формуле

CS = CSA·(MEMR

MEMW).

,

схема по рис. 3.51 должна быть несколько

изменена. Изменение заключается в том,

что выборка адресного дешифратора DC и

буфера данных BD должна осуществляться

сигналом CS, сформированным по формуле

CS = CSA·(MEMR

MEMW).

В простейшем случае (при условии соблюдения гальванического и емкостного согласования ЗУ с системной шиной МПС) буферы адреса и данных могут отсутствовать.