- •1.Цепи ускоренного переноса.

- •2.Системы и принцип работы озу.

- •3.Схема мультиплексора и способы их наращивания. Схема демультиплексора и способы их наращивания.

- •5. Классификация и назначение преобразователей кодов; преобразователи кодов прямого в обратный и дополнительный; преобразователи десятичного в двоично-десятичный.

- •6. Триггеры. Схемотехника асинхронного и синхронного rs-триггеров, счетного t-триггеров, d-триггеров, jk-триггеров.

- •7. Принцип построения и работы регистров параллельного действия и регистров последовательного действия.

- •10.Организация и принцип работы постоянных запоминающих устройств

- •9.Преобразователи цап и ацп

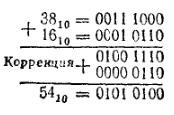

5. Классификация и назначение преобразователей кодов; преобразователи кодов прямого в обратный и дополнительный; преобразователи десятичного в двоично-десятичный.

Под преобразованием кодов понимается преобразование n-разрядных двоичных чисел, представляющих информацию в одном заданном коде, в m-разрядные двоичные числа, представляющие эту информацию в другом коде.

Микросхемы преобразователей кодов (англ. сonverter) служат для преобразования входных двоичных кодов в выходные двоично-десятичные и наоборот. Они используются довольно редко, так как применение двоично-десятичных кодов ограничено узкой областью, например, они применяются в схемах многоразрядной десятичной индикации. К тому же при правильной организации схемы часто можно обойтись без преобразования в двоично-десятичный код, например, выбирая счетчики, работающие в двоично-десятичном коде. Преобразование двоично-десятичного кода в двоичный встречается еще реже.

Знак «плюс» изображается как 0, а «минус» - 1.

Д воично-

десятичное кодирование-

кодирование, при котором каждая десятичная

цифра представляется группой двоичных

цифр. Число битов в таких группах строго

фиксируется (их должно быть не менее 4)

с сохранением всех левых нулевых

разрядов. При сложении двух чисел в коде

прямого замещения необходимо добавить

корректирующее слагаемое 610=

01102.

воично-

десятичное кодирование-

кодирование, при котором каждая десятичная

цифра представляется группой двоичных

цифр. Число битов в таких группах строго

фиксируется (их должно быть не менее 4)

с сохранением всех левых нулевых

разрядов. При сложении двух чисел в коде

прямого замещения необходимо добавить

корректирующее слагаемое 610=

01102.

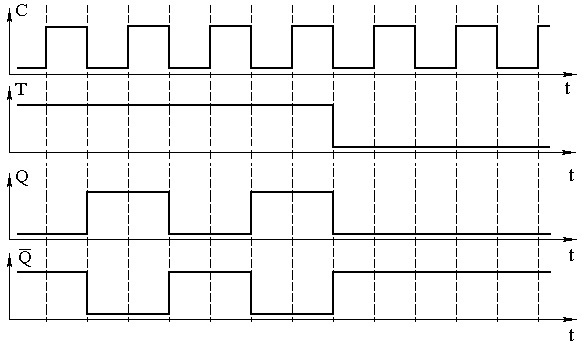

6. Триггеры. Схемотехника асинхронного и синхронного rs-триггеров, счетного t-триггеров, d-триггеров, jk-триггеров.

Триггер - основной элемент памяти, используемый для хранения единицы информации. Как правило, схема триггера помимо элемента памяти, хранящего бит информации, имеет дополнительные схемы управления-ключи, с помощью которых создаются определенные условия для записи и хранения информации в ЭП.

![]()

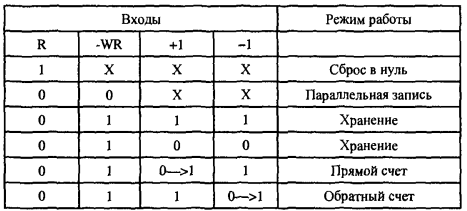

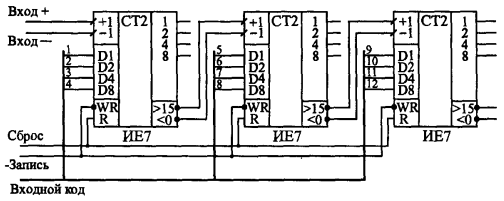

7. Принцип построения и работы регистров параллельного действия и регистров последовательного действия.

Регистр - узел ЭВМ, предназначенный для приема, хранения и передачи информации в другие узла в процессе выполнения операций в вычислительных устройствах. Регистр представляет собой совокупность триггеров, число которых соответствует количеству разрядов размещаемой в нем информации. Наличие прямых и инверсных выходов позволяет использовать такое устройство для получения кодов чисел хранимой информации. По способу приема и передачи информации регистры подразделяются на параллельные (прием и передача n-разрядного кода производятся параллельно под воздействием управляющего сигнала), последовательные (прием и передача n-разрядной информации производится последовательно разряд за разрядом, при этом внутри регистра возможны однонаправленный сдвиг информации из разряда в разряд влево или вправо и двунаправленный (реверсивный) сдвиг в зависимости от условий как вправо, так и влево) и последовательно-параллельные (прием и передача n-разрядной информации могут производиться в последовательном, параллельном и смешанном режимах).

Регистр параллельного действия может работать в следующих режимах:

- предварительная установка;

- запись информации в триггеры регистра;

- хранение ранее записанной информации;

- чтение информации из регистра.

Регистр последовательного действия: имеет один вход для последовательного ввода информации. Межразрядные связи соединяют входы триггеров младших разрядов с входами триггеров старших разрядов, что позволяет осуществлять последовательное продвижение информации из разряда в разряд под воздействием управляющих синхроимпульсов (C).