- •Организация эвм

- •Принципы Неймана построения эвм. Элемент Неймана. Автомат Неймана.

- •Структура классической эвм. Назначение и взаимосвязь ее основных устройств.

- •Машина Тьюринга.

- •Команда и ее формат. Взаимосвязь формата команды и основных параметров эвм

- •Системы кодирования команд. Структура одно-, двух-, трех-, четырехадресной эвм. Естественный и принудительный порядок выполнения программы.

- •Стековая память. Структура безадресной эвм.

- •Цикл выполнения команды. Взаимодействие основных узлов и устройств эвм при автоматическом выполнении команды в трехадресной эвм.

- •Основы схемотехнической реализации эвм

- •Системы логических элементов. Основные параметры логических элементов. Условно-графические обозначения основных логических элементов.

- •Этапы проектирование логических схем на элементах “и-не”, “или-не”. Быстродействие логических схем.

- •Д ешифратор: назначение, таблица истинности. Условно-графическое обозначение.

- •Триггер. Назначение. Классификация триггерных схем.

- •Асинхронный двоичный счетчик. Назначение. Временная диаграмма работы. Оценка быстродействия.

- •Регистры. Назначение. Регистр хранения. Регистр сдвига. Условно-графическое обозначение. Регистр хранения

- •Устройства эвм

- •Устройство управления (уу): назначение, принципы построения.

- •Структурная схема уу с жесткой логикой. Реализация датчика сигналов на счетчике с дешифратором и на сдвиговом регистре.

- •Структурная схема микропрограммного уу.

- •Запоминающие устройства (зу): назначение, основные параметры. Иерархическая структура зу современных эвм.

- •Конвейерная организация работы микропроцессора. Ступени конвейера.

- •Оценка производительности микропроцессора при конвейерной организации работы.

- •Типы конфликтов в конвейере и методы уменьшения их влияния на снижение производительности микропроцессора.

- •Недостаточное дублирование некоторых ресурсов.

- •Система управления памятью. Статическое и динамическое распределение памяти. Страничная организация памяти. Виртуальная память.

- •Система прерываний. Назначение. Последовательность действий компьютера при обработке запросов прерываний.

- •Мультипрограммная эвм

- •Мультипрограммный режим работы эвм. Процесс и ресурс в мультипрограммных эвм.

- •Структура мультипрограммной эвм и особенности ее функционирования. Основные характеристики работы эвм в мультипрограммном режиме.

- •Счет1 - ввод - счет2 - вывод.

- •Одноочередные дисциплины распределения ресурсов в мультипрограммных эвм: fifo, lifo, круговой циклический алгоритм.

- •Многоочередная дисциплина распределения ресурсов в мультипрограммных эвм и ее модификации.

- •Режимы работы мультипрограммных эвм: пакетный, разделения времени, реального времени.

- •Организация работы персональной эвм

- •Структура персональной эвм.

- •Структура микропроцессора 8086, состав и назначение его основных блоков.

- •Организация памяти в ibm pc: физическое адресное пространство, адрес байта, слова, двойного слова.

- •Символическое и машинное представление команд: назначение, область применения.

- •Формат двухоперандной команды ibm pc общего вида. Назначение полей команды.

- •Режимы адресации операндов в ibm pc.

- •Формирование физического адреса в ibm pc в реальном режиме работы.

- •Формат команды ibm pc, использующей непосредственный операнд. Назначение полей команды.

- •Структура 32-разрядного микропроцессора, состав и назначение его основных блоков. Структура 32-разрядного универсального микропроцессора

- •Обработка прерываний в персональной эвм.

- •Порядок обработки прерываний

- •Контроллер приоритетных прерываний. Назначение. Порядок работы. Контроллер приоритетных прерываний

- •Каскадное включение контроллеров приоритетных прерываний

- •Защита памяти в мультипрограммных эвм. Назначение. Классические методы защиты Защита отдельных ячеек памяти. Метод граничных регистров. Метод ключей защиты памяти.

- •Организация защиты памяти в персональной эвм. Защита при управлении памятью. Защита по привилегиям.

- •Ввод-вывод информации в эвм. Проблемы организации ввода вывода и пути их решения.

- •Основные интерфейсные сигналы шины isa.

Организация работы персональной эвм

Структура персональной эвм.

Структура персональной ЭВМ.

Персональная ЭВМ типа IBM PC включает в себя МП, ОП, УВВ, объединенные между собой системной шиной.

МП предназначен для выполнения арифметических и логических операций и управления взаимодействием блоков компьютера.

ОП хранит операнды и программу во время выполнения.

УВВ обеспечивают обмен информацией между МП и ОП (ядром компьютера) и средством ввода и отображения данных.

Персональная ЭВМ строится по магистрально-модульному принципу, при котором все блоки компьютера связываются между собой системной шиной, предназначенной для обмена данными, адресной и управляющей информацией между составными частями ЭВМ.

Как правило, при такой организации в любой момент может быть установлена связь только между двумя модулями ЭВМ. Системная шина определяет общий порядок обмена между любыми блоками компьютера, а также максимальное количество используемых УВВ.

СШ включает в себя шину адреса (ША), шину данных (ШД) и шину управления (ШУ).

Специфика каждого конкретного блока учитывается особыми УУ – контроллерами, входящими в состав этих блоков.

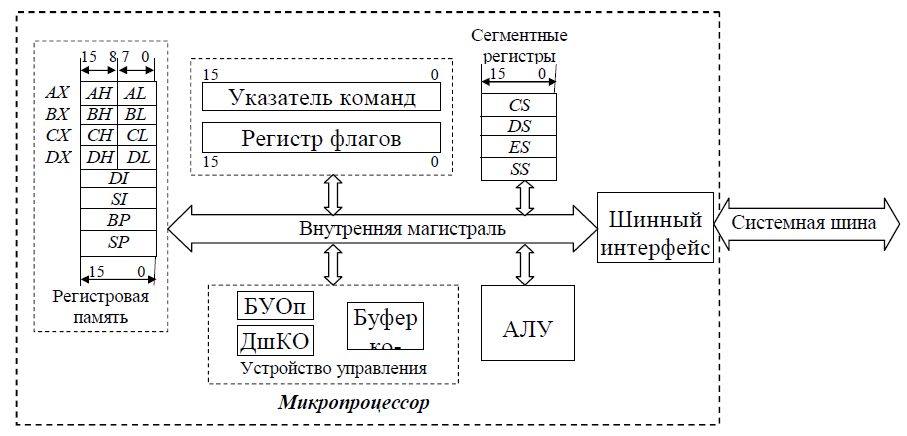

Структура микропроцессора 8086, состав и назначение его основных блоков.

АЛУ – выполнение арифметических и логических операций.

РП, состоящая из 8 16-разрядных регистров. 4 допускают раздельное использование младших и старших разрядов.

УУ, включающее в себя:

-Буфер команд, представляющий собой регистровую память объемом 6 байт, предназначенную для хранения выполняемой в данный момент команды (аналогично РК в классической ЭВМ) и заполняемую очередными командами из ОП по мере освобождения.

-Дешифратор кода операций, определяющий тип команды

-Блок управления операциями, который на основе расшифрованного дешифратором кода операции формирует управляющие сигналы, организующие работу всех блоков МП

Указатель команд (IP – instruction pointer), определяющий адрес выполняемой команды в сегменте ОП.

Регистр флагов, содержащий признаки результата выполняемых команд и некоторую управляющую информацию.

Признаки результата:

ZF – флаг 0 (1 при нулевом результате)

SF – флаг знака (устанавливается равным старшему биту результата)

CF – флаг переноса (фиксирует факт переноса из старшего бита в арифметических операциях)

OF – флаг переполнения (1 при результате вне допустимого диапазона)

PF – флаг паритета (1 если младшие 8 бит результата содержат четное кол-во 1)

Флаги управления:

IF – разрешение прерывания (при 1 МП распознает маскируемые прерывания)

DF – флаг направления (используется в командах обработки последовательности байт в памяти. 0 – от младшего адреса к старшему, 1 – наоборот)

TF – флаг трассировки (используется при отладке. 1 - после выполнения каждой команды генерируется внутреннее прерывание, позволяющее перейти к соответствующей подпрограмме)

Блок сегментных регистров, состоящий из 16-разрядных регистров, каждый из которых содержит старшие разряды базового (начального) адреса сегмента ОП, выделяемого программе при ее выполнении:

CS – кодовый сегмент

DS – сегмент данных

SS – сегмент стека

ES – дополнительный сегмент данных

Шинный интерфейс содержит схемы, обеспечивающие связь внутренней магистрали МП и системной шиной.