- •Задачи статистического и динамического анализа сау

- •Классификация объектов тепловой энергетики по параметру регулирования и их математическое описание.

- •Общий вид экспериментальных переходных кривых теплоэнергетических процессов. Обобщенная энергетическая форма уравнений динамики регулируемых объектов.

- •Понятие и основные сведения об алгоритме. Способы записи алгоритмов

- •Схемы и основные структуры алгоритмов

- •Декомпозиция алгоритмов управления и сбора информации в технологической системе.

- •Классификация процессов функционирования энергоблока аэс. Типовые алгоритмы управления

- •Типовые алгоритмы регулирования, типовые регуляторы и их динамические характеристики

- •Структурная схема унифицированного регулятора сцар.

- •Выбор схем регулирования типовых теплоэнергетических процессов и методы настройки типовых регуляторов.

- •Структура формирования технологического цикла. Общая последовательность

- •Комбинационные детерминированные модели технологического цикла.

- •Последовательностные детерминированные модели технологического

- •Комбинационные и последовательностные автоматы. Структура

- •Основные логические функции. Реализация основных логических функций на релейно-контактных схемах.

- •Основные логические элементы и их функции. Функционально полный набор логических элементов.

- •Минимизация логических функций методом матриц Карно.

- •Виды запоминающих устройств. Триггеры. Регистры.

- •Структура и принципы построения эвм.

- •Классификация эвм по сфере применения.

- •Структура и основные функции увм. Иерархическая структура асу тп.

- •Структура и функции традиционных асу тп аэс.

- •Структура и функции увс "Комплекс-Титан 2"

- •Основные недостатки традиционных асу аэс.

- •Обобщённая структура и функции информационно-управляющей

- •Человеко-машинный интерфейс (чми), реализованный в свбу асу тп аэс

- •Система регулирования мощности реактора. Режимы работы. Структура и

- •Центробежный регулятор частоты вращения турбины. Назначение,

- •Система регулирования уровня в парогенераторе.

- •Способы регулирования давления пара перед турбиной.

Минимизация логических функций методом матриц Карно.

Метод матриц Карно (диаграмм Вейча) облегчает процедуру склеивания благодаря тому, что члены СДНФ или СКНФ (совершенные дезьюктивные или конъюктивные формы) (полные конъюнкции или полные дизъюнкции) размещаются на плоскости таким образом, что соседние члены, для которых возможно склеивание, оказываются в непосредственной близости друг от друга.

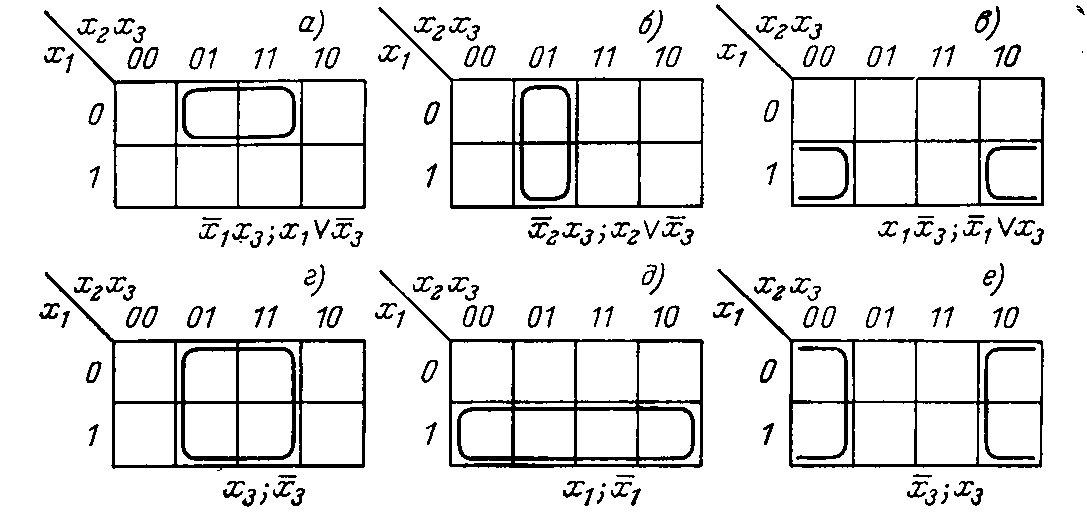

Примеры матриц Карно приведены на рис. 3-2. Каждая клетка матрицы соответствует одной комбинации значений входных переменных. Код этих комбинаций подобран так, чтобы соседние клетки отличались значениями только одной переменной, т. е. чтобы им соответствовали соседние выражения (код Грея). В построенную на основе этого кода таблицу вписываются символы, соответствующие значениям функции на определенных наборах входных переменных. Процедура облегчается, если функция задана десятичными индексами входных наборов. Такие матрицы, заполненные десятичными числами, представлены на рис. 3-2.

Рис. 3-3.. Примеры объединения и результаты склеивания в матрицах для трех переменных.

Если в двух соседних клетках заполненной матрицы Карно находятся одинаковые символы (0 или 1), то соответствующие этим клеткам выражения можно склеить, что равносильно устранению переменной, которая в рамках склеиваемой группы меняет значение. Соседние клетки матрицы, образующие пары, объединяются замкнутой линией для обозначения возможности склеивания.

Итак, одинаковые символы, охваченные контуром, можно представить конъюнкцией (если эти символы суть единицы) или дизъюнкцией (если эти символы нули), в которые входят только переменные, не меняющиеся в пределах этого контура. На рис. 3-3 под соответствующими матрицами приведены результаты склеивания, причем на первом месте даны выражения, представляющие группу единиц, а через точку с запятой — выражения, представляющие группу нулей.

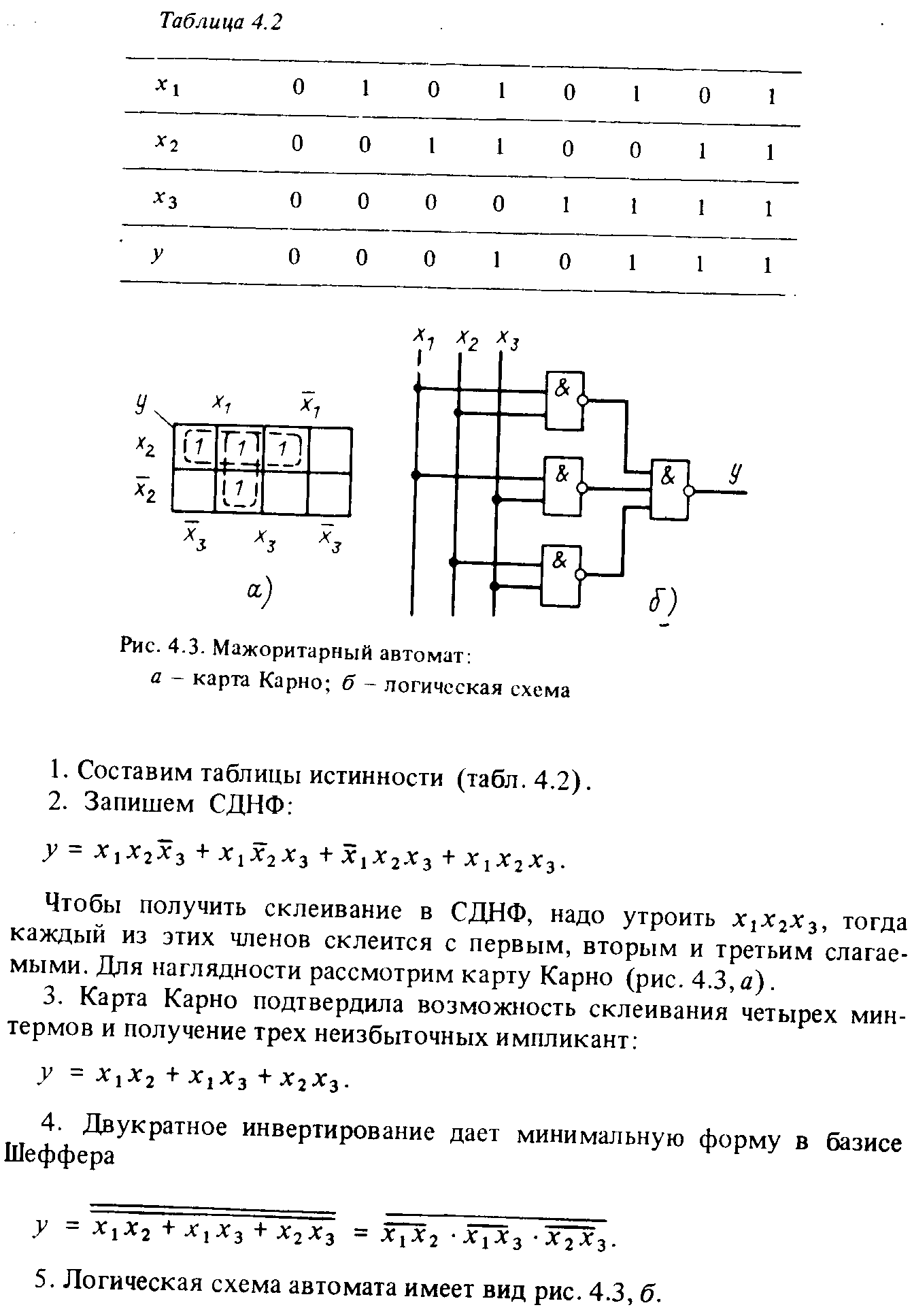

Пример 4.2. Разработать автомат, реагирующий не менее чем на два сигнала из трех (мажоритарный автомат).

Виды запоминающих устройств. Триггеры. Регистры.

Виды запоминающих устройств:

По своему назначению ЗУ подразделяются на два класса:

Постоянные

ПЗУ предназначены для длительного хранения информации, потому их основным качеством является энергонезависимость, т.е. способность длительное время сохранять записанную информацию после отключения электропитания.

По своей конструкции ПЗУ подразделяются на магнитомеханические и электронные.

а) Магнитомеханические ПЗУ — это жесткие магнитные и гибкие дискеты. Информация записывается на их дорожках в виде последовательности намагниченных и ненамагниченных участков в двоичном коде (намагниченный участок — это 1, а ненамагниченный — это 0). Магнитомеханические ПЗУ энергонезависимы и надежны, допускают перезапись информации, но их быстродействие ограничено скоростью вращения дисков. Они удобны для употребления в тех случаях, когда перезапись информации и обращение за информацией к ЗУ происходит относительно редко, как это бывает, например, при записи массива УП в памяти УЧПУ.

б) Электронные ПЗУ, в том числе перепрограммируемые (ППЗУ), выполняются на базе больших интегральных схем (БИС). Они обладают большей скоростью обмена информацией и используются для формирования в УВМ системного программного обеспечения (см. подразд. 6.1), а ППЗУ используются также для записи УП. Однако электронные ПЗУ имеют меньшую информационную емкость и низкую транспортабельность.

Оперативные.

Оперативные ЗУ предназначены для скоростной обработки текущей (оперативной) информации. Эта информация не предназначена для длительного хранения, но должна быть обработана достаточно быстро, чтобы обеспечить управление быстродействующими исполнительными механизмами, электроприводами. Выполняются ОЗУ на энергозависимых БИС, но позволяют обрабатывать информацию с тактовой частотой в десятки и сотни мегагерц.

Основой БИС ОЗУ являются триггерные ячейки, выполненные на электронных элементах с двумя устойчивыми состояниями триггеров.

Триггеры.

Триггер – это стандартная ячейка ОЗУ для хранения информации с емкостью 1 бит. Триггер – логический элемент, обладающий двумя устойчивыми состояниями.

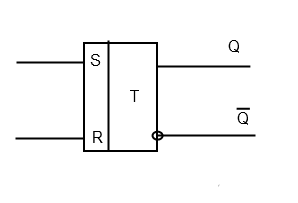

RS-триггер.

П ростейшей

триггерной ячейкой является асинхронный

RS-триггер.

Это ячейка с двумя входами (R

и

S)

и

двумя выходами: прямым выходом Q

и

инверсным выходом Q.

По

сигналу S

=

1 (Set

—

установка) RS

-триггер устанавливается в единичное

состояние, которому соответствует Q

=

1 и

ростейшей

триггерной ячейкой является асинхронный

RS-триггер.

Это ячейка с двумя входами (R

и

S)

и

двумя выходами: прямым выходом Q

и

инверсным выходом Q.

По

сигналу S

=

1 (Set

—

установка) RS

-триггер устанавливается в единичное

состояние, которому соответствует Q

=

1 и ![]() =

0. По сигналу R

= 1

(Reset

— сброс)

RS

-триггер сбрасывается в нулевое состояние,

которому соответствует Q

= 0

и

=

1. Когда на одном из входов RS

триггера имеется единичный сигнал, на

другой вход должен быть подан нулевой

сигнал.

=

0. По сигналу R

= 1

(Reset

— сброс)

RS

-триггер сбрасывается в нулевое состояние,

которому соответствует Q

= 0

и

=

1. Когда на одном из входов RS

триггера имеется единичный сигнал, на

другой вход должен быть подан нулевой

сигнал.

Одновременная подача единичных сигналов на оба входа RS-триггера не допускается.

При наличии на обоих входах RS -триггера нулевых сигналов его состояние не изменяется.

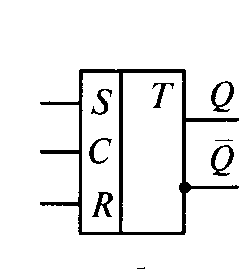

Синхронный RS-триггер.

Синхронный триггер переключается только при одновременной подаче единичных сигналов на один из информационных входов и на вход С (Clock).

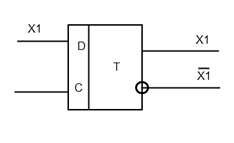

D – триггер. (Delay — задержка).

Состояние D-триггера принимает то значение, которое имеется на входе D: при D = 1 получим Q= 1, а при D= 0 получим Q = 0, но только при условии, что С= 1. При С= 0 состояние выходов D -триггера не изменяется. Это свойство Д-триггера можно использовать для организации считывания информации со входов управляющего устройства.

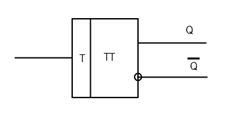

Счетный триггер (Т- триггер)

У Т

-триггера имеется только один

информационный (счетный) вход Т,

который

совпадает с тактовым входом С. После

прохождения единичного импульса на

счетном входе Т

состояние триггера изменяется на

противоположное.

Т

-триггера имеется только один

информационный (счетный) вход Т,

который

совпадает с тактовым входом С. После

прохождения единичного импульса на

счетном входе Т

состояние триггера изменяется на

противоположное.

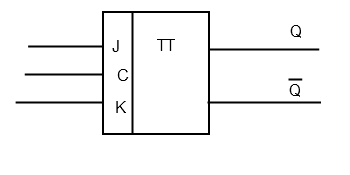

J К- триггер.

У ниверсальность

J

К

-триггера заключается в том, что при

подаче входных сигналов J

=

1 или К=

1

раздельно он работает, как RS

-триггер. Если же на вход К

подавать инвертированный сигнал с входа

J

,

то получится D

-триггер. А

при

подаче J

= К= 1

одновременно он работает, как

Т

-триггер.

ниверсальность

J

К

-триггера заключается в том, что при

подаче входных сигналов J

=

1 или К=

1

раздельно он работает, как RS

-триггер. Если же на вход К

подавать инвертированный сигнал с входа

J

,

то получится D

-триггер. А

при

подаче J

= К= 1

одновременно он работает, как

Т

-триггер.

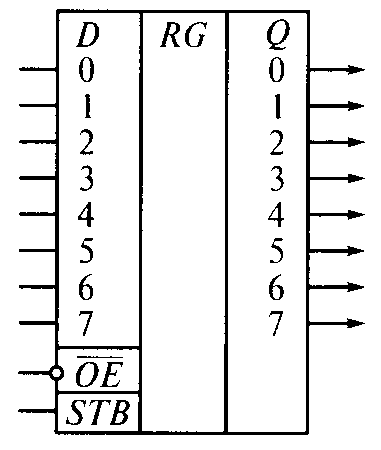

Регистры.

Триггеры, используемые в ОЗУ, применяются не по одному, а группами, называемыми регистрами.

Регистр — это электронное устройство, базирующееся на совокупности триггерных ячеек и предназначенное для хранения и преобразования помещенной в него информации, записанной в двоичном коде.

По характеру выполняемых операций регистры принято подразделять на регистры хранения, регистры сдвига и счетные регистры (счетчики).

Р

егистры

хранения

реализуют

только одну, общую для регистров

всех типов, функцию хранения информации

в двоичном коде. Типичные регистры

хранения строятся на D-триггерах.

Примером простейшего регистра хранения

является совокупность D-триггеров

в схеме, приведенной на рис. 5.12.

егистры

хранения

реализуют

только одну, общую для регистров

всех типов, функцию хранения информации

в двоичном коде. Типичные регистры

хранения строятся на D-триггерах.

Примером простейшего регистра хранения

является совокупность D-триггеров

в схеме, приведенной на рис. 5.12.

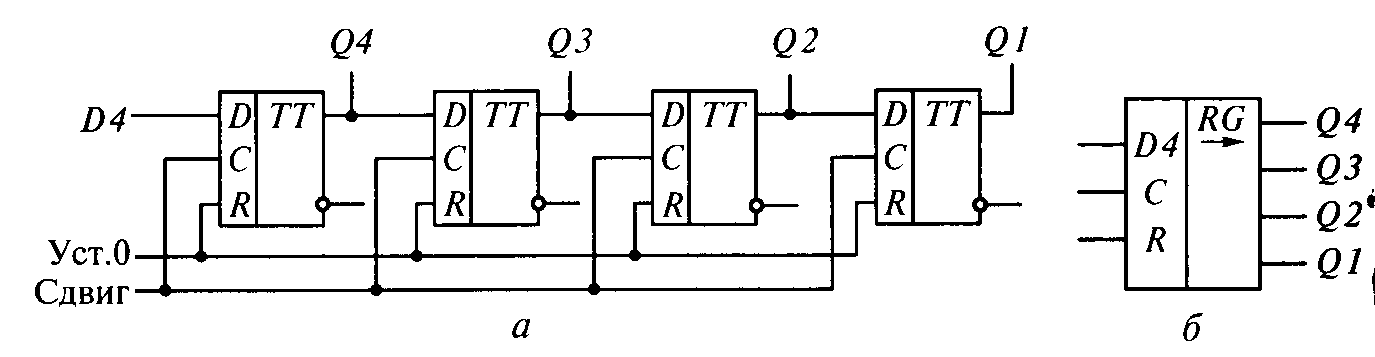

Рис. 5.14. Регистр хранения RG, построенный на D-триггерах:

а — условное обозначение;

Регистры сдвига помимо приема, хранения и выдачи информации подобно регистрам хранения позволяют сдвигать записанную информацию, т.е. перемещать значения записанных битов информации от одной триггерной ячейки к другой, соседней, причем сдвиг информации производится одновременно во всех ячейках в одном направлении. Информация в такой регистр может поступать как в последовательном, так и в параллельном коде, а сдвиг информации производится подачей единичного импульса на вход сдвига. Вход сдвига организуется путем объединения всех тактовых входов регистра.

Рис. 5.15. Схема регистра сдвига (а) и его условное обозначение (б)

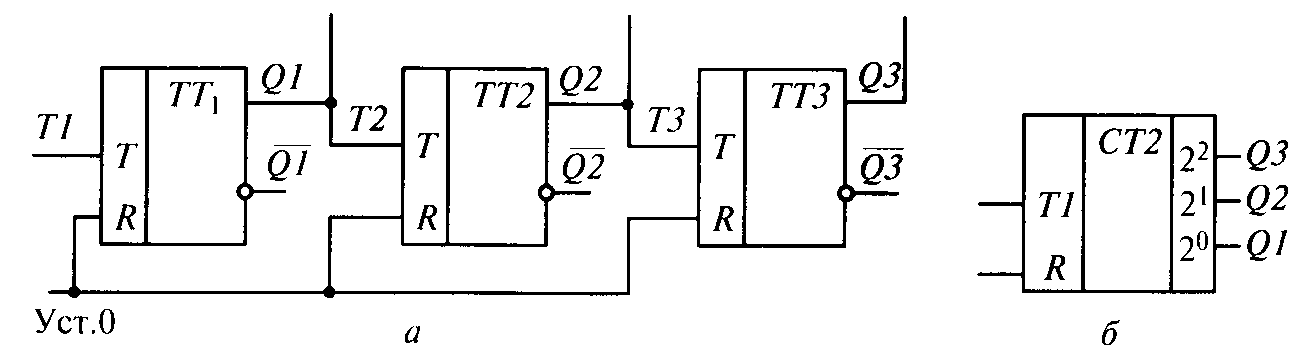

Счетные регистры, или счетчики, отличаются тем, что помимо функций записи, хранения и выдачи информации выполняют функцию счета поступающих на них импульсов с запоминанием результатов.

Рис. 5.16. Схема трехразрядного двоичного счетчика (а) и его условное обозначение (б)