- •14. Прерывания микроконтроллера hc908gp32. Маскирование прерываний. Распознавание и обработка прерываний

- •21. Структура, назначение таймерного модуля tim08 микроконтроллера hc908gp32.

- •22. Режимы работы таймерного модуля tim08 микроконтроллера hc908gp32. Режим захвата.

- •23. Режимы работы таймерного модуля tim08 микроконтроллера hc908gp32. Режим сравнения/совпадения

- •2. Порты ввода/вывода

21. Структура, назначение таймерного модуля tim08 микроконтроллера hc908gp32.

22. Режимы работы таймерного модуля tim08 микроконтроллера hc908gp32. Режим захвата.

23. Режимы работы таймерного модуля tim08 микроконтроллера hc908gp32. Режим сравнения/совпадения

. ПРОЦЕССОР СОБЫТИЙ TIM08

Модуль TIM08, хотя и носит дословное название «модуль таймерного интерфейса», по сути, является одним из лучших процессоров событий в 8-разрядных МК.

Модуль TIM08 состоит из 16-разрядного таймера-счетчика и некоторого количества связанных с ним полностью идентичных каналов захвата/сравнения. Каждый из каналов в процессе инициализации может быть настроен на один из пяти режимов работы:

входного захвата;

небуферированного выходного сравнения;

буферированного выходного сравнения;

небуферированной широтно-импульсной модуляции (ШИМ);

буферированной ШИМ.

Каждый канал захвата/сравнения связан с одним из выводов МК. Функция входного или выходного сигнала модуля процессора событий является альтернативной функцией линий порта Port D. МК MC68HC908GP32 имеет в своем составе два модуля процессора событий - TIM1 и TIM2. Каждый из модулей имеет по два канала захвата/сравнения.

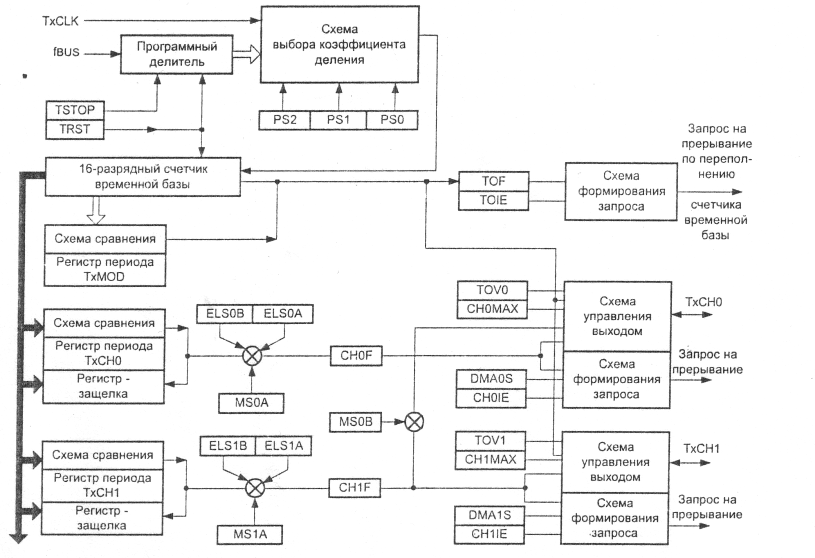

Структурная схема модуля двухканального процессора событий представлена на рис. 3.1. Шестнадцатиразрядный таймер-счетчик служит временной базой для модулей захвата/сравнения. Он подсчитывает импульсы тактовой частоты, поступающие на его вход. Все интервалы времени, которые генерируются или измеряются МК, измеряются числом периодов этой тактовой частоты.

В общем случае (модули TIM08 других МК семейства НС08) таймер-счетчик имеет два источника тактирования:

внутренний генератор, выполненный на основе программируемого делителя час тоты шины МК fBUS;

внешний генератор, подключаемый к выводу TxCLK МК.

Выбор между внутренним и внешним генераторами, а также выбор коэффициента деления программируемого делителя частоты шины КТ|Мх определяется комбинацией битов PS2 - PS0 регистра управления таймера-счетчика TxSC. Коэффициент деления КТ|Мх может принимать семь различных значений: 1, 2, 4, 8, 16, 32, 64. Максимальная частота сигнала внешнего генератора, подключаемого ко входу TxCLK, составляет 4 МГц при условии, что МК работает на предельной частоте внутренней шины fBUS- 8 МГц. Процессоры событий TIM! и TIM2 в составе МК MC68HC908GP32 не имеют выводов T1CLK и T2CLK в перечне выводов корпуса и, следовательно, могут использовать для тактирования только встроенный генератор.

Таймер-счетчик временной базы допускает программную установку периода работы. Если не предпринимать специальных действий при инициализации процессора событий, то коэффициент счета счетчика временной базы будет равен 216, т. е. счетчик проходит полный цикл от начального состояния кода $0000 до конечного состояния кода SFFFF. Если таймер-счетчик находится в состоянии $FFFF, то при поступлении на его вход очередного тактового импульса наступает переполнение таймера-счетчика. Счетчик переходит в состояние $0000, одновременно устанавливается флаг переполнения TOF. Переполнение счетчика не оказывает влияния на его работу: при поступлении следующих тактовых импульсов код в счетчике продолжает нарастать. Коэффициент счета таймера-счетчика может быть изменен посредством записи кода желаемого Ксч в двухбайтовый регистр периода TxMOD (TxMODH и TxMODL - старший и младший байты этого регистра, х - номер таймерного модуля, для TIM1 х = 1, для TIM2 х = 2). Вход сброса счетчика подключен к выходу цифрового компаратора (см. рис. 3.1), на один из входов которого поступает код текущего состояния таймера-счетчика, а на другой - код Ксч, записанный в регистре TxMOD. Если эти коды равны, то при поступлении следующего тактового импульса счетчик сбрасывается в «О», и флаг переполнения TOF устанавливается в «1». Диапазон допустимых значений Ксч составляет от 1 до (21б-1). Таким образом, дискретность регулирования периода таймера-счетчика, который в режиме ШИМ образует период ШИМ-сигнала, составляет 16 бит.

Предусмотрена возможность пуска и останова таймера-счетчика под управлением программы (бит TSTOP в регистре управления таймером-счетчиком TxSC). Кроме того, счетчик и программируемый делитель частоты могут быть одновременно сброшены посредством установки в «1» бита TRST в регистре TxSC. При этом все триггеры таймера-счетчика установятся в «О», а программируемый делитель частоты будет настроен на режим единичного коэффициента деления частоты внутренней шины МК. Заметьте, что бит TRST не останавливает работу таймера-счетчика, с приходом очередного тактового импульса состояние счетчика станет равным $0001. Сброс таймера-счетчика рекомендуется проводить в следующем порядке:

остановите таймер-счетчик (бит TSOP = 1);

выполните операцию сброса таймера-счетчика (бит TRST = 1);

переинициализируйте биты PS2-PS0 регистра TxSC, которые определяют источник и частоту тактирования;

разрешите счет таймера-счетчика.

Код таймера-счетчика в процессе счета может быть считан прикладной программой при обращении к регистрам текущего кода TxCNTH и TxCNTL. При обращении к регистру старшего байта код таймера-счетчика автоматически копируется в указанную регистровую пару. Поэтому, несмотря на то, что операции чтения старшего и младшего байтов разнесены во времени, вы прочитаете состояние таймера-счетчика в момент обращения к регистру старшего байта TxCNTH. Такое решение предотвращает получение ложной информации в случае, если частота тактирования таймера-счетчика высока, и по этой причине в моменты обращения к регистрам TxCNTH и TxCNTL состояния счетчика различаются. Однако нельзя допускать ситуацию, при которой после прочтения старшего байта младший прочитан не будет. Повторное чтение старшего байта не сопровождается защелкиванием текущего кода таймера-счетчика в регистрах TxCNTH и TxCNTL.

При переполнении таймера-счетчика устанавливается флаг переполнения TOF в регистре управления TxSC (таб. 3.1) и генерируется запрос на прерывание, если бит разрешения прерывания TOIE установлен в «1», т. е. прерывания по переполнению таймера-счетчика разрешены.

Для управления таймером-счетчиком модуля TIM08 предусмотрены пять регистров специальных функций:

TxSC - регистр управления таймером-счетчиком «х», где «х» - имя модуля процессора событий МК (для TIM1 х=1, для TIM2 х=2 );

TxMODH - регистр периода таймера-счетчика (старший байт );

TxMODL - регистр периода таймера-счетчика (младший байт);

TxCNTH - регистр текущего значения таймера-счетчика (старший байт);

TxCNTL - регистр текущего значения таймера-счетчика (младший байт).

. Структурная схема процессора событии ТIМ08 МК MC68H0908GP32

Каждый канал захвата/сравнения в составе процессора событии связан с одним выводом МК (см. рис. 3.1). Вывод обозначают TxCHi, где i – порядковый номер канала захвата/ сравнения в составе процессора событии х. Например, T1СНО – вывод канала 0 процессoра событий ТIМ1. В режиме захвата аппаратные средства канала захвата/сравнения фиксируют моменты времени, когда логический сигнал на входе TxCHiК изменяет свое состояние. В режимах выходного сравнения и широтно-импульсной модуляции (ШИМ) канал захвата/сравнения формирует импульсный сигнал с заданными временными параметрами на выходе TxCHi. Направление передачи сигнала по линии TxCHi (вход или выход) определяется инициализацией каналов захвата/сравнения на тот или иной режим. Несмотря на то, что работа линии ТхСНi в составе процессора coбытий является альтернативной функцией линии одного из портов ввода/вывода МК, состояние регистра направления передачи порта DDRx в этом случае значения не имеет.

Программно-логическая модель каждого канала захвата/сравнения включает три регистра: 16-разрядный регистр данных канала i (TxCHiH и TxCHiL – старший и младший байты этого регистра) и регистр управления каналом i – ТХSС1. Функция регистра данных определяется режимом работы канала захвата/сравнения, регистр управления TxSCi служит для выбора этого режима и для обслуживания прерываний по запросам модуля

захвата/сравнения.

В режиме входного захвата аппаратные средства модуля следят за уровнем сигнала на входе TxCHi микроконтроллера (рис. 3.2).

При изменении уровня логического сигнала с «0» на «1» или наоборот вырабатывается строб записи, и текущее состояние таймера-счетчика временной базы копируется в 16-разрядный регистр данных TxCHi. канала захвата/сравнения. Событие захвата отмечается установкой в п1» флага CHiF в регистре управления каналом с номером i. Этот флаг может быть считан программно, а если прерывания по событию канала i разрешены (флаг СНi1Е в регистре управления установлен), то модуль процессора событий выставляет запрос на прерывание. Предусмотрены три типа изменения сигнала на входе TxCHi МК, которые воспринимаются модулем захвата/сравнения, как событие захвата:

1)передний (нарастающий) фронт сигнала;

2)задний (падающий) фронт сигнала;

3)любое изменение логического уровня сигнала.

Выбор типа события захвата для модуля определяется битами ELSiB:ELSiA регистра

управления каналом TxSCi.

В режиме выходного сравнения аппаратные средства модуля непрерывно сравнивают изменяющийся во времени код таймера-счетчика с кодом, который записан в 16-раз-рядный регистр данных TxCHi модуля захвата/сравнения i (рис. 3.3).

В момент равенства кодов аппаратные средства модуля устанавливают на выходе микроконтроллера TxCHi заданный уровень логического сигнала либо изменяют этот уровень на противоположный. При наступлении события выходного сравнения в регистре управления канала TxSCi устанавливается в «1» флаг CHiF, тот же, что и при настyплении события захвата. Аналогично предыдущему случаю этот флаг вызывает формирование запроса на прерывание, если прерывания от модуля i разрешены. Предусмотрены три типа изменения сигнала на выходе TxCHi МК в момент события выходного

сравнения:

1)инвертирование сигнала на выходе;

2)установка низкого логического уровня;

3)установка высокого уровня.

Выбор типа изменения выходного сигнала для модуля определяется битами ELSiB:ELSiA регистра управления каналом TxSCi

20. Организация ввода/вывода в микроконтроллере HC908GP32.